## Multi-formalism in Different Levels of Abstraction for Requirements Engineering and Architectural Design of Real-Time Embedded Systems

Fabíola Gonçalves Coelho Ribeiro

Federal University of Uberlândia Faculty of Computing Posgraduate Program in Computer Science

> Uberlândia 2019

#### Fabíola Gonçalves Coelho Ribeiro

### Multi-formalism in Different Levels of Abstraction for Requirements Engineering and Architectural Design of Real-Time Embedded Systems

Ph.D. Thesis presented to the Posgraduate Program of the Computer Faculty of Uberlândia Federal University and of the Carl von Ossietzky Universität Oldenburg as a part of the requirements for obtaining the title of Doctor in Computer Science.

Concentration Area: Computer Science

Supervisor: Dr. Michel S. Soares Co-Supervisor: Dr. Carlos Eduardo Pereira Adviser: Dr. Achim Rettberg

|              | Ficha Catalográfica Online do Sistema de Bibliotecas da UFU com dados informados pelo(a) próprio(a) autor(a).                                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R484<br>2019 | Ribeiro, Fabíola Gonçalves Coelho, 1985-<br>Multi-formalism in Different Levels of Abstration for<br>Requirements Engineering and Architectural Design of Real-Time<br>Embedded Systems [recurso eletrônico] / Fabíola Gonçalves<br>Coelho Ribeiro 2019.                                                                               |

|              | Orientador: Michel dos Santos Soares .<br>Coorientador: Carlos Eduardo Pereira.<br>Coorientador: Achim Rettberg.<br>Tese (Doutorado) - Universidade Federal de Uberlândia, Pós-<br>graduação em Ciência da Computação.<br>Modo de acesso: Internet.<br>Disponível em: http://doi.org/10.14393/ufu.te.2019.2608<br>Inclui bibliografia. |

|              | 1. Computação. I., Michel dos Santos Soares,1978-, (Orient.). II.<br>Pereira, Carlos Eduardo,1965-, (Coorient.). III. Rettberg, Achim,<br>1966-, (Coorient.). IV. Universidade Federal de Uberlândia. Pós-<br>graduação em Ciência da Computação. V. Título.                                                                           |

|              | CDU: 681.3                                                                                                                                                                                                                                                                                                                             |

|              | Bibliotecários responsáveis pela estrutura de acordo com o AACR2:<br>Gizele Cristine Nunes do Couto - CRB6/2091                                                                                                                                                                                                                        |

Nelson Marcos Ferreira - CRB6/3074

SEI/UFU - 1569683 - Ata de Defesa - Pós-Graduação

https://www.sei.ufu.br/sei/controlador.php?acao=documento\_imprimir\_web&acao\_origem=arvore\_vi...

UNIVERSIDADE FEDERAL DE UBERLÂNDIA

Coordenação do Programa de Pós-Graduação em Ciência da Computação Av. João Naves de Ávila, nº 2121, Bloco 1A, Sala 243 - Bairro Santa Mônica, Uberlândia-MG, CEP 38400-902 Telefone: (34) 3239-4470 - www.ppgco.facom.ufu.br - cpgfacom@ufu.br

#### ATA DE DEFESA - PÓS-GRADUAÇÃO

| Programa de Pós-<br>Graduação em:     | Ciência da Computação                        |                         |                     |                                |         |

|---------------------------------------|----------------------------------------------|-------------------------|---------------------|--------------------------------|---------|

| Defesa de:                            | Tese, 16/2019, PPGCO                         |                         |                     |                                |         |

| Data:                                 | 3 de setembro de 2019                        | Hora de início:         | 14:02               | Hora de encerramento:          | 15:58   |

| Matrícula do Discente:                | 11423CCP010                                  |                         |                     |                                |         |

| Nome do Discente:                     | Fabíola Gonçalves Coelho Ribeiro             |                         |                     |                                |         |

| Título do Trabalho:                   | Multi-formalism in Di erent Levels of Abstra | action for Requirements | Engineering and Des | sign of Real-Time and Embedded | Systems |

| Área de concentração:                 | Ciência da Computação                        |                         |                     |                                |         |

| Linha de pesquisa:                    | Engenharia de Software                       |                         |                     |                                |         |

| Projeto de Pesquisa de<br>vinculação: | -                                            |                         |                     |                                |         |

Reuniu-se na Sala F02, na Escherweg 2, 26121 Oldenburg, Alemanha, a Banca Examinadora, designada pelo Colegiado do Programa de Pósgraduação em Ciência da Computação, assim composta: Professores Doutores: Flávio de Oliveira Silva - FACOM/UFU, Stéphane Julia - FACOM/UFU, Martin Fränzle - University of Oldenburg, Jürgen Sauer - University of Oldenburg, Carlos Eduardo Pereira - UFRGS (Coorientador) e Michel dos Santos Soares - UFS, orientador da candidata.

Iniciando os trabalhos o presidente da mesa, Prof. Dr. Michel dos Santos Soares, apresentou a Comissão Examinadora e a candidata, agradeceu a presença do público, e concedeu à Discente a palavra para a exposição do seu trabalho. A duração da apresentação da Discente e o tempo de arguição e resposta foram conforme as normas do Programa.

A seguir o senhor presidente concedeu a palavra, pela ordem sucessivamente , aos examinadores, que passaram a arguir a candidata. Ultimada a arguição, que se desenvolveu dentro dos termos regimentais, a Banca, em sessão secreta, atribuiu o resultado nal, considerando a candidata:

Aprovada.

1 of 2

08/09/2020 15:10

SEI/UFU - 1569683 - Ata de Defesa - Pós-Graduação

https://www.sei.ufu.br/sei/controlador.php?acao=documento\_imprimir\_web&acao\_origem=arvore\_vi...

Esta defesa faz parte dos requisitos necessários à obtenção do título de Doutor.

Ressalta-se que os examinadores Martin Fränzle e Jügen Sauer por serem estrangeiros, residentes em outro país e não possuírem CPF registrado no Brasil não podem assinar a ata de defesa.

Defesa realizada de acordo com convênio de dupla titulação entre a Universidade Federal de Uberlândia e a Carl von Ossietzky Oldenburg, processo 23117.076440/2018-63.

O competente diploma será expedido após cumprimento dos demais requisitos, conforme as normas do Programa, a legislação pertinente e a regulamentação interna da UFU.

Nada mais havendo a tratar foram encerrados os trabalhos. Foi lavrada a presente ata que após lida e achada conforme foi assinada pela Banca Examinadora.

Referência: Processo nº 23117.084804/2019-60

SEI nº 1569683

I dedicate this research to Luzia Gonçalves, my mother, and to Maria Fernanda, my daughter.

## Acknowledgements

The initial desire for accomplishing this research grew from a family dream. A dream that was not mine, but one that came to sculpture and be the sculptor of the person I would become. In all certainty, looking back over my expectations some four years ago, I never imagined that study and qualification would fuse into my persona in such a dignifying manner. The student, professor, researcher and the very human being of four years ago are no longer the same.

The contributions presented in this thesis are the result of four years of dedication, resilience and love for research. Indeed, it also comes from the help, support, comprehension, dedication and fidelity of the innumerous individuals involved. To my almighty Lord, thank you for giving me health and strength to continue and for supporting me throughout.

I was fortunate to have the privilege of counting on the contribution of three supervisors who supported me at different and specific moments over my research, while delivering excellent tuition in our meetings and lectures; they also provided life based examples. Therefore, I would like to thank in advance the Professors Dr. Achim Rettberg, Dr. Carlos Pereira and Dr. Michel Soares for their immeasurable and constant support. My personal development, without doubt, was greatly incremented through such support and experiences. I profoundly hope that someday, I too may pass onto my students a little of what you were to me.

Prof. Achim Rettberg, you received me in your research group gave me support advised and guided me through my double PhD. Prof. Achim, you are an example of a skilled, qualified and caring person that provides personalized attention to students. Thank you so much for your comprehension, contribution to my research topic, the help provided in achieving the attained results, and especially to your immense dedication while making the final corrections to my thesis. I would like also to express gratitude for the several developmental and learning capacity opportunities that exceed those of a doctoral student's curriculum. Prof. Carlos Pereira, I still remember well our first personal contact. You have shown me that despite the numerous commitments and responsibilities, you have always been sensitive to the demands of your students. Professor Carlos, you have an incredible subtlety and intelligence in each assessment, evaluation and supervision. Furthermore, it is admirable the manner in which you share your knowledge and experiences. All of these factors were primordial to my personal and professional development. Therefore, I sincerely wish to thank you for all the support and many life enhancing lessons I received.

Prof. Michel Soares, we have worked together since my master studies, from that time until now nine years have passed! Michel, what you have done and still do for your students is much more that provide technical and professional supervision: you have established a teaching based on examples. I will never be able to compensate the time you spent with me. We can recount several weekends working together, tight deadlines and many papers/thesis analyses. Moreover, there were, I recall "tellings-off" and even in situations where I was agitated and felt anxious, you would always tell me: "calm down, everything will be all right!" Thank you Michel for your belief in my ability and always guiding me on to the better path.

I wish also to thank my Family. Each and every member, close or distant, has helped me in distinct ways: encouraged, cared, prayed, wept and laughed with me. I will always be thankful. You cannot imagine how much you are important to me! I would like to give special thanks to Geovanna Gonçalves and Maria Rita Bernardes, my dear sisters, to my dear cousins Gleyce Kelle Bernardes and Américo Gonçalves, to my aunts Amélia Gonçalves, Nívea Rodrigues and Juvenília Gonçalves and to my uncles João Batista Gonçalves and Carlos Gonçalves.

I would like to thank, with all my heart, my friends Dayse de Oliveira, Kênia Santos, Clénia Rios, and Renata de Oliveira. Thank you for always being here for me, for rejoicing in my achievements and encouraging me to do better every day.

Marcos Bhering, you have been "walking by me" for so much longer! You have been benevolent, friendly, kind and supportive at all times over the completion of my thesis. Thank you so much for your comforting words and care, for the many hours dedicated to improving the text and specially, for the love and affection with which you always helped me.

My thanks also go to IF-Goiano for having allowed for my exclusive dedication to Ph.D. research. I am grateful to the institution, my colleagues and the management team for their support and encouragement.

Thanks to CAPES for the financial support during my sandwich Ph.D. studies in Germany.

I would like to thank the Carl von Ossietzky University Oldenburg and the University of Applied Sciences Hamm/Lippstadt for the support provided that aided in the accomplishment of my Ph.D. studies. Considering the period I lived in Germany, all the enriching experiences I have had and the lessons learned, I would like to express my gratitude to André Faria, Charles Steinmetz, Cíntia Faria, Edenilda Brachtendorf, Filiz Polat, Renata Lutkehaus and Vincent Marnier. Thank you for dedicating your time, care, friendship and words of encouragement and support over the points of this journey.

Finally, I want to thank my mother, Luzia de Fátima Gonçalves, and my daughter, Maria Fernanda Gonçalves. You are the ones who deserve all the honors and are to whom I dedicate all the results and jubilation that come from this research. I know how hard this period was for you both: many absences, relinquishment, days without dialogue and several "rainy days". Thanks for the true friendship, your support and unconditional love. My dearest of friends, you have lived and supported my dream. I could never have done all this without you, I love you infinitely.

"Porque não há nada mais belo que o amor." (Marcos Jungmann Bhering)

#### Resumo

Os Sistemas de Tempo Real e Embarcados (STRE) têm se tornado cada vez mais onipresentes nas atividades humanas. O grau de confiabilidade e de corretude com que estes sistemas são desenvolvidos têm um decisivo impacto em sua futura operação. Sendo assim, o sucesso no desenvolvimento destes sistemas está relacionado não apenas com a sua correta execução computacional, mas também com a confiabilidade em que as restrições de tempo real e embarcadas são atendidas. A engenharia de requisitos e o projeto arquitetural constituem importantes atividades do desenvolvimento dos STRE, pois lidam com domínios complexos e diversificados como software, hardware, mecânico, eletrônico e o ambiente físico. Dentro do domínio dos STRE, a engenharia de requisitos e o projeto arquitetural devem atender aos requisitos funcionais e embarcados e aos respectivos requisitos não funcionais. Além disto, o design destes sistemas deve considerar as propriedades de custo, qualidade, confiabilidade e segurança. Este estudo relaciona-se ao desenvolvimento e análise de uma metodologia que abrange diferentes fases de projeto de STRE. A presente pesquisa propõe distintas estratégias para analisar restrições temporais possibilitando avaliá-las em diferentes níveis de abstração, tais como em modelos iniciais de requisitos e a partir da avaliação empírica de anotações dos modelos arquiteturais. Inicialmente, construtores, estereótipos e enumerações do profile MARTE são rastreadas para descrever requisitos não-funcionais dos STRE. Com base na semântica e sintaxe do profile MARTE, no uso combinado da SysML, do formalismo do Timed Automata e das diretrizes propostas na SPES, a metodologia  $MARTeSys^{ReqD}$  foi desenvolvida e apresentada nesta tese. A metodologia MARTeSys<sup>ReqD</sup> emprega conceitos de Model-Driven Systems Engineering e propõe orientações para o design de STRE baseando-se em viewpoints, níveis de granularidade, anotações e verificações de importantes características de tempo real. Além disto, MARTeSys<sup>ReqD</sup> define novas estratégias para formalizar as atividades de modelagem arquitetural, para medir a complexidade do design dos STRE e para validar restrições temporais desde os modelos iniciais do *viewpoint* de Requisitos. A metodologia desenvolvida é validada de maneira quantitativa e qualitativa de modo a

atestar suas contribuições e expressividade para o desenvolvimento dos SRTE.

**Palavras-chave:** Sistemas de Tempo Real e Embarcados, Engenharia de Requisitos, Arquitetura de Sistemas, SysML, MARTE, SPES, Restrições não-funcionais, Complexidade do Design.

## Abstract

Real-time embedded systems (RTES) are increasingly omnipresent in human activities. The reliability and accuracy with which these systems are developed have a predominant impact when dealing with system operation. Thus, the success in the development of these systems relates not only to the accurate computational execution itself, but also how reliably real-time embedded constraints are developed. Requirements Engineering (RE) and architectural design of RTES are challenging activities, since they deal with complex and diversified domains such as software, hardware, mechanical, electronics, electrical and the physical environment. Requirements specification and architectural design, associated with the RTES domain, must attend to embedded and functional system requirements and their related non-functional concerns, while considering cost, quality, reliability and safety properties. This thesis relates to the development and analysis of a methodology that covers different phases of RTES design. Different strategies for analyzing timing constraints are proposed in such a way that they are evaluated at different abstraction levels, such as early analysis of requirement models and empirical evaluation of architectural models assumptions. Initially, constructors, stereotypes and enumerations of the MARTE profile are traced and linked to specific and non-functional concerns of the RTES domain. Through the collected data and the combined use of the SysML profile, Timed Automata and SPES guidelines the MARTeSys<sup>*ReqD*</sup> methodology is proposed. The proposed methodology employs Model-Driven Systems Engineering approaches and presents distinctive guidelines to design RTES based on viewpoints, refinements, granularity levels, annotation and verification of real-time embedded concerns. Furthermore, the proposed methodology provides new strategies to formally describe architectural design decisions, to measure the design complexity of RTES, as well as to validate timing constraints from the early model requirement viewpoint. The methodology proposed in this study is both quantitatively and qualitatively validated, which aims at demonstrating the expressiveness and contributions made toward RTES development.

**Keywords:** Real-Time Embedded System, Requirement Engineering, System Architecture, SysML, MARTE, SPES, Non-Functional Constraints, Design Complexity.

# **List of Figures**

| Figure 1 –  | Research Methodology Applied in the $\mathrm{MARTeSys}^{ReqD}$ Methodology | 37  |

|-------------|----------------------------------------------------------------------------|-----|

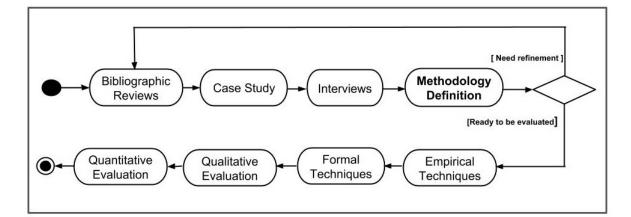

| Figure 2 –  | Diagrams of SysML Profile, adapted of [1]                                  | 53  |

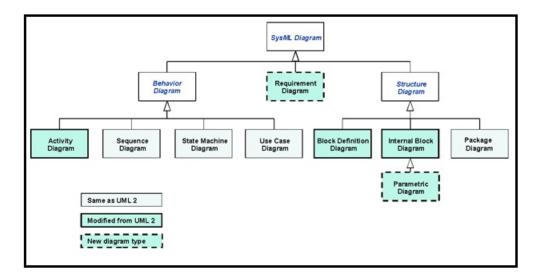

| Figure 3 –  | SysML Requirements Model, adapted of [1]                                   | 54  |

| Figure 4 –  | SysML Blocks Diagram Model, adapted of [1]                                 | 55  |

| Figure 5 –  | Viewpoints and Granularly Views of SPES Methodology                        | 57  |

| Figure 6 –  | MARTE Profile Architecture, adapted from [2]                               | 59  |

| Figure 7 –  | Global View of the MARTeSys <sup><math>ReqD</math></sup> Methodology       | 77  |

| Figure 8 –  | General Flow of the MARTeSys <sup><math>ReqD</math></sup> Methodology      | 81  |

| Figure 9 –  | The MARTeSys <sup><math>ReqD</math></sup> Methodology                      | 83  |

| Figure 10 – | Correlation between Requirements Engineering Process and Require-          |     |

|             | ments Viewpoint of the MARTeSys $^{ReqD}$ Methodology                      | 85  |

| Figure 11 – | Example of Requirements Refinement within the Activity of High-Level       |     |

|             | Description of Requirements.                                               | 88  |

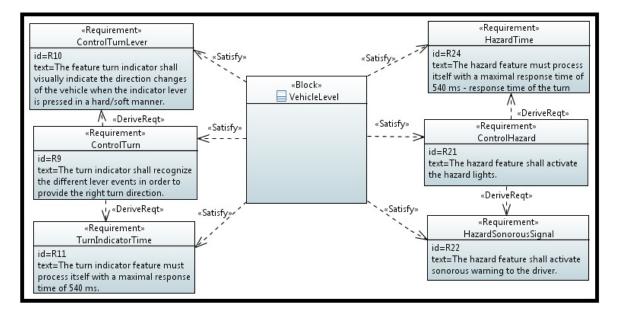

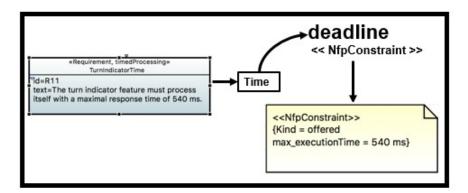

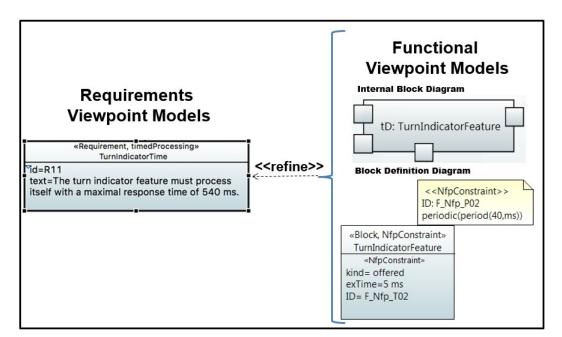

| Figure 12 – | Formalization of Concerns in Requirements Models by VSL                    | 89  |

| Figure 13 – | Example of Application: Requirements Pre-Analysis                          | 93  |

| Figure 14 – | Example of Application: High-Level Description of Requirements             | 94  |

| Figure 15 – | Example of Application: Composition of Models using the MARTE              |     |

|             | Profile                                                                    | 94  |

| Figure 16 – | Example of Application: Stereotyped annotations by VSL Formalism.          | 95  |

| Figure 17 – | Example of Application: Analysis of Requirements                           | 95  |

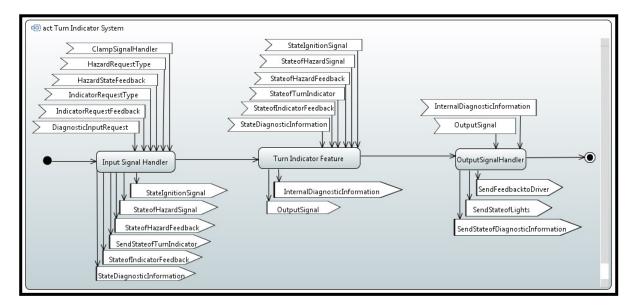

| Figure 18 – | Example of Application: Functional Viewpoint.                              | 97  |

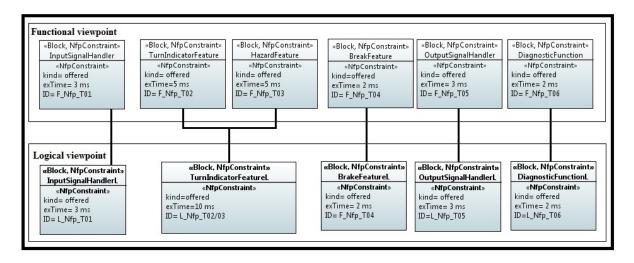

| Figure 19 – | Mapping between the Functional viewpoint and Logical viewpoint. $\ .$      | 98  |

| Figure 20 – | Mapping between Functional and Logical viewpoints                          | 100 |

| Figure 21 – | General Framework of the MARTeSys $^{ReqD}$ Methodology                    | 102 |

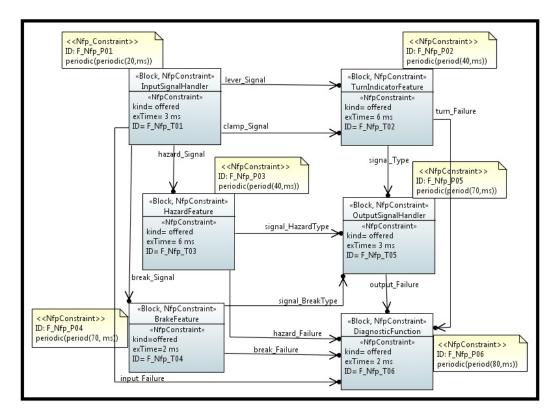

| Figure 22 – | Trace of $\ll NfpConstraint \gg$ from Functional Viewpoint to Logical      |     |

|             | Viewpoint                                                                  | 103 |

| Figure 23 – | Contributions of the Proposed Formalization.                               | 105 |

| Figure 24 –   | Viewpoints of Real-Time and Embedded Design and their Complexity          |      |

|---------------|---------------------------------------------------------------------------|------|

|               | Function.                                                                 | 119  |

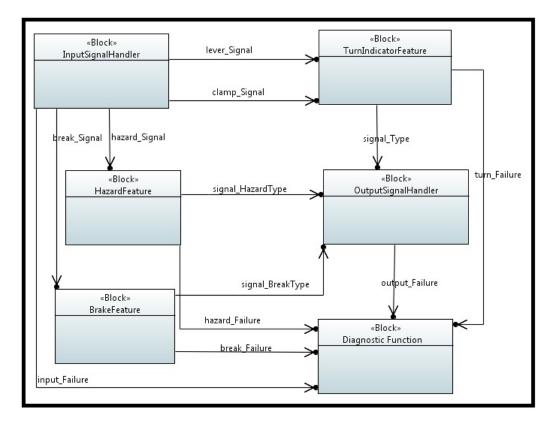

| Figure 25 –   | Domains in Automotive System Development                                  | 126  |

| Figure 26 –   | Structure of the Body Control Module                                      | 127  |

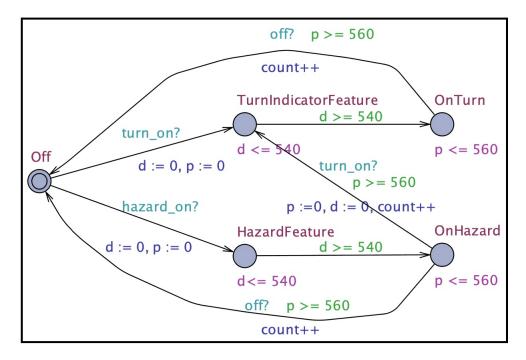

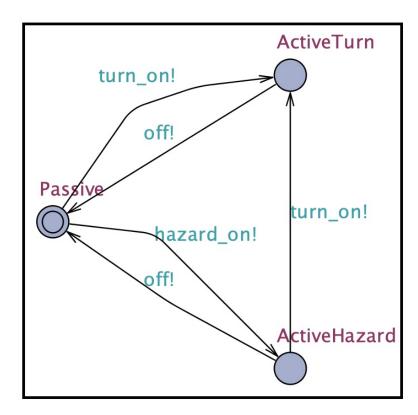

| Figure 27 –   | Features of the Turn Indicator System                                     | 128  |

| Figure 28 –   | An Example Scenario of Turn Indicator System                              | 130  |

| Figure 29 –   | Artefact of High-Level Description of Requirements - Use Case Dia-        |      |

|               | gram                                                                      | 137  |

| Figure 30 –   | Artefact of the Composition of Models using the MARTE Profile and         |      |

|               | VSL Formalism - SysML Requirements Diagram                                | 139  |

| Figure 31 –   | Artefact of the Analysis of Requirements - The <b>Timed Automata</b>      |      |

|               | diagram of the Turn Indicator System.                                     | 140  |

| Figure 32 –   | Artefact of the Analysis of Requirements - The Trigger <b>Timed Au-</b>   |      |

|               | tomata diagram.                                                           | 140  |

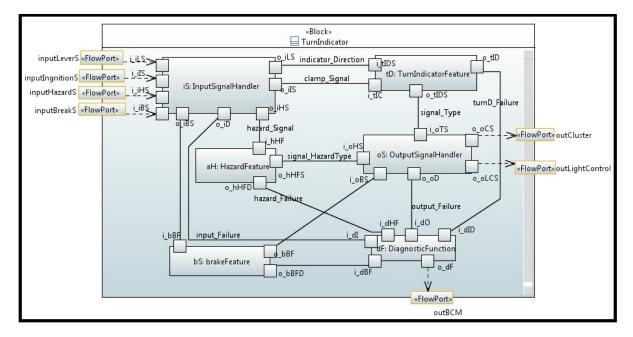

| Figure 33 –   | First Refinement of Functional Viewpoint - SysML Block Diagram.           | 142  |

| Figure 34 –   | Second Refinement of Functional Viewpoint - SysML Internal Block          |      |

|               | Diagram                                                                   | 142  |

| Figure 35 –   | Third Refinement of Functional Viewpoint - $\mathbf{SysML}$ Block Diagram |      |

|               | with MARTE annotations                                                    | 143  |

| Figure 36 –   | First Refinement of the Logical Viewpoint: Turn Indicator Model -         |      |

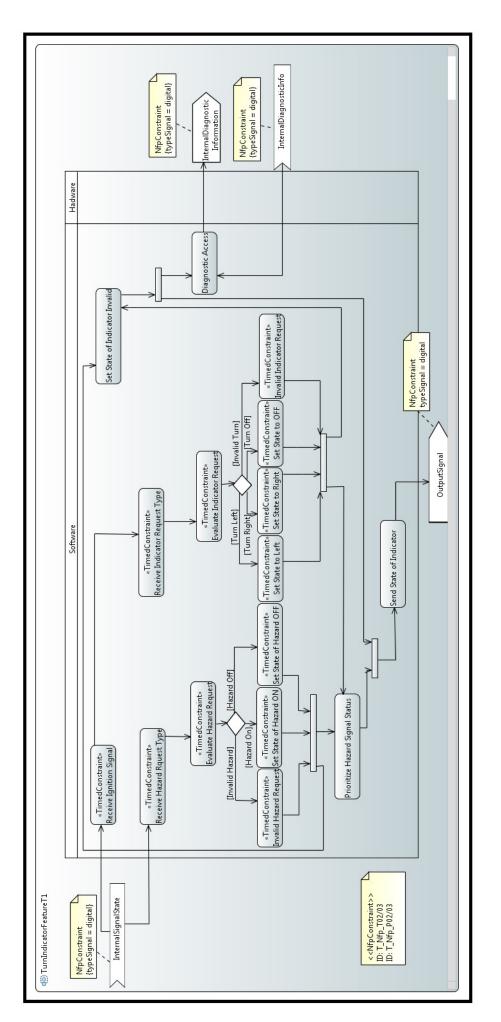

|               | SysML Activity Diagram.                                                   | 144  |

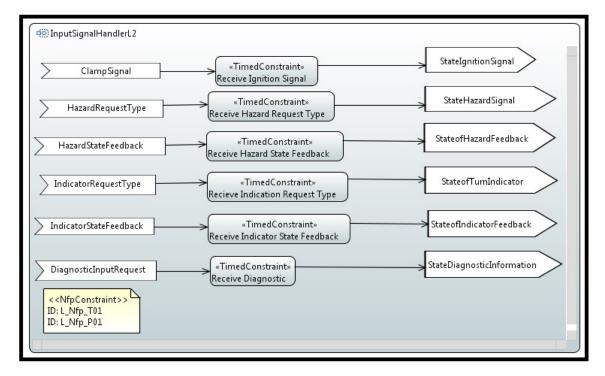

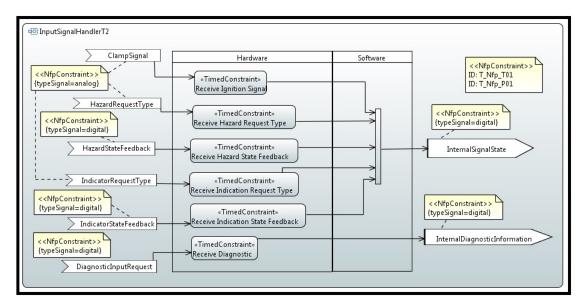

| Figure 37 –   | Second Refinement of the Logical Viewpoint: Input Signal Handler -        |      |

|               | SysML Activity Diagram.                                                   | 145  |

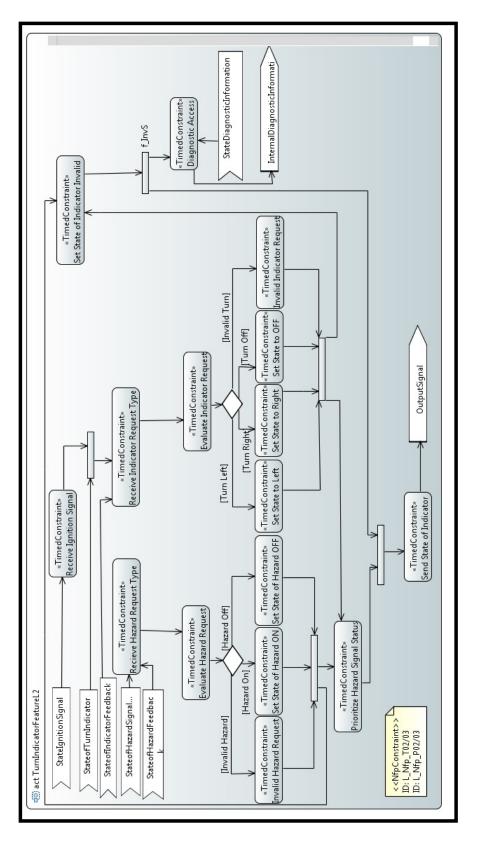

| Figure 38 –   | Second Refinement of the Logical Viewpoint: Turn Indicator Features       |      |

|               | - SysML Activity Diagram.                                                 | 146  |

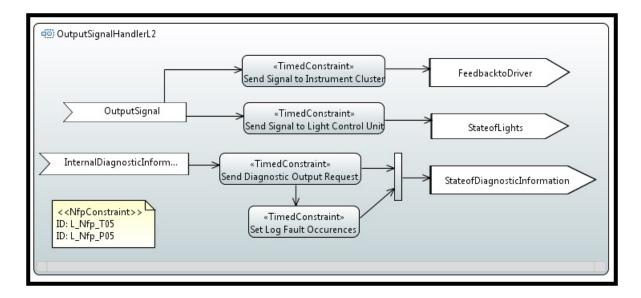

| Figure 39 –   | Second Refinement of the Logical Viewpoint: Output Signal Handler         |      |

|               | - SysML Activity Diagram.                                                 | 147  |

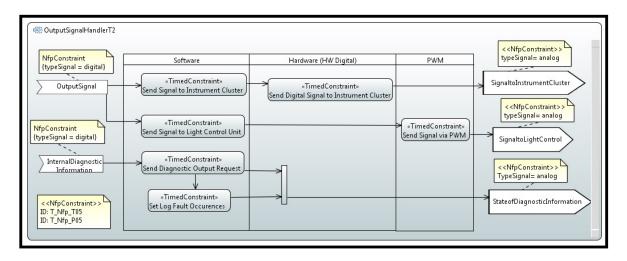

| Figure 40 –   | Technical Viewpoint: Input Signal Handler.                                | 148  |

| Figure 41 –   | Technical Viewpoint: Output Signal Handler                                | 148  |

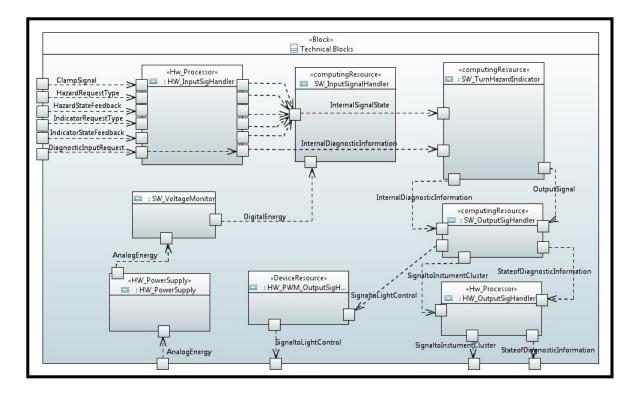

| Figure 43 $-$ | Global System Architecture of Turn Indicator                              | 149  |

| Figure 42 –   | Technical Viewpoint: Turn Indicator Features                              | 150  |

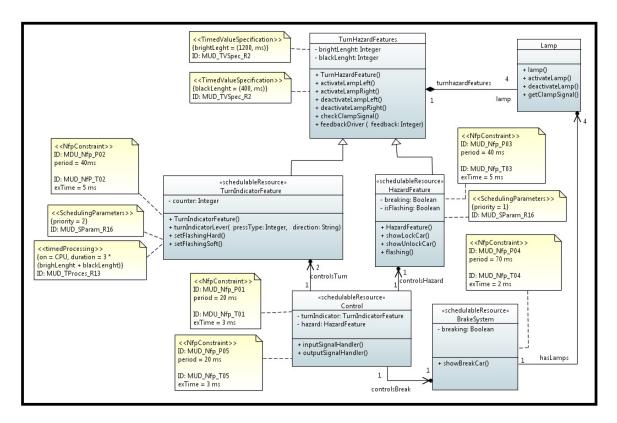

| Figure 44 –   | Class Diagram of Turn Indicator with MARTE Constraints. $\ldots$ .        | 151  |

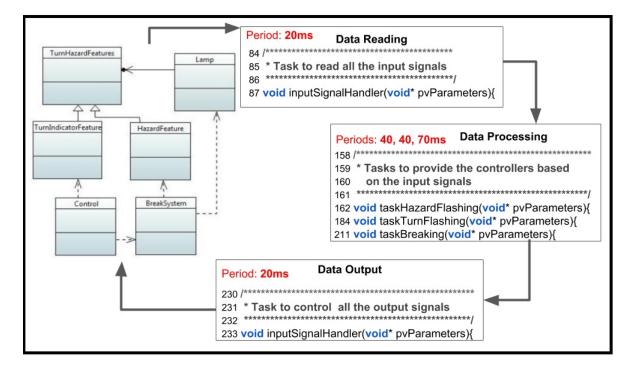

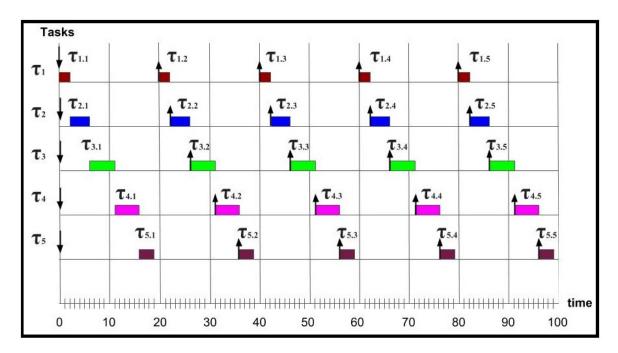

| Figure 45 –   | Tasks of Turn Indicator System                                            | 152  |

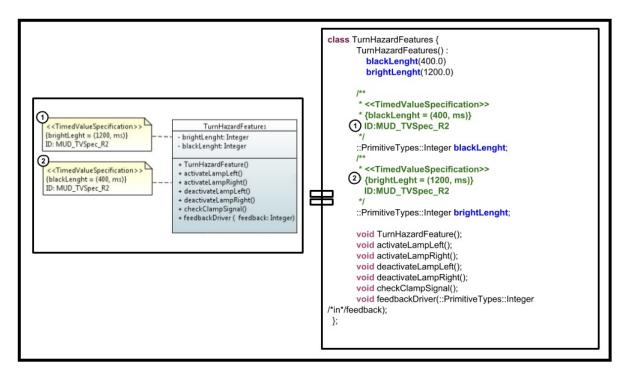

| Figure 46 –   | Tracing Non-Functional Constraints to System Implementation               | 153  |

| Figure 47 –   | Rate Monotonic Scheduling of the Tasks of the Turn Indicator Example.     | .159 |

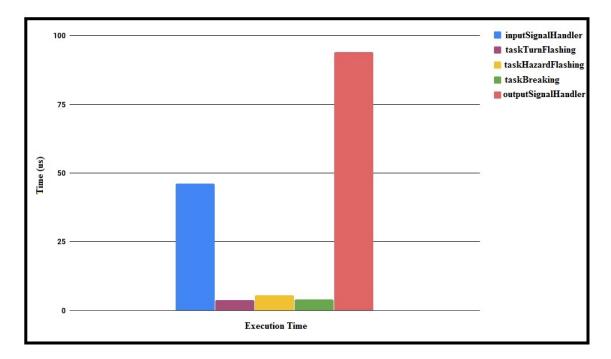

| Figure 48 –   | Execution Time Simulation of Tasks.                                       | 160  |

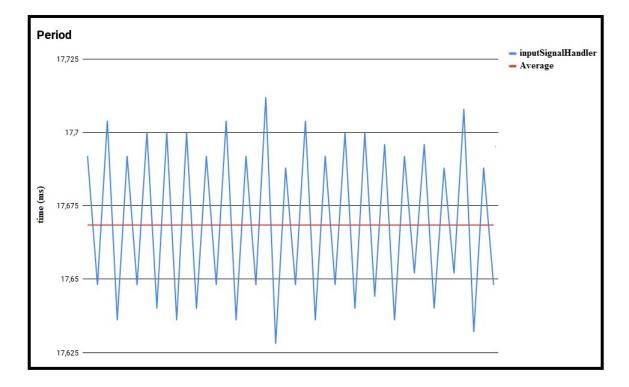

| Figure 49 –   | Period of Input Signal Handler Task                                       | 162  |

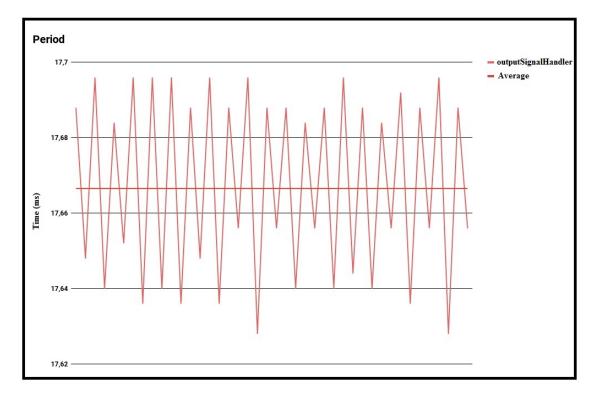

| Figure 50 –   | Period of Output Signal Handler Task.                                     | 163  |

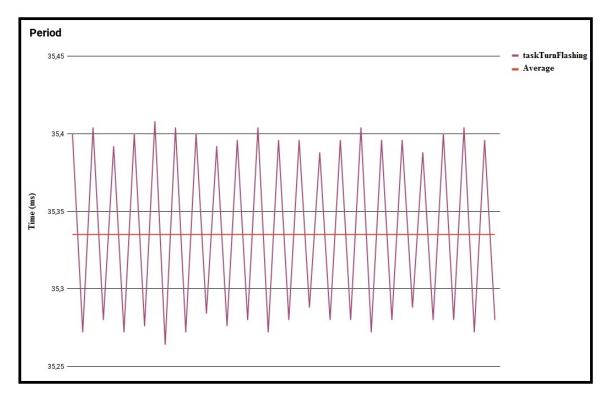

| Figure 51 –   | Period of Turn Flashing Task                                              | 163  |

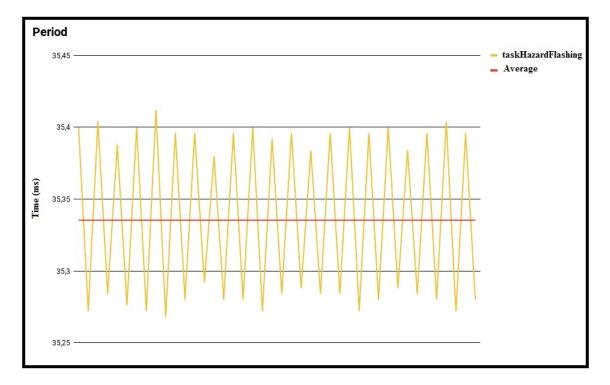

| Figure 52 – Period of Hazard Flashing Task                                               | 164 |

|------------------------------------------------------------------------------------------|-----|

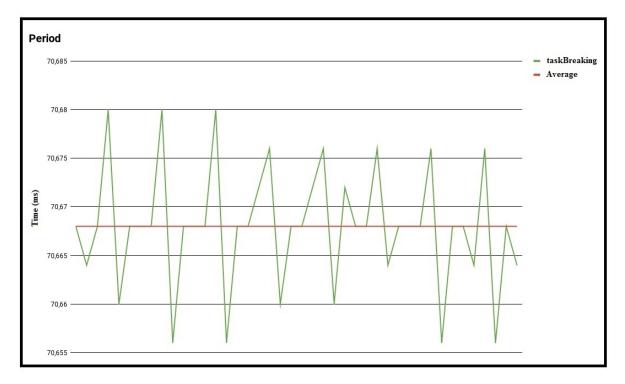

| Figure 53 – Period of Breaking Task                                                      | 164 |

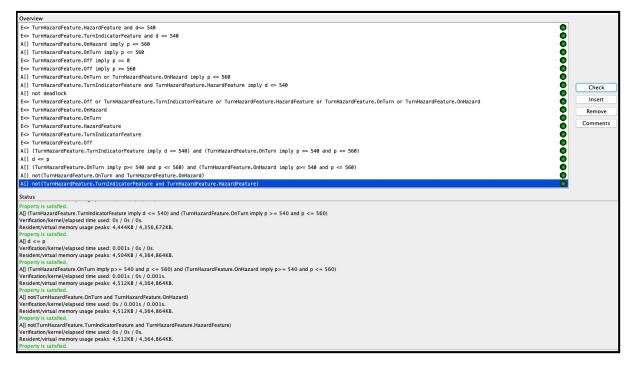

| Figure 54 $-$ The Proposed TCTL Specifications and the Validation Results. $\ . \ . \ .$ | 166 |

| Figure 55 – Main Steps to Perform the Qualitative Evaluation                             | 169 |

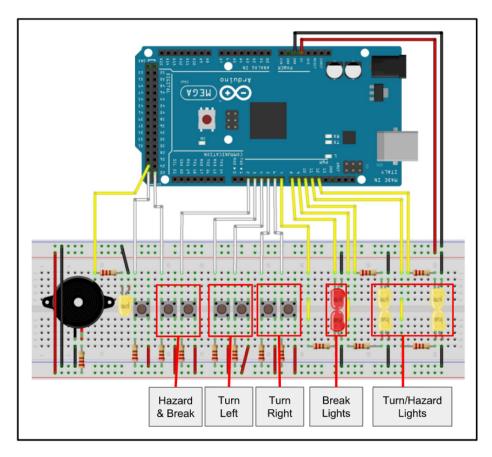

| Figure 56 – Prototype of Turn Indicator System.                                          | 213 |

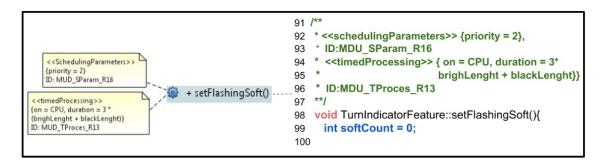

| Figure 57 – Example of MARTE Constraints to the System Realization                       | 215 |

## **List of Tables**

| Table 1 –   | Real-Time Embedded Concerns.                                         | 48   |

|-------------|----------------------------------------------------------------------|------|

| Table 2 –   | Analysis of the State of the Art                                     | 72   |

| Table 3 $-$ | Framework for the Requirements Pre-Analysis                          | 86   |

| Table 4 –   | Requirements Categorization Table - Requirements viewpoint           | 87   |

| Table 5 $-$ | Modelling Concepts and Strategies adopted in the Refinements of the  |      |

|             | Requirements Viewpoint.                                              | 96   |

| Table 6 –   | The Concepts adopted in the Refinements of the Functional viewpoint. | 96   |

| Table 7 $-$ | Algorithms and their Cost Functions                                  | 115  |

| Table 8 –   | Artefacts of the Requirements Pre-Analysis - Requirements Specifi-   |      |

|             | cation                                                               | 133  |

| Table 9 $-$ | Artefacts of the High-Level Description of Requirements- Require-    |      |

|             | ments Categorization.                                                | 137  |

| Table 10 –  | MARTE Constraints Simulation                                         | 158  |

| Table 11 –  | Tasks and their Expected Scheduling Policy.                          | 159  |

| Table 12 –  | Attendees of the First Qualitative Evaluation                        | 172  |

| Table 13 –  | Attendees of the Second Qualitative Evaluation.                      | 174  |

| Table 14 –  | Adoption of MARTE Packages Stereotypes to represent RTES Concerns.   | .208 |

| Table 15 –  | Results of the First Qualitative Evaluation                          | 218  |

| Table 16 –  | Results of the Second Qualitative Evaluation.                        | 221  |

## **Acronyms List**

**AMF** Architecture Modeling Framework

AOSD Aspect-Oriented Software Development

- AMoDE-RT Aspect-oriented Model Driven Engineering for Real-Time systems

- **ACS** Automotive Control Systems

- **ADC** Automotive Doors Control

- BCM Body Control Module

- **BDD** Blocks Definition Diagram

- ${\bf CPU}\,$  Central Process Unit

- **DRM** Detailed Resouce Modeling

- **DSMLs** Domain-Specific Modelling Languages

- **DERAF** Distributed Embedded Real-time Aspects Framework

- **DERCS** Distributed Embedded Real-time Compact Specification

- ${\bf ECU}$  Electronic Control Unit

- GenERTiCA Generation of Embedded Real Time Code based on Aspects

- **GRM** Generic Resource Modeling

- GCM Generic Component Model

- **GQAM** Generic Quantitative Analysis Modeling

- HRM Hardware Resource Modeling

${\bf IBD}\,$  Internal Block diagram

IL Interaction Level

**IS** Interface Size

**IPS** Industrial Packing System

**MARTE** Modeling and Analysis of Real-Time Embedded Systems

**MDSE** Model-Driven Systems Engineering

NFP Non-Functional Properties Modeling

${\bf NL}\,$ Natural Language

**NL-TA** Natural Language to Timed Automata

**OO** Objected-Oriented

**OAC** Operation Argument Complexity

PC Product Complexity

${\bf PWM}\,$  Pulse-width Modulation

**STRE** Sistemas de Tempo Real e Embarcados

**RTS** Real-Time Systems

**RTES** Real-Time Embedded Systems

**RE** Requirements Engineering

${\bf RCM}\,$  Rubus Component Model

**RTMS** Road Traffic Management Systems

**SRM** Software Resource Modeling

$\mathbf{SysML}$  Systems Modeling Language

**SPES** Software Platform Embedded Systems

SoCs Systems-on-Chip

**TA** Timed Automata

**TIS** Turn Indicator System

**UML** Unified Modeling Language

UML-RT Unified Modeling Language - Real Time

## Contents

| 1     | INTRODUCTION                                           | 31        |

|-------|--------------------------------------------------------|-----------|

| 1.1   | $\operatorname{Motivation}$                            | 35        |

| 1.2   | Research Methodology                                   | 36        |

| 1.2.1 | Goals and Scope Delimitation                           | 38        |

| 1.2.2 | Assumptions and Research Questions                     | 40        |

| 1.3   | Contributions of the Thesis                            | 42        |

| 1.4   | Organization of the Thesis                             | 43        |

| 2     | THEORETICAL FOUNDATION                                 | 45        |

| 2.1   | Real-time Embedded Systems and their Properties        | 45        |

| 2.2   | Real-Time Embedded Constraints in Architectural Models | 47        |

| 2.3   | Model-Driven Systems Engineering                       | 47        |

| 2.4   | Specification and Design of Real-Time Embedded Systems | <b>49</b> |

| 2.5   | Characterization of UML                                | 50        |

| 2.6   | Characterization of Timed Automata                     | 51        |

| 2.7   | Characterization of SysML                              | 52        |

| 2.7.1 | Use Case Diagram                                       | 53        |

| 2.7.2 | SysML Requirements Diagram                             | 54        |

| 2.7.3 | SysML Block Definition Diagram                         | 55        |

| 2.7.4 | SysML Internal Block Diagram                           | 56        |

| 2.7.5 | SysML Activity Diagram                                 | 56        |

| 2.8   | Software Platform Embedded Systems                     | 57        |

| 2.9   | Characterization of the MARTE Profile                  | 59        |

| 2.9.1 | MARTE Foundations Model                                | 60        |

| 2.9.2 | MARTE Design Model                                     | 61        |

| 2.10  | Contributions of this Chapter                          | 63        |

| 3     | STATE OF THE ART ANALYSIS                                                                                                       | <b>65</b> |

|-------|---------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1   | Methodologies to Design Real-Time Embedded Systems                                                                              | <b>65</b> |

| 3.2   | Formalization of Architectural Viewpoints                                                                                       | 72        |

| 3.3   | Contributions                                                                                                                   | 75        |

| 4     | MARTESYS <sup><i>ReqD</i></sup> METHODOLOGY                                                                                     | 77        |

| 4.1   | $\mathbf{MARTeSys}^{ReqD} \ \mathbf{Scope} \ \ldots \ $ | 77        |

| 4.2   |                                                                                                                                 | 80        |

| 4.3   | <b>Requirements Specification and Architectural Viewpoints within</b>                                                           |           |

|       | ${f the}\;{f MARTeSys}^{ReqD}\;{f Methodology}\;\ldots\;\ldots\;\ldots\;\ldots\;\ldots\;\ldots\;\ldots$                         | 83        |

| 4.4   | Requirements Viewpoint of the $MARTeSys^{ReqD}$ Methodology                                                                     | 84        |

| 4.4.1 | Requirements Pre-Analysis                                                                                                       | 84        |

| 4.4.2 | High-Level Description of Requirements                                                                                          | 86        |

| 4.4.3 | Composition of Models using the MARTE Profile                                                                                   | 88        |

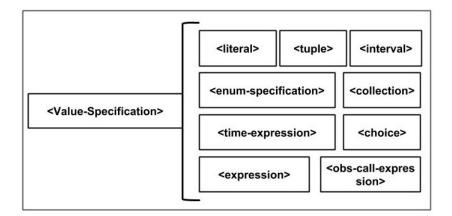

| 4.4.4 | Formal Specification with VSL                                                                                                   | 89        |

| 4.4.5 | Requirements Analysis                                                                                                           | 90        |

| 4.4.6 | Application of the Requirements Viewpoint                                                                                       | 93        |

| 4.4.7 | Summary of Requirements viewpoint                                                                                               | 95        |

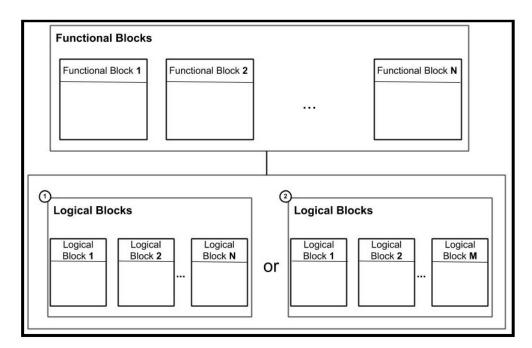

| 4.5   | ${\bf Functional \ Viewpoint \ of \ the \ MARTeSys}^{ReqD} \ {\bf Methodology}  .$                                              | 96        |

| 4.5.1 | Application of the Functional Viewpoint                                                                                         | 97        |

| 4.6   | ${\bf Logical \ Viewpoint \ of \ the \ MARTeSys}^{ReqD} \ {\bf Methodology}  \ldots  .$                                         | 98        |

| 4.6.1 | Application of the Logical Viewpoint                                                                                            | 99        |

| 4.7   | ${\rm Technical \ Viewpoint \ of \ the \ MARTeSys}^{{\it ReqD}} \ {\rm Methodology} \ \ . \ .$                                  | 100       |

| 4.7.1 |                                                                                                                                 | 101       |

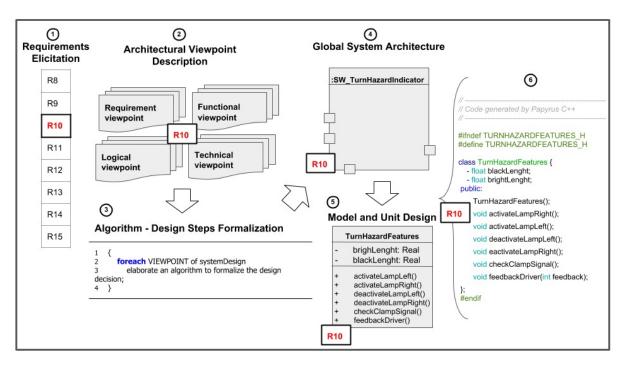

| 4.8   | From Architectural Viewpoints to Global System Architecture                                                                     | 101       |

| 4.9   | An Strategy to Trace Real-Time Embedded Systems Con-                                                                            |           |

|       | straints in Architectural Viewpoints                                                                                            | 103       |

| 4.10  | Contributions                                                                                                                   | 104       |

| 5     | FORMALIZATION OF MARTESYS <sup><i>ReqD</i></sup>                                                                                | 105       |

| 5.1   | Formalization of the Design Decision of Architectural View-                                                                     |           |

|       | $\mathbf{points}$                                                                                                               | 105       |

| 5.2   | Algorithms to Describe the Architectural Viewpoint                                                                              | 107       |

| 5.2.1 | Formalization of Requirements Viewpoint Decisions                                                                               | 108       |

| 5.2.2 | Formalization of Functional Viewpoint Decisions                                                                                 | 109       |

| 5.2.3 | Formalization of Logical Viewpoint Decisions                                                                                    | 112       |

| 5.2.4 | Formalization of the Technical Viewpoint Decisions                                                                              | 113       |

| 5.3   | A Strategy to Analyze the Architectural Viewpoints in RTES                                                                      |           |

|       | Development                                                                                                                     | 115       |

| 5.3.1 | Partial Asymptotic Analysis of the $\mathrm{MARTeSys}^{ReqD}$ Design Decisions $% \mathcal{A}$ . | 115          |

|-------|--------------------------------------------------------------------------------------------------|--------------|

| 5.3.2 | System Complexity Prediction of Architectural Viewpoint Design                                   | 119          |

| 5.4   | Contributions of the Proposed Formalization                                                      | 122          |

| 6     | APPLICATION OF THE MARTESYS <sup>ReqD</sup> METHODOLOGY                                          | 125          |

| 6.1   | An Overview of Automotive Control Systems                                                        | 125          |

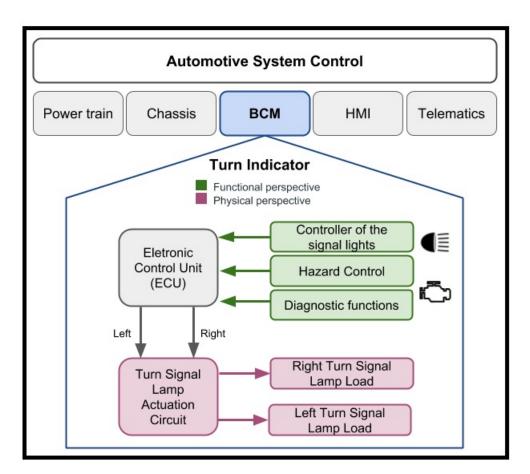

| 6.1.1 | Body Control Module                                                                              | 126          |

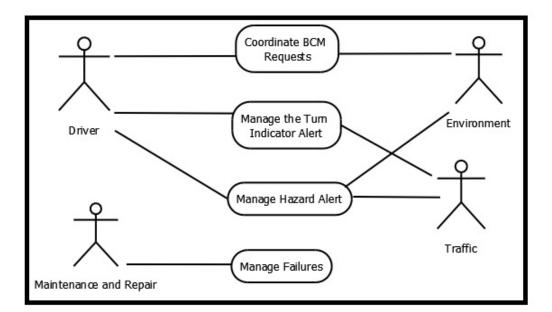

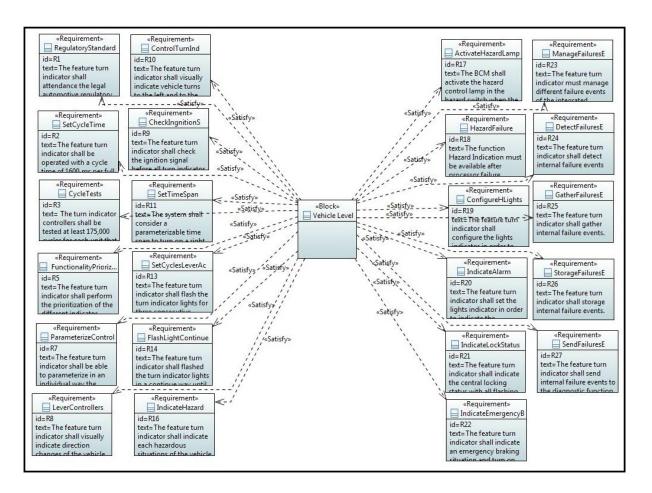

| 6.1.2 | A Motivating Case: The Turn Indicator System                                                     | 128          |

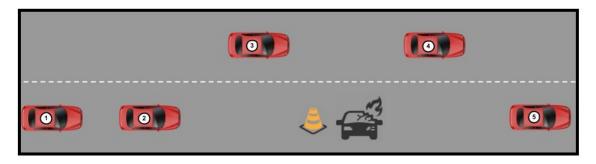

| 6.1.3 | Scenario of the Turn Indicator System                                                            | 129          |

| 6.2   | Design of Architectural Viewpoints of the Turn Indicator System                                  | n <b>130</b> |

| 6.2.1 | Requirements Viewpoint with the MARTeSys $^{ReqD}$ Methodology                                   | 131          |

| 6.2.2 | Functional Viewpoint with the MARTeSys $^{ReqD}$ Methodology $\ . \ . \ .$                       | 141          |

| 6.2.3 | Logical Viewpoint with the MARTeSys $^{ReqD}$ Methodology $\ldots$ $\ldots$ $\ldots$             | 144          |

| 6.2.4 | Technical Viewpoint with the MARTeSys $^{ReqD}$ Methodology                                      | 147          |

| 6.3   | Model and Unit Design Models                                                                     | 149          |

| 6.4   | Tracing Real-Time Embedded Systems Constraints to Imple-                                         |              |

|       | mentation Models                                                                                 | 152          |

| 6.5   | Contributions                                                                                    | 154          |

| 7     | EVALUATION OF THE MARTESYS <sup>ReqD</sup> METHODOLOGY                                           | 155          |

| 7.1   | $ {\bf Quantitative \ Evaluation \ of \ the \ MARTeSys}^{ReqD} \ {\bf Metodology} \ . \ .$       | 155          |

| 7.1.1 | Empirical Evaluation of MARTE Constraints                                                        | 156          |

| 7.2   | Early Evaluation of MARTE Constraints of Architectural View-                                     |              |

|       | $\operatorname{point}$                                                                           | 166          |

| 7.3   | $ {\bf Qualitative \ Evaluation \ of \ the \ MARTeSys}^{ReqD} \ {\bf Methodology} \ . \ . \ .$   | 168          |

| 7.3.1 | Data Gathering                                                                                   | 169          |

| 7.3.2 | First Qualitative Evaluation                                                                     | 172          |

| 7.3.3 | Second Qualitative Evaluation                                                                    | 173          |

| 7.4   | Contributions                                                                                    | 176          |

| 8     | CONCLUSION                                                                                       | 177          |

| 8.1   | Main Results                                                                                     | 177          |

| 8.2   | Research Challenges and Limitations                                                              | 179          |

| 8.3   | Future Research                                                                                  | 180          |

| 8.4   | Bibliographic Production                                                                         | 181          |

| ANNEX | A DESCRIPTION OF THE VALUE SPECIFICATION                                                         |              |

|       | LANGUAGE                                                                                         | 185          |

| A.1   | Introduction                                                                                     | 185          |

| A.2   | Time Expression                                                                                  | 187          |

| ANNEX                          | B ALGORITHMS FORMALIZATION TO MARTESYS <sup>4</sup>                                                                                                                                                                                                                                                      | ReqD                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                | METHODOLOGY                                                                                                                                                                                                                                                                                              | 191                             |

| B.1                            | Requirements Viewpoint                                                                                                                                                                                                                                                                                   | 191                             |

| B.2                            | Functional Viewpoint                                                                                                                                                                                                                                                                                     | 195                             |

| B.3                            | Mapping between Functional Viewpoint to Logical Viewpoint                                                                                                                                                                                                                                                |                                 |

|                                | Models                                                                                                                                                                                                                                                                                                   | 196                             |

| B.4                            | Logical Viewpoint                                                                                                                                                                                                                                                                                        | 198                             |

| ANNEX                          | C RELATING MARTE PROFILE CONSTRUCTORS                                                                                                                                                                                                                                                                    |                                 |

|                                | AND CONCERNS OF RTES                                                                                                                                                                                                                                                                                     | 205                             |

| C.1                            | Introduction                                                                                                                                                                                                                                                                                             | 205                             |

| C.2                            | Mapping MARTE Stereotypes to Specify RTES Constraints . 2                                                                                                                                                                                                                                                | 206                             |

|                                |                                                                                                                                                                                                                                                                                                          |                                 |

| ANNEX                          | D SYSTEM REALIZATION                                                                                                                                                                                                                                                                                     | 211                             |

| <b>ANNEX</b><br>D.0.1          | DSYSTEM REALIZATION2Toolbox for Modeling, Simulation and Verification of MARTeSys2                                                                                                                                                                                                                       | 211                             |

|                                | Toolbox for Modeling, Simulation and Verification of $MARTeSys^{ReqD}$                                                                                                                                                                                                                                   | <b>211</b><br>211               |

|                                | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup><i>ReqD</i></sup><br>Methodology                                                                                                                                                                                                      |                                 |

| D.0.1                          | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup>ReqD</sup> Methodology                                                                                                                                                                                                                | 211                             |

| D.0.1<br>D.0.2                 | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup>ReqD</sup> Methodology                                                                                                                                                                                                                | 211<br>212                      |

| D.0.1<br>D.0.2                 | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup>ReqD</sup> Methodology                                                                                                                                                                                                                | 211<br>212                      |

| D.0.1<br>D.0.2<br><b>ANNEX</b> | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup>ReqD</sup> Methodology                                                                                                                                                                                                                | 211<br>212<br><b>217</b>        |

| D.0.1<br>D.0.2<br><b>ANNEX</b> | Toolbox for Modeling, Simulation and Verification of MARTeSys <sup>ReqD</sup> Methodology       System Implementation         System Implementation       System Implementation         E       RESULTS OF THE FIRST QUALITATIVE EVAL-<br>UATION         F       RESULTS OF THE SECOND QUALITATIVE EVAL- | 211<br>212<br>217<br>217<br>219 |

I hereby certify that I have obtained all legal permissions from the owner(s) of each third-party copyrighted matter included in my thesis, and that their permissions allow availability such as being deposited in public digital libraries.

Fabíola Gonçalves Coelho Ribeiro

## Chapter

## Introduction

Software systems have been increasingly present in human activities, and many of these have a high level of complexity and automation. These systems are composed of critical, non-functional, temporal, embedded and frequently real-time requirements [3], [4]. The development of these systems is a complex activity, since qualitative and quantitative aspects, such as efficiency, reliability, safety and real-time behavior must be considered [5], [6].

Real-Time Systems (RTS) can be defined as "a computer system whose correctness depends not only on the output, but also the time at which the output is produced" [7], [8]. The term "real-time" is used for systems that react to external inputs given strict time requirements. These systems must analyze in a correct manner, as well as answer their external stimuli in a finite and pre-defined period [9]. RTS are complex systems that involve multiple perspectives of analysis, domain application and increasingly depend on the interaction between various disciplines, such as Mechanics, Electronics and Software Engineering [10], [11], [12]. Moreover, these systems are frequently developed for embedding in physical devices and, consequently, are named as Real-Time Embedded Systems (RTES) [8].

Embedded software holds a substantial relationship with one or more computers/processors, which have an imperative functionality in the system [13]. This kind of system faces several constraints such as non-functional and real-time requirements, resource limitations and hardware dependencies [3]. As of this point, in this thesis, non-functional requirements with a real-time (as detailed on Table 1) specification are simply called "constraint". Generally, RTS "include many embedded and safety-critical systems that are subcomponents of a larger complex system operating in a safety-critical environment" [14]. The class of RTES is composed of electronic, mechanical, electrical, sometimes hydraulic components in which they are encapsulated. Besides, these systems must coordinate in a temporal manner their software, hardware and mechanical elements [15].

The design, development, implementation and maintenance of RTES has always been

considered difficult and challenging [16], [17], [8], [18], [19]. RTES must accomplish their functional requirements, also meet cost, quality, reliability and safety requirements [20]. In this sense, Software Engineering proposes a variety of activities, processes, methods and tools that assist in the analysis, description, development and maintenance of RTES [10], [13], [21].

A variety of standards, formalisms, languages and approaches have been proposed in recent years to assist developers in managing software development activities and help them to deal with the inherent complexity of RTES [22], [23], [13], [24]. Model-Driven Systems Engineering (MDSE) approaches can contribute and facilitate RTES development, since it encompasses design strategies in order to develop, evolve, verify, formalize, configure and maintain embedded, real-time and distributed software [25], [26]. MDSE approaches are based on models that direct system development, perform refinements of different abstraction levels and provide several types of stakeholder interaction [27]. Thus, MDSE approaches must be able to support specification and design of embedded hardware and software components, which includes functional and non-functional requirements, as well as to ensure the correct translation of specifications into executable embedded systems [6].

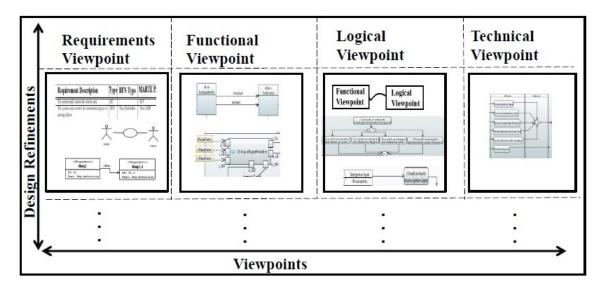

In RTES development, Software Engineering activities are characterized as being difficult and complex, since since they must address functional and non-functional properties in a correct and consistent manner, while performing analysis and description of distinctive domains [28], [29]. Thus, such activities require, increasingly, high levels of knowledge in order to specify and formalize RTES concerns along architectural design [30]. RE defines a set of well-established practices that are able to describe and detail the properties of an RTES [3]. Requirements viewpoint [18] of RTES aims at ensuring that the complete set of needs, requirements and restrictions of a system will be captured and, posteriorly, transformed into a valid set of requirements for all activities of the software life cycle [31], [26], [21], [32]. Furthermore, the Requirements viewpoint provides the basis for further Functional, Logical and Technical viewpoints of architectural system design [33], [18].

Among the other software development activities, Architectural Design, mapped here in the Functional, Logical and Technical viewpoints, is defined as the set of activities that involves analyses, refinements and development of system requirements at different abstraction levels. The architectural design represents a fundamental activity during the development of the RTES [34], [35], [36], [20], [18]. Architectural design artefacts aims to describe software structure (detailing its components), to capture initial decisions of the project, to present the behavioral overview of the system, to specify system technical artifacts and, also, to contribute to the general reliability of the system [37], [29]. It also allows one to describe software architectural characteristics in which associations/communications between components and connectors are made explicit [38], [34], [35].

Architectural design and the artefacts that are derived from this process are vulnerable

to erroneous choices in the early stages of RTES development [24]. Such choices may impact negatively on the development and deployment phases of RTES [38], [39], [37], [36]. Therefore, it can be inferred that, for most RTES projects, it is of great importance to understand, analyze, specify and validate the artefacts which arise from the design since it can minimize complexity in its description and correct development [40], [39].

The development of RTES must specify structure and behavior of software, along with its physical and logical resources, its infrastructure and temporal constraints [10], [41], [42], [26], [43]. Therefore, using a single modelling language/method may not be sufficiently suitable to cover all the multidisciplinary aspects that describes the RTES domain [44], [45], [46], [47]. The combination of modelling techniques, languages and methodologies can contribute to the full RTES description [48], [49], [5].

In a general sense, RTES engineers tend to use different approaches (formal, graphical models or object-oriented) for modelling, analysis and specification of RTES [50], [51], [47]. Furthermore, the specification language must be robust enough to represent the system requirements at different abstraction levels in order to avoid omissions in the specification and enable elicitation of physical, logical and temporal requirements, as well as other aspects that describe these systems [20]. Thus, adoption of approaches based on perspectives, multiple granularity levels and refinements, together with formal and semiformal languages, contributes to the system design, development of their components and complex relationships [52], [11], [44], [53], [54].

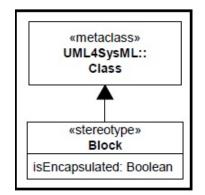

Several Domain-Specific Modelling Languages (DSMLs) [45] have been proposed in the form of extensions to the Unified Modeling Language (UML) metamodel and are named as profiles [55], [56], [2], [57], [1]. UML is designed to be customizable and extensible and it has been applied to several domains [44], [58], [59]. The UML metamodel includes many semantic variables and provides special constructors in the language for refinement. Such constructs, stereotypes, tagged values, and tags are used to define DSMLs based on UML [60]. As these capture domain-specific concepts, profiles are typically used together with other specific stereotypes of the same domain. Profiles are usually based on only one subset of the UML metamodel (as opposed to the complete metamodel), resulting in simpler and more compact DSMLs, commonly contributing to representation of requirements that are intrinsic to RTES [12].

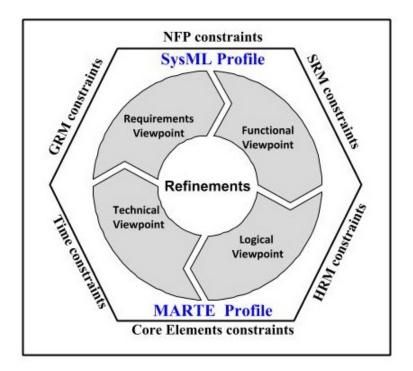

In this thesis, UML, MARTE and SysML profiles, SPES methodology and Timed Automata language are combined in order to provide an overall methodology to specify and design RTES. The combined adoption of these languages/profiles encompasses functional and non-functional concerns in model elements along the architectural viewpoint design of RTES. The proposed methodology aims at defining a general and appropriate architectural viewpoint definition to design RTES. Thus, it adopts viewpoints and refinements of architectural viewpoints with focus on RTES design. In the Requirements, Functional, Logical and Technical viewpoints, these refinements consider specific diagrams and nonfunctional annotations from the early steps of design, while fortifying the description of important aspects concerning these systems.

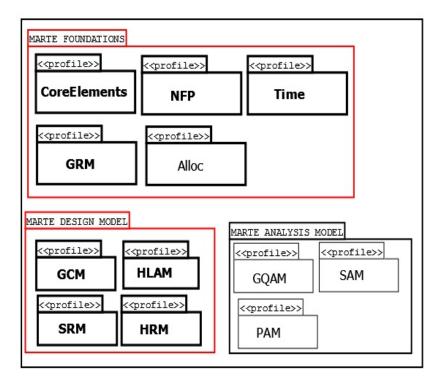

The Software Platform Embedded Systems (SPES) methodology provides a framework toward RTES development, while providing guidelines to software and system design. The adoption of SPES viewpoints and their perspectives contributes to minimizing the complexity of RTES development, as it performs separation of non-functional concerns and functional system services [33]. The proposed decomposition of system services can favor one's understanding and development of such services [61], [62]. Modeling and Analysis of Real-Time Embedded Systems (MARTE) extend the UML with constructors to analyze, modelling and design RTES [2]. Systems Modeling Language (SysML) is also a UML extension that supports system modelling allowing either high or low-level description of RTES [1]. MARTE constructors can be annotated directly in SysML models without any extension as MARTE is a UML profile [59]. Therefore, SysML and MARTE can be combined in MDSE approaches to express RTES properties.

In this thesis, MARTE profile and SPES methodology are employed in modelling strategies, from SysML and Timed Automata (TA) [63], in order to specify, design and validate the requirements, services and systems components. The combination of these strategies culminates in the development of the MARTeSys<sup>*ReqD*</sup> methodology. The MARTeSys<sup>*ReqD*</sup> methodology depicts how to design structured and dynamic models of RTES, while highlighting hardware and software requirements of these systems. The proposed methodology, which incorporates described models and guidelines to design RTES considering distinctive and complementary perspectives, is able to represent RTES characteristics such as functional and non-functional features.

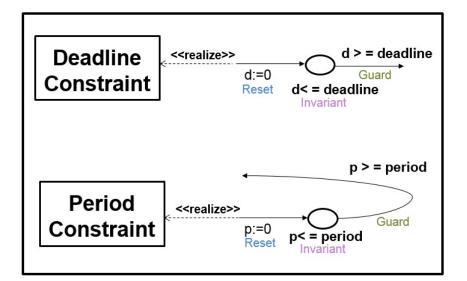

The MARTeSys<sup>*ReqD*</sup> methodology also proposes a formal definition of RTES design activities and viewpoints. The proposed formalization allows for different measurements regarding complexity of system design, from the initial design activities, as well as the definition of a formalized manner in order to analyze RTES complexity without interference of user external knowledge. In addition, it presents two novel strategies for managing RTES timing constraints: (1°) it traces RTES constraints along the architectural design to the system realization so, that it can be formally analyzed, (2°) it provides a formal grammar to transform timing specifications, written in natural language, to timed-automata. This last aspect allows for the verification of timing constraints such as period and deadlines from requirements specification documents in an unambiguous manner.

The MARTeSys<sup>ReqD</sup> methodology has been applied in different case studies such as Road Traffic Management Systems (RTMS), Automotive Control Systems (ACS), Automotive Doors Control (ADC), Industrial Packing System (IPS) and Turn Indicator System (TIS)). In this thesis, the full example of MARTeSys<sup>ReqD</sup> methodology is applied in particular to the TIS in order to show the use of the proposed methodology, guidelines for the design of complex system features, and to direct RTES development.

#### 1.1 Motivation

The development of RTES must cover different development phases, such as requirements specification and architectural design [64]. Other phases, such as source code development, testing and integration, are direct consequences of modelling activities [13]. RTES operate in domains in which UML extensions can be used to provide greater expressiveness, such as mutual exclusion mechanisms, temporal features, concurrency, specification of deadlines, among others [59], [65], [47]. Moreover, formal and semi-formal languages, combined with MDSE principles, can contribute to RTES specification and design [66].

In this thesis, the author adopts MDSE concepts to support development of RTES considering analysis, modelling, evaluation and validation of timing critical constraints. The thesis scope can be subdivided into the following motivations:

- 1. Development of strategies to cover the design of RTES. This means, specifically, that the thesis concentrates on formal and semi-formal methods to model RTES along the requirements and design activities.

- 2. Enabling of annotation of RTES concerns at different abstraction levels. This thesis culminates in the MARTeSys<sup>*ReqD*</sup> methodology and it presents a wide analysis and guidelines to represent real-time and embedded concerns into architectural models.

- 3. Analysis, verification and validation of timing concerns from multiple architectural models. MARTeSys<sup>*ReqD*</sup> methodology presents guidelines to annotate models describing non-functional concerns of RTES design. Furthermore, it provides a strategy to analysis, validate and verify specific timing concerns along of RTES development.

RTES are complex, composed by functional and non-functional properties and their development must accomplish critical concerns [67]. However, this thesis is restricted to the analysis, validation and verification of designed timing concerns based on three reasons.

First, time is an essential variable to RTES [68]. Representing time is a crucial activity in RTES modelling and the mapping of temporal characteristics is of fundamental importance to RTES design activities [16], [69]. Thus, the development of RTES with a high correctness level and reliability depends on the correct specification and design of system functionalities [64], which includes analysis and specification of their time constraints [11], [15]. Therefore, design of these systems requires a complete and effective support in order to define and express temporal parameters that are related to the application under development [49]. Secondly, it is important to trace and validate timing constraints from the early design steps of RTES development. The correct description and evaluation of these complex data along the RTES design are directly related to their reliability, safety and quality [22]. It is possible to create formal and semi-formal strategies to provide guarantees regarding the time bounds of the architectural models. Here, these constraints are attached in the models, at different abstraction levels, and can be verified and validated by modelchecking and simulation strategies.

Finally, the investigation of MDSE strategies to RTES design can benefit their development [70]. The RTES projects involve multiple domain-specific languages to cover different characteristics of these systems [47]. Given the heterogeneous and complex nature of these systems, and the several different categories of stakeholders with different concerns and interests, it is necessary to use multiple languages [71], [12]. These languages should have compatible models in order to represent the various aspects of a system [44]. It is expected that the chosen design strategies for the MARTeSys<sup>*ReqD*</sup> methodology provide expressiveness of RTES design, while expressing the models of Requirements, Functional, Logical and Technical viewpoints.

This thesis has been motivated by the need to manage the complexity of RTES development, while focusing on the design of critical properties and their analyses. This is performed by the development of specific criteria for specification, modelling and the architectural design of these systems.

#### **1.2** Research Methodology

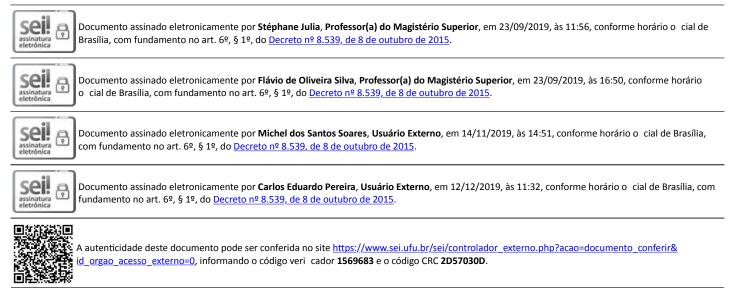

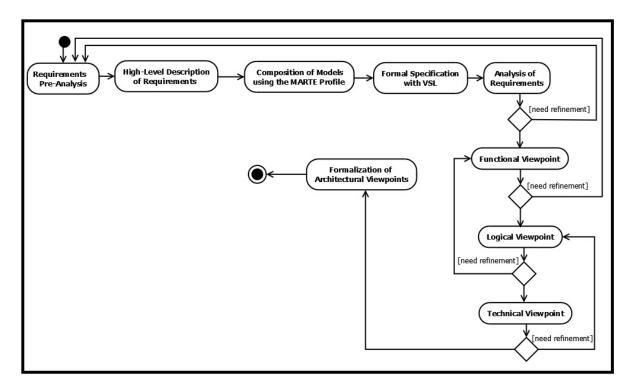

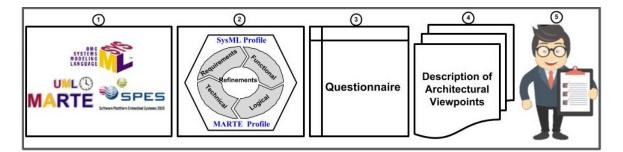

As emphasized in [72], a method is a set of organizing principles around which empirical data is collected and analyzed. A variety of methods can be applied to any research problem and, oftentimes, it becomes necessary to use a combination of methods to fully understand the problem and to conduct relevant and non-refutable issues in relation to the research criteria. Figure 1 depicts the Activity diagram followed by the adopted research methodology. This research method encloses the overall research methods and techniques to develop and evaluate the proposed study of this thesis.

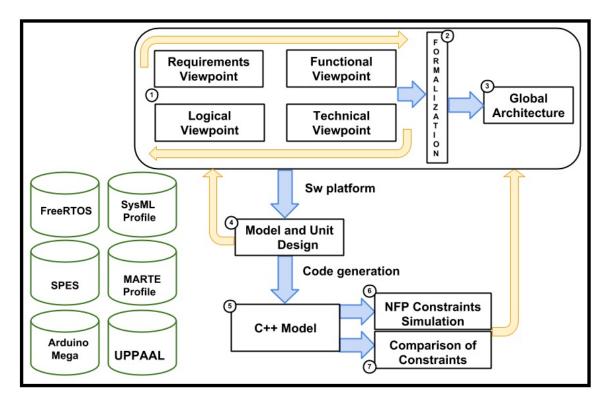

Research methods are applied in the context of a scientific research study. Therefore, they relate to goals, objectives, bibliographic reviews and validations [73], [74]. Research strategies, in Software Engineering, are applied in a specific context/strategy of investigation and seek to provide new knowledge that is expressed in the form of theoretical and practical results [75]. In the top part of Figure 1, the research methods that provide the main insights to the proposed study are presented. Regarding the data collection technique, this thesis applies mixed approaches and methods, with greater detail provided in [72] and [76]. As it can be noticed in Figure 1, the framework to develop MARTeSys<sup>*ReqD*</sup> is based on data collection techniques, from field research (for example case studies), in-

Figure 1 – Research Methodology Applied in the MARTeSys<sup>ReqD</sup> Methodology.

terviews and bibliographic reviews. These techniques help to define the scope, guidelines and design decisions of the proposed methodology.

Results of a research study can be expressed as procedures or techniques, as qualitative, descriptive, empirical or analytic models, also as tools and notations, as specific solutions, as evaluations/comparison, or, yet still, as reports with observations or rules. In the bottom part of Figure 1, the methods to perform the thesis evaluations are shown. Empirical Techniques, Formal Techniques, Qualitative and Quantitative Evaluations are considered to check the expressiveness, significance and adequacy level of the research results to RTES development. In this thesis, simulation, testing, measurements (in specific case studies) and formal validations of the design artifacts are considered in order to analyze the proposed methodology.

Qualitative and Quantitative measurements perform significant evaluation of the proposed strategy. The qualitative approach, used in this research, aims to construct a theoretical framework that emerges from the analysis of collected data during research and that explains the research results in a coherent manner [77]. The **Quantitative Evaluation** focus on assumptions evaluation and aims to measure their reliability when faced with design decisions. The quantitative research is based on the measurement of objective variables, on the comparison of results and/or on the intensive use of statistical techniques. As stated previously, the numerical values from the simulation activities aims to check if there is consistency between the architectural constrained models and the dynamics results.

Qualitative and quantitative techniques are applied in order to evaluate the results of this thesis regarding the artefacts generated from the application of the proposed methodology in an industrial case study. The case study technique stands out among the main tools for exploratory studies, and in this thesis, it will be used to support the research proposal, to understand the scope of the problem and to answer the research questions. Case studies are appropriate for various research objectives and they can be used in contexts of description (with the objective of answering questions of type "what", "where" and "how"), of explaining questions (with the objective of clarifying questions of the type "why"), of predictions (it includes state predictions of the short-term/long-term, behaviors, events) and of control process (it attempts to influence attitudes, cognitions and behaviors for a particular case) [78], [79], [80].

An analysis of usability and expressiveness, of the proposed methodology, will be performed regarding an industrial case study. For this, a team that is constituted of professionals, researchers and students who work and do research on RTES, are invited to evaluate the proposed methodology. In this way, as detailed in Chapter 7, interviews and questionnaires are applied to analyze the MARTeSys<sup>*ReqD*</sup> methodology and its contributions to requirements specification and architectural design of RTES.

Each subject receives in advance a manual and basic guidelines about the MARTe-Sys<sup>ReqD</sup> methodology. Posteriorly, the experts analyze the artefacts coming from the application of the proposed methodology, in an industrial case study. Then, interviews and questionnaires are performed. Thus, the experts may qualify and quantify their experiences. The proposed questionnaires are based on known standards of the RE process and Architectural Design such as ISO/IEC/IEEE 29148:2011 [81] and ISO/IEC/IEEE 42010:2011 [37]. Finally, different qualitative analyses are performed, by the author, from the collected data regarding the answers from the expert.

Regarding the data collection technique, as noted in Figure 1, the background to develop MARTeSys<sup>ReqD</sup> is based on data collection techniques through research in the field, specification techniques and RTES design. Therefore, the research proposed in this thesis uses mixed approaches and methods, which is given greater detail in [72], such as bibliographic analyses, literature review and case studies.

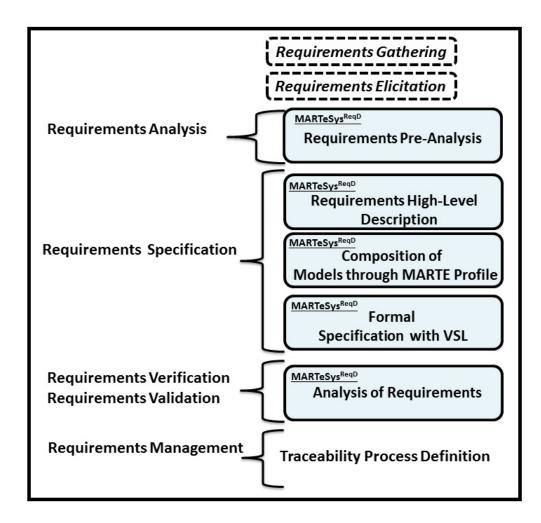

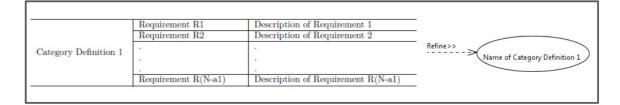

#### **1.2.1** Goals and Scope Delimitation

Different approaches to the Requirements Specification process have been proposed. Many of these approaches focus on the specification, analysis, elicitation and requirements management processes of RTES. In [82], [83] and [84] extensions to the SysML Requirements diagram were presented in order to allow for definition of a modelling methodology with relevant criteria for documentation, requirements analysis, classification, traceability and design of systems at different abstraction levels.

The author's publications, which were mentioned previously, had their focus on extensions of attributes and relationships of the SysML Requirements diagram. These extensions were applied fundamentally to activities of requirements specifications. Furthermore, it did not focus on RTES constraints annotation and traceability between artefacts from different development stages. Following the studies of [82], [83], [84], [85], and with the goal of portraying the gaps not covered in these works or in findings from the literature, this section provides details of the principle and specific objectives.

The main objective of this thesis is to provide a methodology for RTES design that covers functional and non-functional properties, while allowing timing analyses at different abstraction levels. With this in mind, it is initially intended to use the MARTE profile in combination with SysML diagrams and SPES guidelines in order to develop a methodology that can be applied to the structural and dynamic design of RTES. Furthermore, this methodology provides a manner to represent the characteristics that are inherent to RTES at separate abstraction levels. The overall design phases proposed in this thesis have been formalized to allow its application for different RTES examples. Hence, it is estimated to significantly promote the specification, description, validation and verification of RTES concerns for physical and logical system components. The specific objectives of this thesis are:

- □ To develop a methodology, based on viewpoint refinements and different abstraction levels, to the Requirements Specification and Architectural Design of RTES;

- □ To trace stereotypes and constructors of MARTE to express specific RTES concerns;

- □ To apply VSL to standardize RTES descriptions within design artefacts;

- □ To propose, in the developed methodology, a strategy to trace timing constraints between artefacts coming from the different design viewpoints and along the RTES development;

- □ To qualitatively evaluate the combined adoption of the SysML diagrams and MARTE stereotypes, together with SPES, to describe Requirements, Functional, Logical and Technical Viewpoints;

- □ To propose a formalization of the proposed methodology, through the specification of the algorithms, and its design activities;

- □ To perform complexity analyses related to the adopting of the proposed methodology;

- □ To provide a strategy to predict the global system complexity when it adopts the proposed methodology;

- □ To create a grammar to transform timing constraints descriptions, written in natural language, from Requirements viewpoints models, to formal syntax representation;

- □ To formally validate timing constraints from the early design phases and over the architectural design; To formally validate timing constraints since early design phases and over architectural design;

□ To apply the proposed methodology for specification and design of RTES in order to qualitatively and quantitatively validate the proposed methodology.

The MARTE profile provides a wide and robust framework of definitions, constructors and formalisms to define, describe and analyze RTES [59]. However, this profile still lacks the dissemination and consolidation of its model [86], as well as applications that present, qualitatively and quantitatively, its suitability, expressiveness and usability in modelling/specification processes [87], [88], [89], [90], [91].

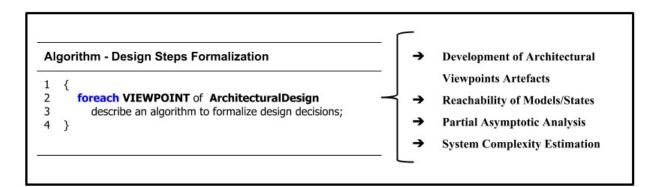

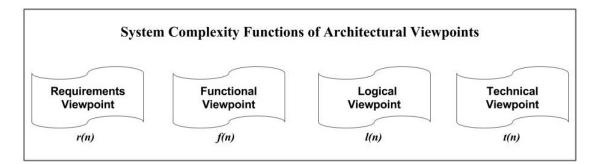

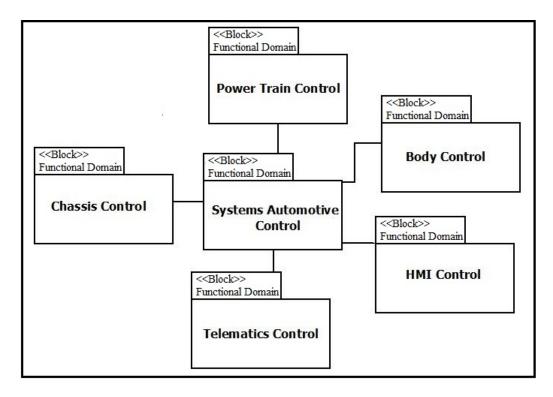

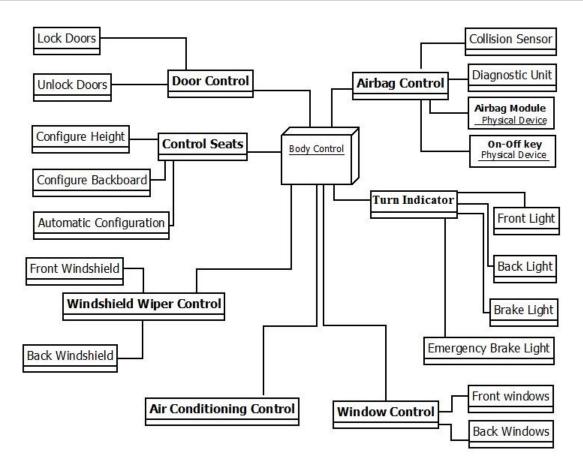

In light of these aforementioned challenges, this thesis aims to show how MARTE stereotypes and constructors can be effectively applied to detail essential concerns of RTES. The MARTeSys<sup>*ReqD*</sup> methodology also provides the trace between RTES concerns and specific constructors from MARTE (see Chapter 4). In addition, this thesis provides several guidelines to combine UML profiles to design architectural models of RTES. Finally, this thesis defines how to link the MARTE stereotypes in different RTES views, at each viewpoint, of the system. It contributes to meaningful refinements of the system design and their RTES concerns, to favor the reproducibility of design decisions and to develop architectural design. Thus, non-functional concerns can be analyzed, as of the early design phases, through the development of RTES, until the system realization.