**UNIVERSIDADE FEDERAL DE UBERLÂNDIA**

FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

**PROJETO E ANÁLISE DE DESEMPENHO DE UM

INVERSOR FULL-BRIDGE EMPREGADO EM UM

SISTEMA UPS ON-LINE COM ELEVADO FATOR DE

POTÊNCIA**

**AUGUSTO MENDES DA COSTA**

Uberlândia - MG

2019

# **UNIVERSIDADE FEDERAL DE UBERLÂNDIA**

**FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA**

## **PROJETO E ANÁLISE DE DESEMPENHO DE UM INVERSOR FULL-BRIDGE EMPREGADO EM UM SISTEMA UPS ON-LINE COM ELEVADO FATOR DE POTÊNCIA**

**AUGUSTO MENDES DA COSTA**

Dissertação de Mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), perante a banca de examinadores abaixo, como parte dos requisitos necessários para a obtenção do título de mestre em Ciências.

Área de concentração: Sistema de energia elétrica.

Orientador: Dr. Luiz Carlos Gomes de Freitas.

Coorientador: Dr. João Batista Vieira Júnior.

Banca Examinadora:

Prof. Dr. Admarço Vieira Costa (CEFET-Araxá)

Prof. Dr. Gustavo Brito de Lima (UFU)

Prof. Dr. Luiz Carlos Gomes de Freitas (UFU)

A Bolsa de Estudos para esta pesquisa foi concedida pela CAPES – Brasil.

Uberlândia - MG

2019

**Dados Internacionais de Catalogação na Publicação (CIP)**

**Sistema de Bibliotecas da UFU, MG, Brasil.**

---

C837p

2019

Costa, Augusto Mendes da, 1992-

Projeto e análise de desempenho de um inversor Full-Bridge empregado em um sistema UPS on-line com elevado fator de potência [recurso eletrônico] / Augusto Mendes da Costa. - 2019.

Orientador: Luiz Carlos Gomes de Freitas.

Coorientador: João Batista Vieira Júnior.

Dissertação (mestrado) - Universidade Federal de Uberlândia, Programa de Pós-Graduação em Engenharia Elétrica.

Modo de acesso: Internet.

Disponível em: <http://dx.doi.org/10.14393/ufu.di.2019.20>

Inclui bibliografia.

Inclui ilustrações.

1. Engenharia Elétrica. 2. Sistemas ininterruptos de energia. 3. Fator de potência. 4. Inversores elétricos. 5. Conversores de energia. 6. Processamento de sinais. I. Freitas, Luiz Carlos Gomes de, 1976-, (Orient.). II. Vieira Júnior, João Batista, 1955-, (Coorient.). III. Universidade Federal de Uberlândia. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

CDU: 621.3

---

Rejâne Maria da Silva – CRB6/1925

*Aos meus pais Fabiene e Roberto,

ao meu irmão Edgar,

à minha namorada Andressa,

e à minha família e amigos.*

# AGRADECIMENTOS

Primeiramente, agradeço a Deus pela oportunidade, por colocar tantas pessoas especiais em meu caminho e pela força fornecida nos momentos difíceis, para nunca desistir.

Ao professor orientador Luiz Carlos Gomes de Freitas e ao Doutor Renato Santiago Maciel, que se tornaram grandes amigos durante estes anos de convivência e que desde a época de iniciação científica, acreditaram em minha capacidade e muito me ensinaram. Obrigado pela dedicação, ensinamentos, competência e especial atenção nas revisões e sugestões, fatores fundamentais para a conclusão deste e outros trabalhos.

Aos meus pais Fabiene e Roberto, pelo carinho, amor, pelos sacrifícios e renúncias realizados ao longo da minha vida para me proporcionar uma boa formação acadêmica. Sua preocupação especial é que me faz ser um cidadão honesto e do bem. Ao meu irmão Edgar, que muito torceu por essa vitória e tantas outras, e também pelos puxões de orelha.

À minha namorada Andressa, por ter me apoiado e acompanhado durante quase toda essa trajetória, sempre me apoioando. Obrigado pelo amor, carinho, compreensão, conselhos, dedicação e por me fazer um homem melhor.

A todos meus amigos do laboratório Renato, Antônio, Lucas, Fernando, entre outros. Todas as trocas de conhecimento foram uma das maiores fontes de aprendizado nestes anos.

A todos os amigos e familiares que contribuíram direta ou indiretamente na realização desse trabalho, incentivando e torcendo por sua conclusão.

Ao CNPq – Conselho Nacional de Desenvolvimento Científico e Tecnológico, à FAPEMIG - Fundação de Amparo à Pesquisa do Estado de Minas Gerais e à CAPES - Coordenação de Aperfeiçoamento de Pessoal de Nível Superior, pelo suporte financeiro para construção e análise experimental do protótipo e publicação.

*É melhor você tentar algo,

vê-lo não funcionar e aprender com isso,

do que não fazer nada.*

*Mark Zuckerberg*

# RESUMO

*O presente trabalho de dissertação apresenta o estudo, a metodologia de projeto e a implementação prática de um inversor Full-Bridge empregado em um sistema UPS do tipo on-line. Este possui como estágio de entrada o conversor Boost SR-ZCS-ZVS-PWM e tem a vantagem de integrar as funções de um conversor pré-regulador com correção do fator de potência (CFP) e de um conversor CC-CC elevador. Para controle do inversor Full-bridge utilizou-se a técnica denominada de modulação bipolar em malha aberta, a qual foi implementada no mesmo DSP (Digital Signal Processor) empregado para realização da correção do fator de potência do estágio de entrada supracitado. A tensão de saída é puramente senoidal, dentro dos critérios estabelecidos pela norma IEC 63040-3. Os resultados experimentais alcançados são apresentados e corroboram com teoria exposta.*

**Palavras-chave:** Conversor Boost, Inversor, Fator de potência, Sistema Ininterrupto de Suprimento de Energia.

# ABSTRACT

The present work of dissertation presents the study, the methodology of design and the practical implementation of a Full-Bridge inverter employed in an on-line type UPS system. The Boost SR-ZCS-ZVS-PWM converter, which is the input stage of the UPS system, has the advantage of integrating the functions of a pre-regulating converter with power factor correction (PFC) and a DC-DC converter. In order to control the Full-bridge inverter, the the so-called open-loop bipolar modulation technique was used, which was implemented in the same DSP (Digital Signal Processor) used to perform the power factor correction of the above-mentioned input stage. The output voltage is pure sinusoidal, within the criteria established by IEC 63040-3. The experimental results are presented and corroborate with the theory exposed.

**Keywords:** Boost converter, Inverter, Power Factor Correction, Uninterrupted Power Supply.

# LISTA DE FIGURAS

|                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1.1 – Estrutura Genérica Sistema UPS.....                                                                                                                      | 21 |

| Figura 2.1 – Diagrama de blocos de um sistema UPS <i>On-line</i> típico .....                                                                                         | 24 |

| Figura 2.2 – Conversor CC-CA em ponte completa (Full-Bridge) .....                                                                                                    | 25 |

| Figura 2.3 – Conversor CC-CA em meia ponte .....                                                                                                                      | 26 |

| Figura 2.4 – Conversor CC-CA <i>Push-Pull</i> .....                                                                                                                   | 27 |

| Figura 2.5 – Conversores CA-CC e CC-CA em ponte completa. ....                                                                                                        | 29 |

| Figura 2.6 – Conversores CA-CC e CC-CA em meia ponte .....                                                                                                            | 29 |

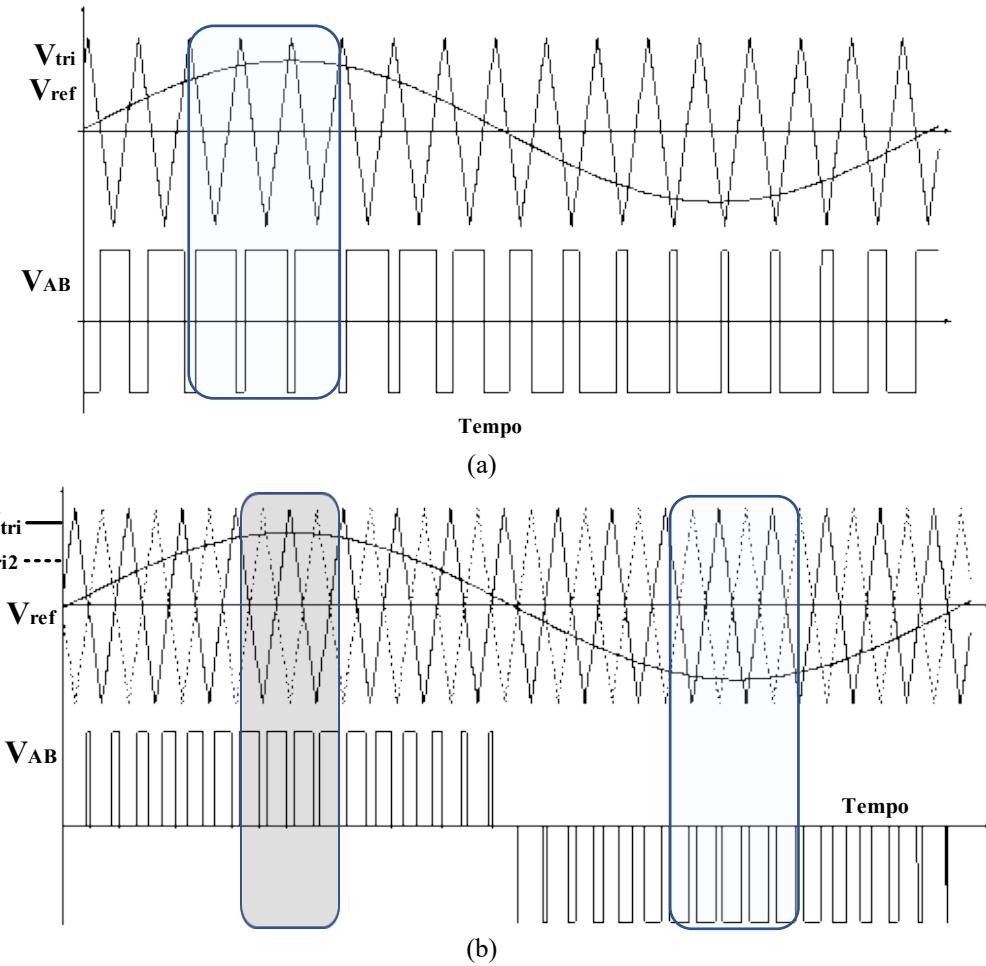

| Figura 2.7 – (a) PWM senoidal bipolar. (b) PWM senoidal unipolar .....                                                                                                | 32 |

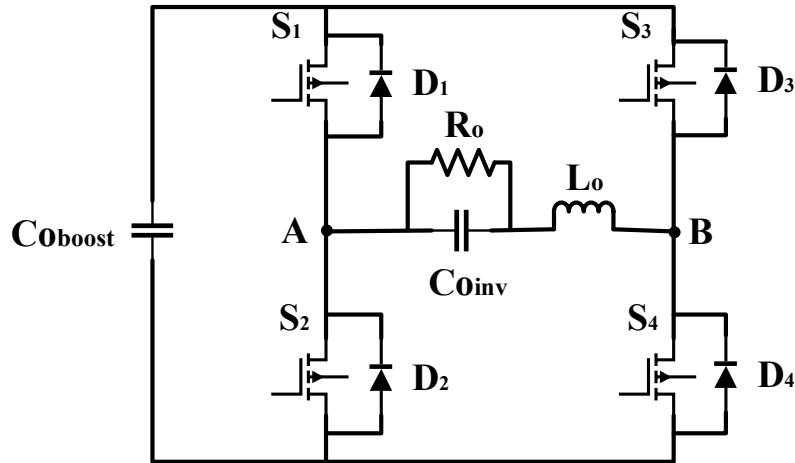

| Figura 2.8 – Circuito simplificado do inversor Full-Bridge.....                                                                                                       | 34 |

| Figura 2.9 – Modulação PWM senoidal bipolar.....                                                                                                                      | 35 |

| Figura 2.10 – Circuito da primeira etapa de operação do inversor ( $t_0 - t_1$ ). .....                                                                               | 35 |

| Figura 2.11 – Circuito da segunda etapa de operação do inversor ( $t_1 - t_2$ ). .....                                                                                | 36 |

| Figura 2.12 – Circuito da terceira etapa de operação do inversor ( $t_2 - t_3$ ).....                                                                                 | 36 |

| Figura 2.13 – Circuito da quarta etapa de operação do inversor ( $t_3 - t_4$ ).....                                                                                   | 37 |

| Figura 2.14 – Forma de onda da tensão $V_{AB}$ para modulação bipolar.....                                                                                            | 37 |

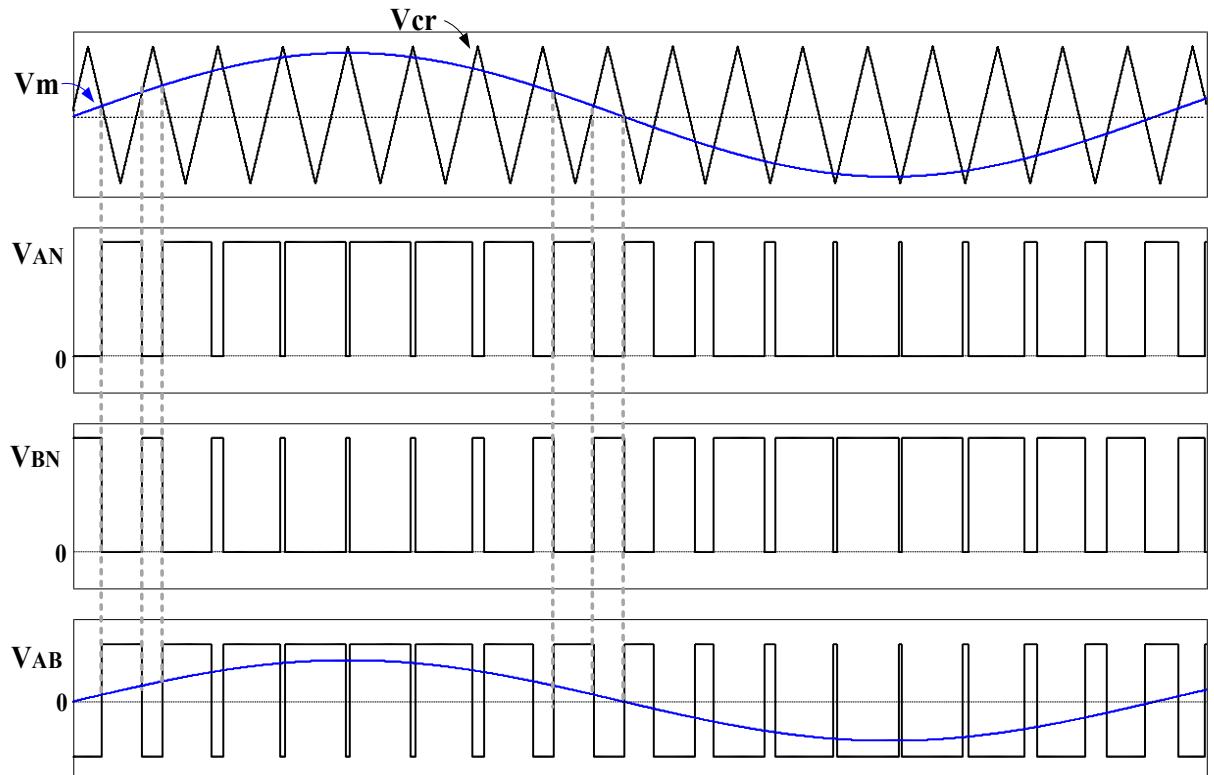

| Figura 2.15 – Modulação PWM senoidal unipolar.....                                                                                                                    | 38 |

| Figura 2.16 – Primeira etapa de funcionamento do inversor para o semiciclo positivo.....                                                                              | 40 |

| Figura 2.17 – Segunda etapa de funcionamento do inversor para o semiciclo positivo.....                                                                               | 40 |

| Figura 2.18 – Terceira etapa de funcionamento do inversor para o semiciclo positivo. ....                                                                             | 41 |

| Figura 2.19 – Quarta etapa de funcionamento do inversor para o semiciclo positivo. ....                                                                               | 41 |

| Figura 2.20 – Primeira etapa de funcionamento do inversor para o semiciclo negativo.....                                                                              | 42 |

| Figura 2.21 – Segunda etapa de funcionamento do inversor para o semiciclo negativo.....                                                                               | 43 |

| Figura 2.22 – Terceira etapa de funcionamento do inversor para o semiciclo negativo .....                                                                             | 43 |

| Figura 2.23 – Quarta etapa de funcionamento do inversor para o semiciclo negativo.....                                                                                | 44 |

| Figura 2.24 – Forma de onda da tensão $V_{AB}$ para modulação unipolar.....                                                                                           | 44 |

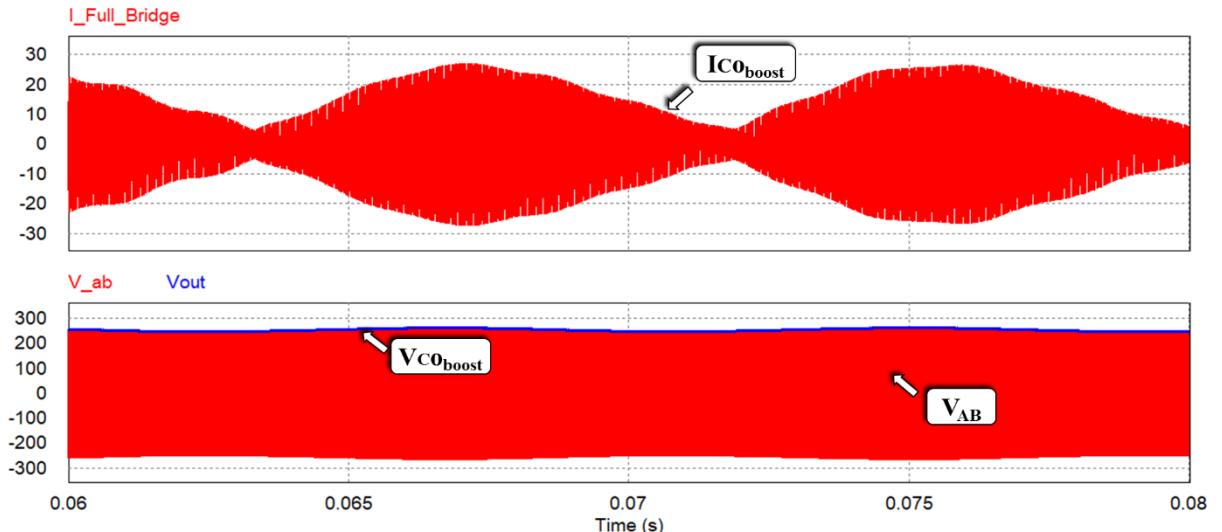

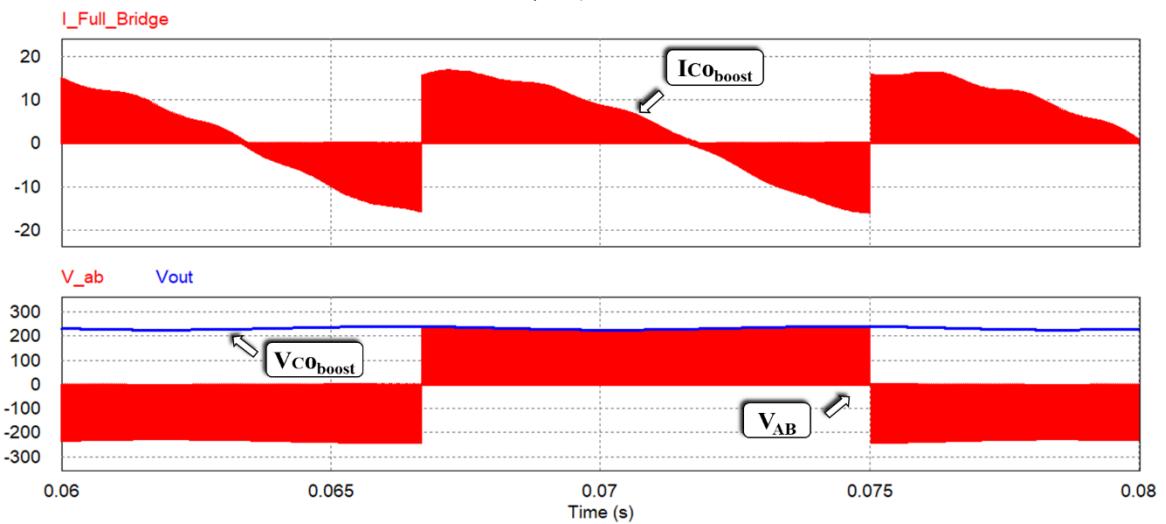

| Figura 2.25 – Formas de onda para modulação bipolar da corrente ( $IC_{boost}$ ) e tensão ( $VC_{boost}$ )<br>do pré-regulador e tensão ( $V_{AB}$ ) do inversor..... | 45 |

| Figura 2.26 – Zoom das formas de onda para modulação bipolar .....                                                                                                    | 45 |

|                                                                                                                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

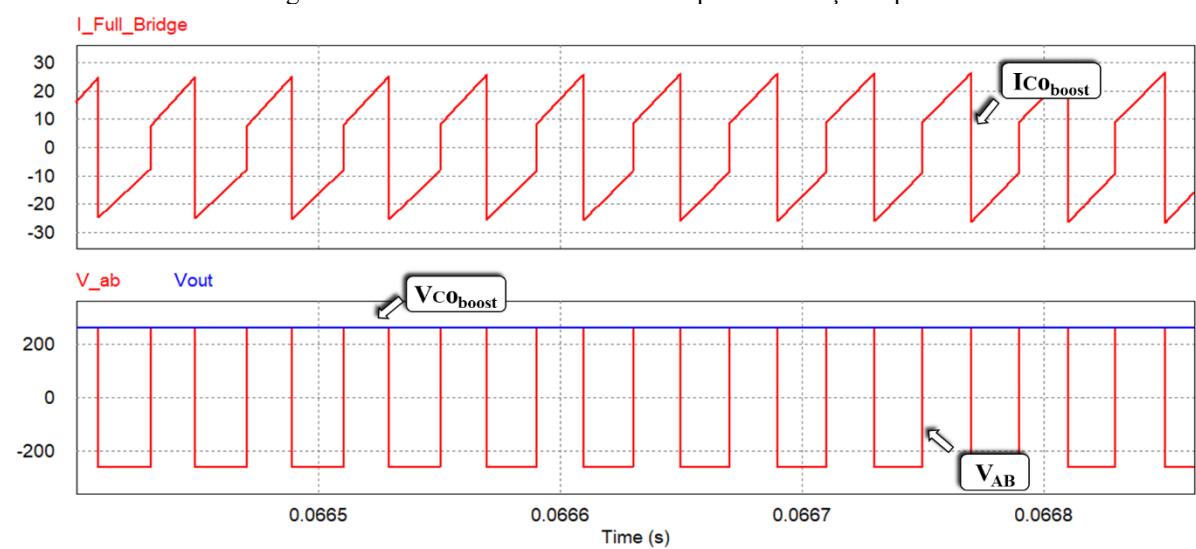

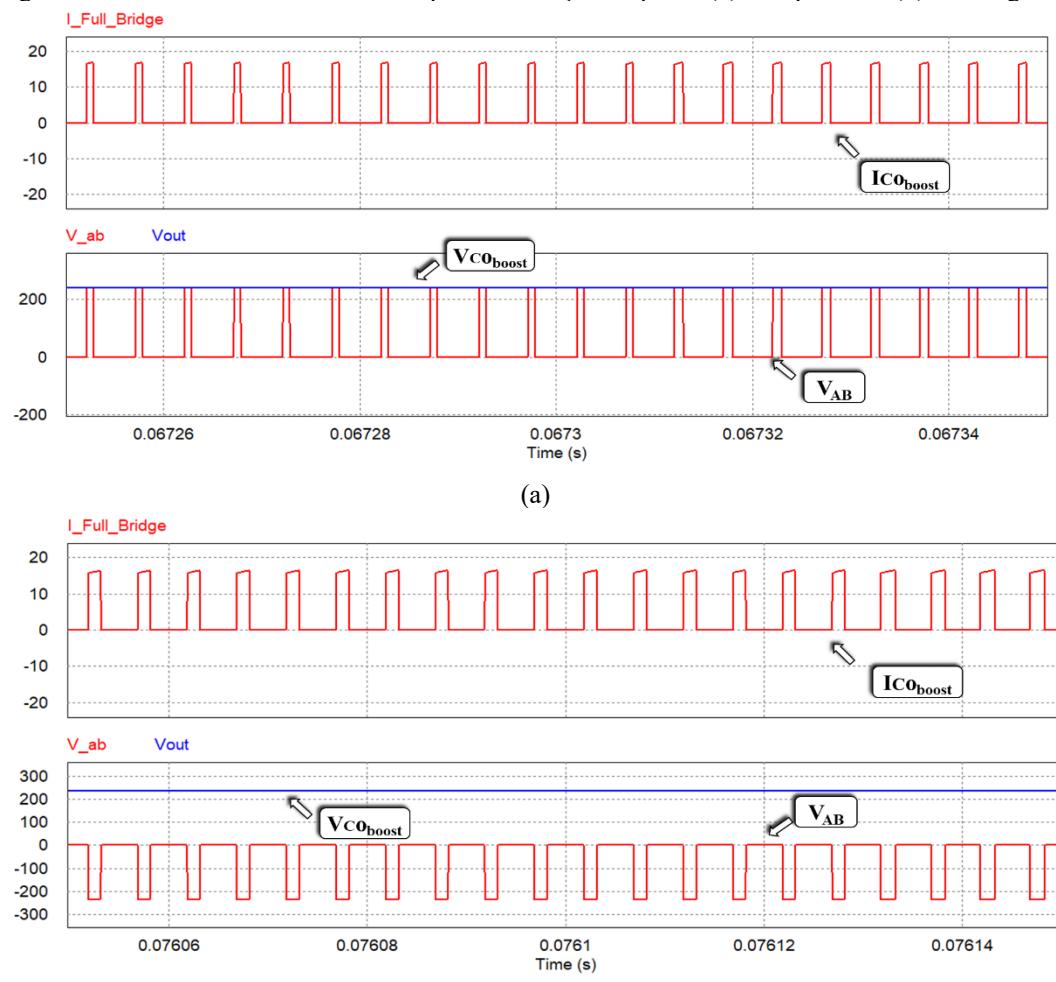

| Figura 2.27 – Formas de onda para modulação unipolar da corrente ( $IC_{boost}$ ) e tensão ( $VC_{boost}$ ) do pré-regulador e tensão ( $V_{AB}$ ) do inversor.....                                                                       | 46 |

| Figura 2.28 – Zoom das formas de onda para modulação unipolar. (a) $V_{AB}$ positivo. (b) $V_{AB}$ negativo .....                                                                                                                         | 46 |

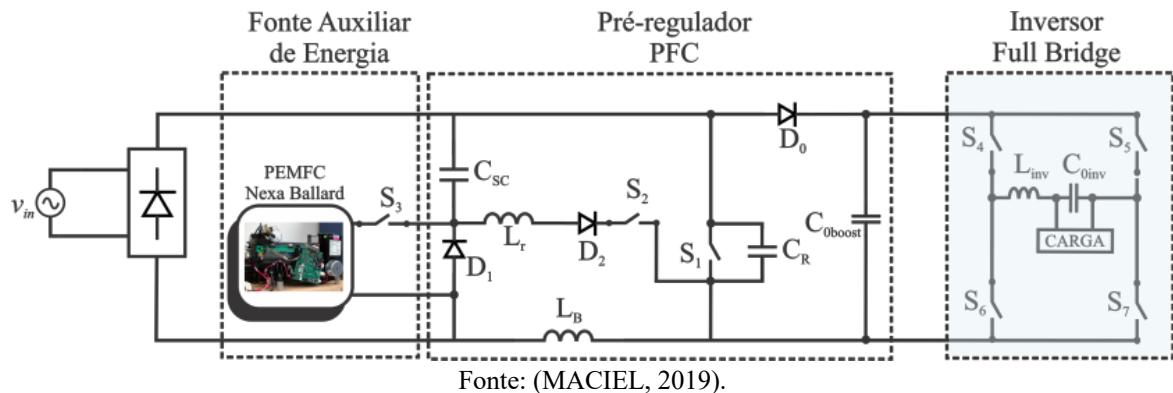

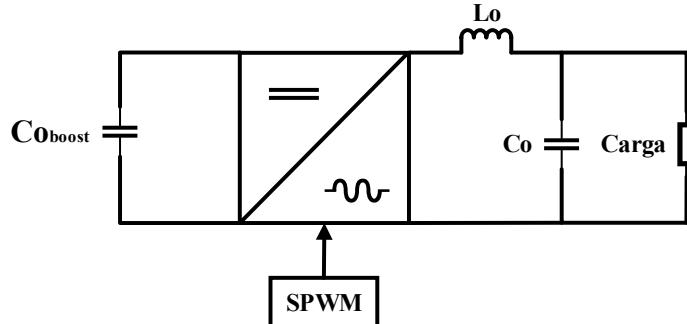

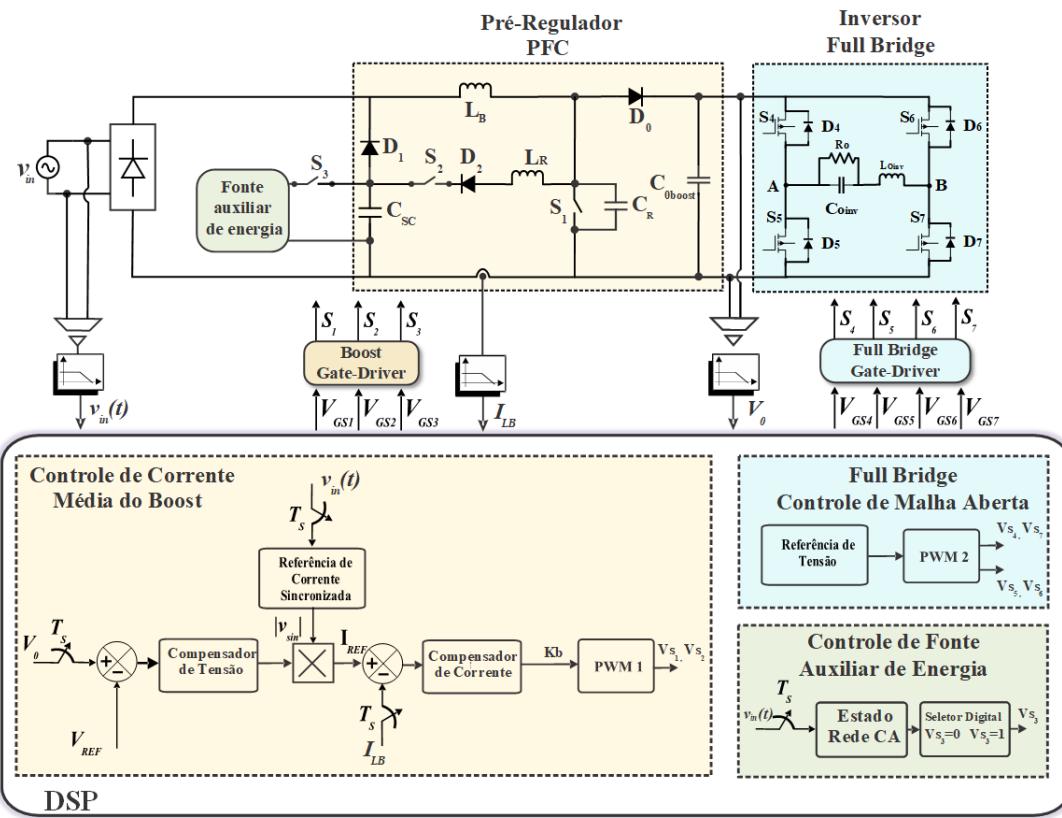

| Figura 3.1 – Sistema UPS <i>On-line</i> Proposto .....                                                                                                                                                                                    | 48 |

| Figura 3.2 - Circuito <i>snubber</i> .....                                                                                                                                                                                                | 65 |

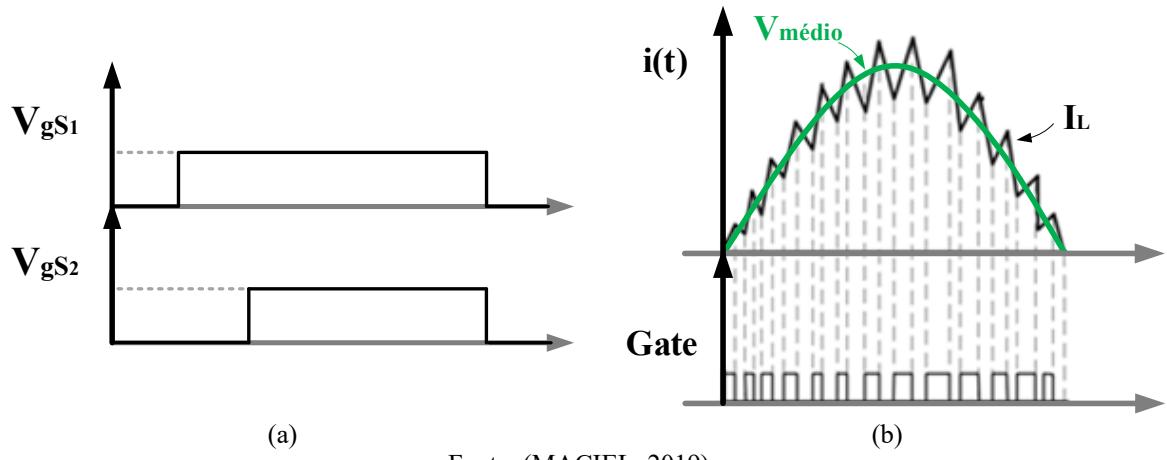

| Figura 4.1 – (a) Sinais PWM de controle. (b) Método e controle da corrente média .....                                                                                                                                                    | 68 |

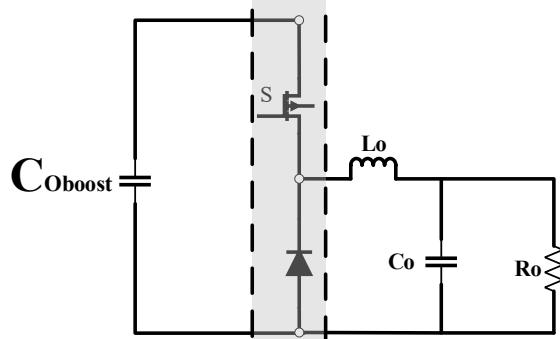

| Figura 4.2 – Circuito simplificado do inversor de tensão.....                                                                                                                                                                             | 69 |

| Figura 4.3 – Circuito do conversor Buck, equivalente ao Conversor Full-Bridge.....                                                                                                                                                        | 69 |

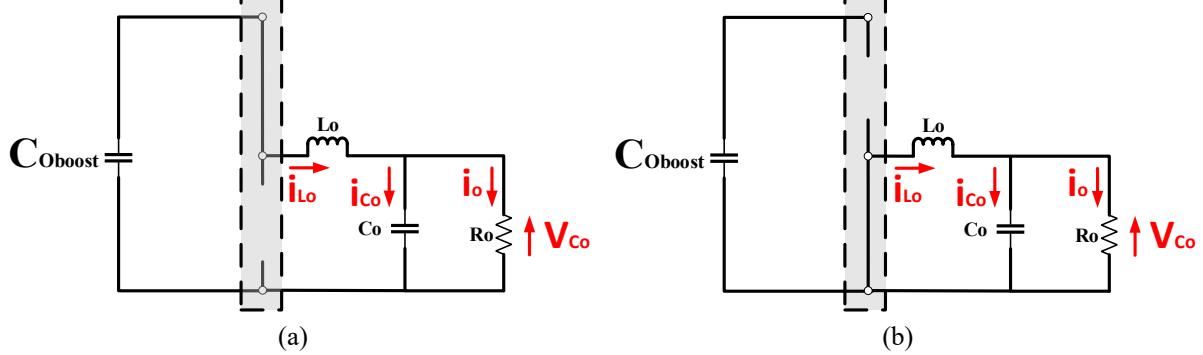

| Figura 4.4 – (a) Chave S1 conduzindo ( $T_{ON}$ ). (b) Chave S1 bloqueada ( $T_{OFF}$ ).....                                                                                                                                              | 70 |

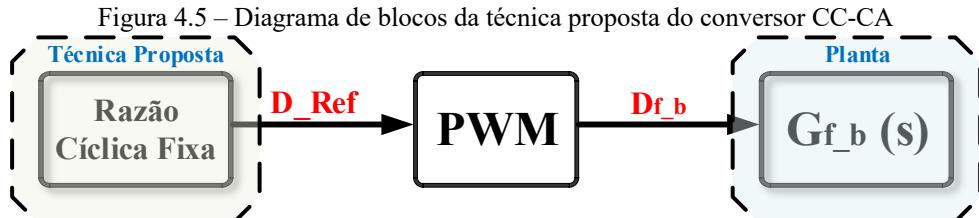

| Figura 4.5 – Diagrama de blocos da técnica proposta do conversor CC-CA.....                                                                                                                                                               | 76 |

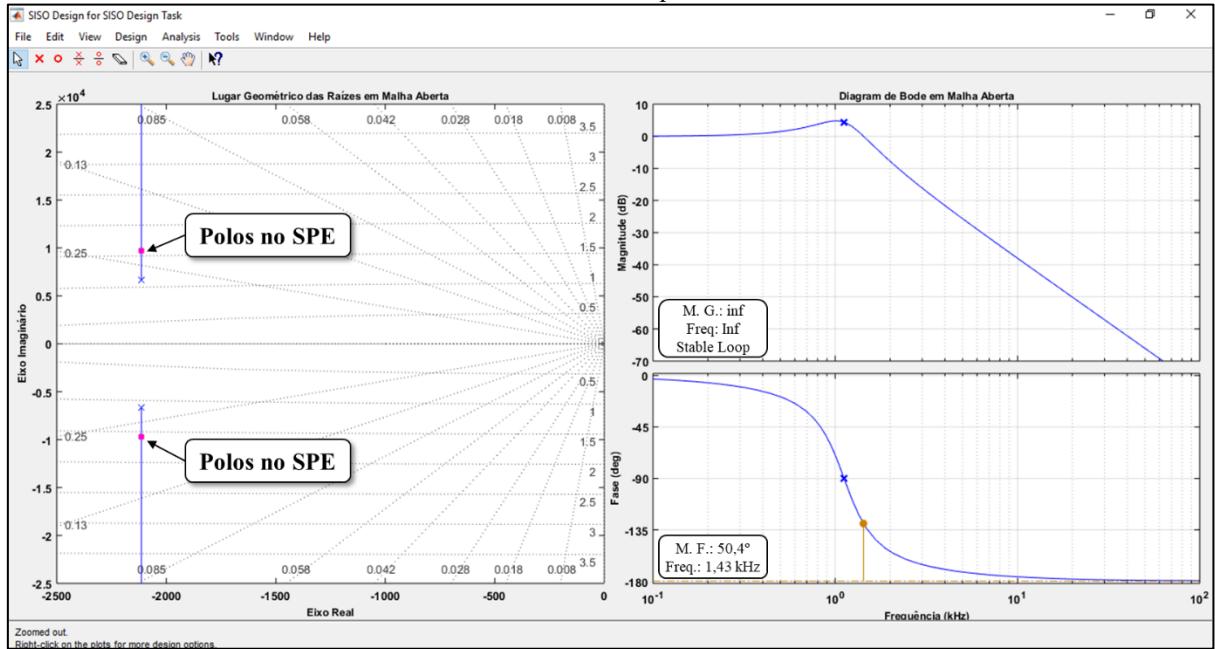

| Figura 4.6 – Lugar geométrico das raízes e Diagrama de Bode em malha aberta da função de transferência do Inversor não compensada .....                                                                                                   | 77 |

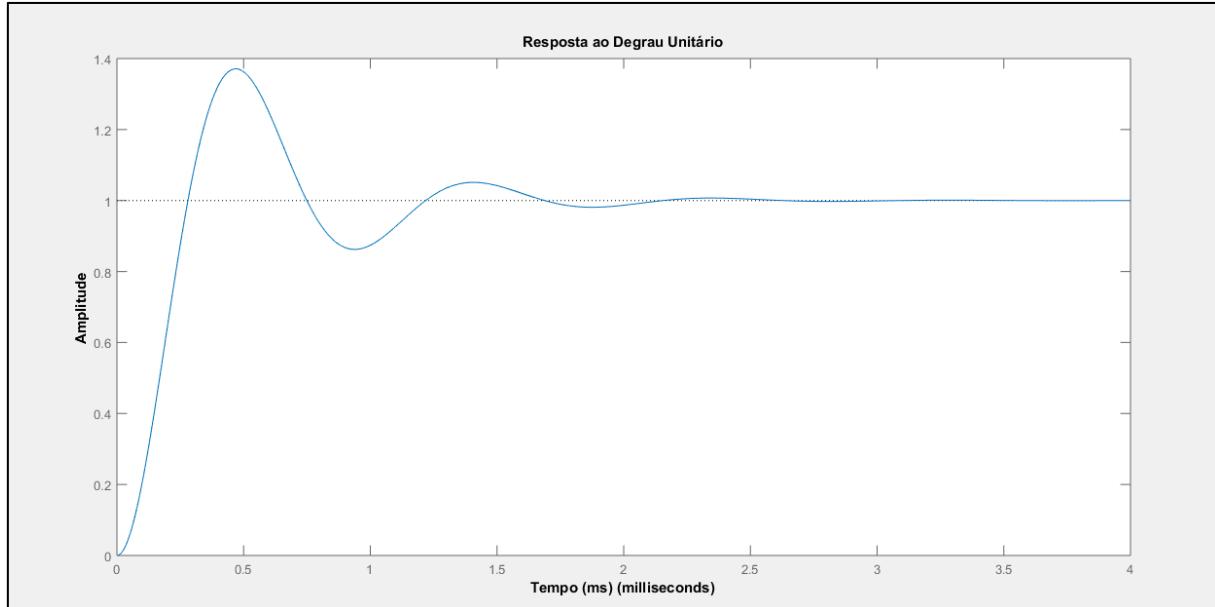

| Figura 4.7 – Resposta ao degrau unitário da função de transferência do conversor Boost não compensada .....                                                                                                                               | 77 |

| Figura 4.8 - Diagrama esquemático do sistema de controle.....                                                                                                                                                                             | 79 |

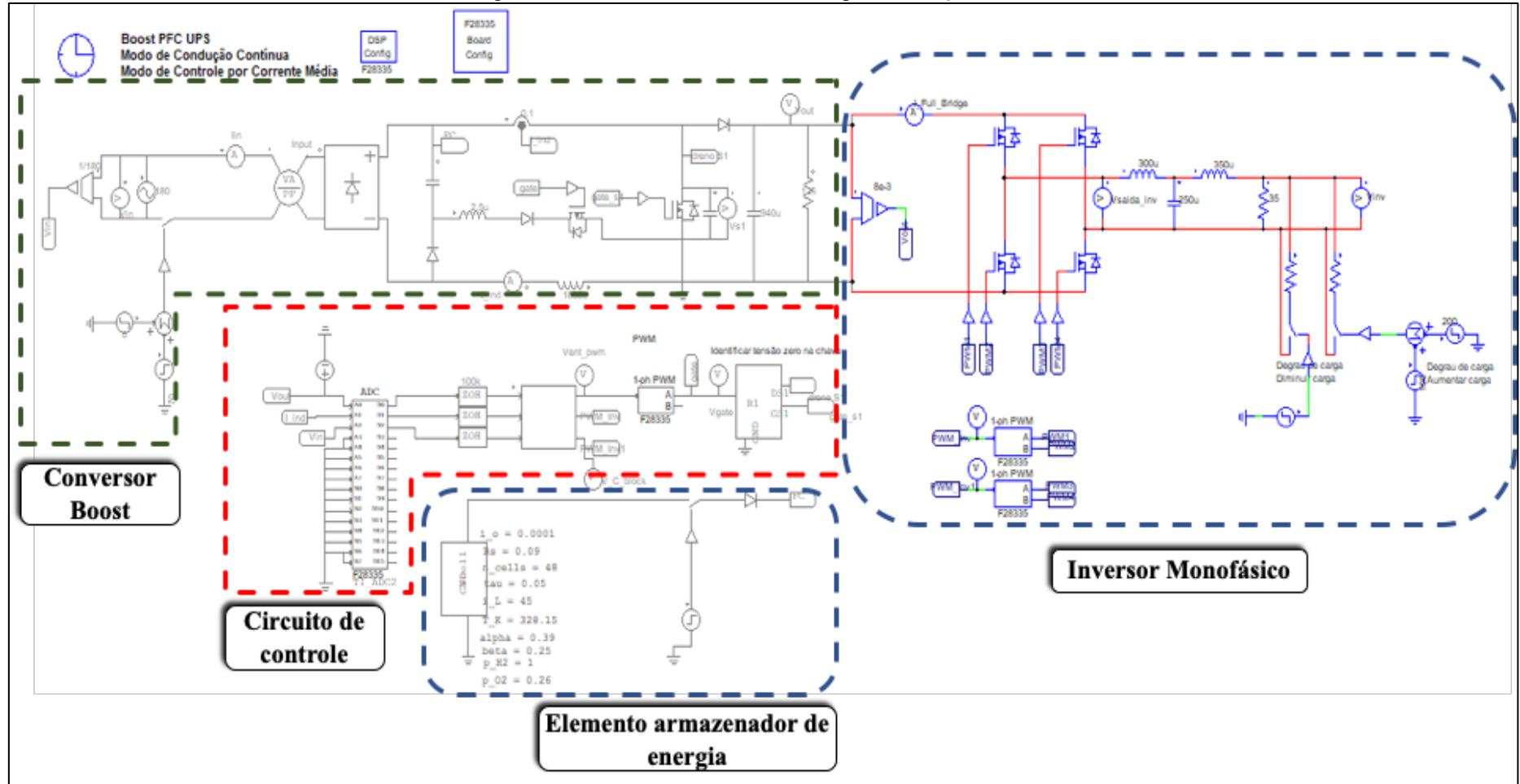

| Figura 5.1 – Circuito montado no PSIM® para simulação do UPS.....                                                                                                                                                                         | 81 |

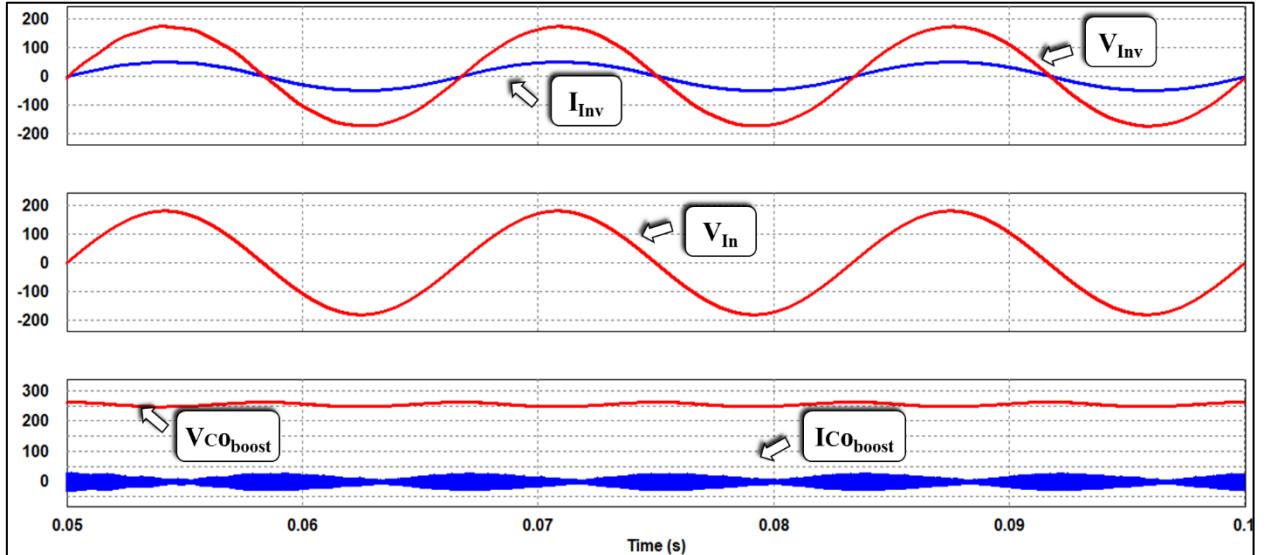

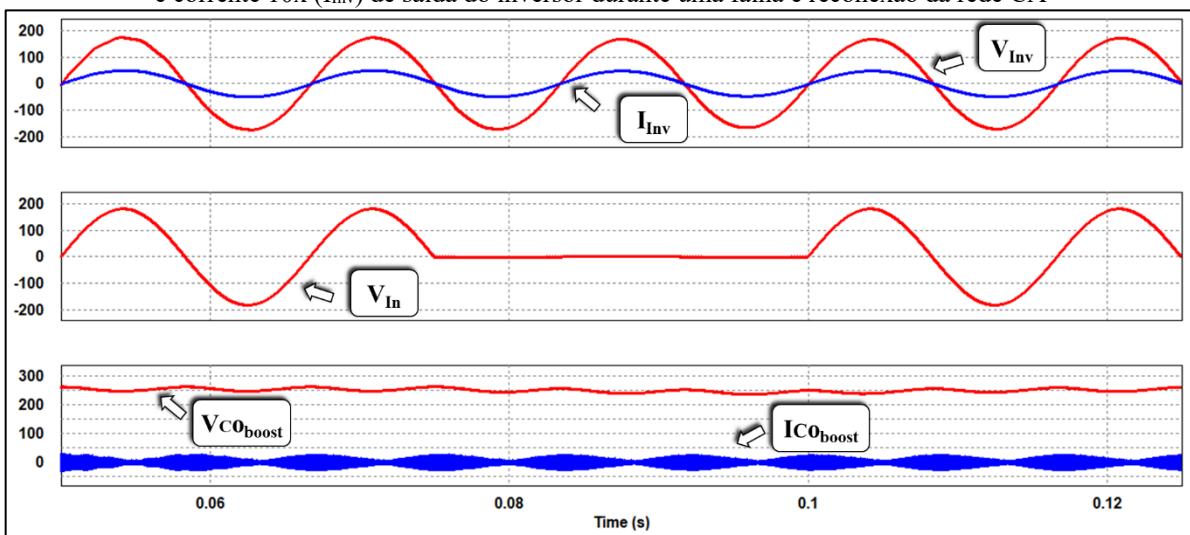

| Figura 5.2 – Formas de onda nominal da tensão de entrada ( $V_{In}$ ), tensão ( $VC_{boost}$ ) do pré-regulador, e tensão ( $V_{Inv}$ ) e corrente 10x ( $I_{Inv}$ ) de saída do inversor .....                                           | 82 |

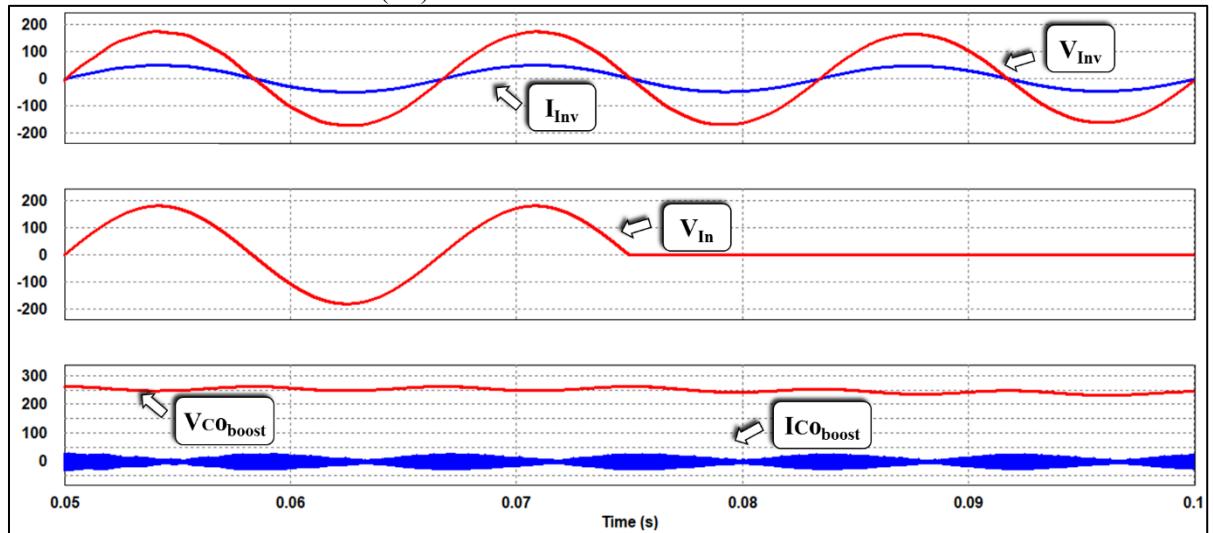

| Figura 5.3 – Formas de ondas da tensão de entrada ( $V_{In}$ ), tensão do pré-regulador ( $VC_{boost}$ ), tensão ( $V_{Inv}$ ) e corrente 10x ( $I_{Inv}$ ) de saída do inversor durante uma falha da rede CA .....                       | 82 |

| Figura 5.4 – Formas de onda nominal da tensão de entrada ( $V_{In}$ ), tensão ( $VC_{boost}$ ) do pré-regulador, tensão ( $V_{Inv}$ ) e corrente 10x ( $I_{Inv}$ ) de saída do inversor durante uma falha da rede CA.....                 | 83 |

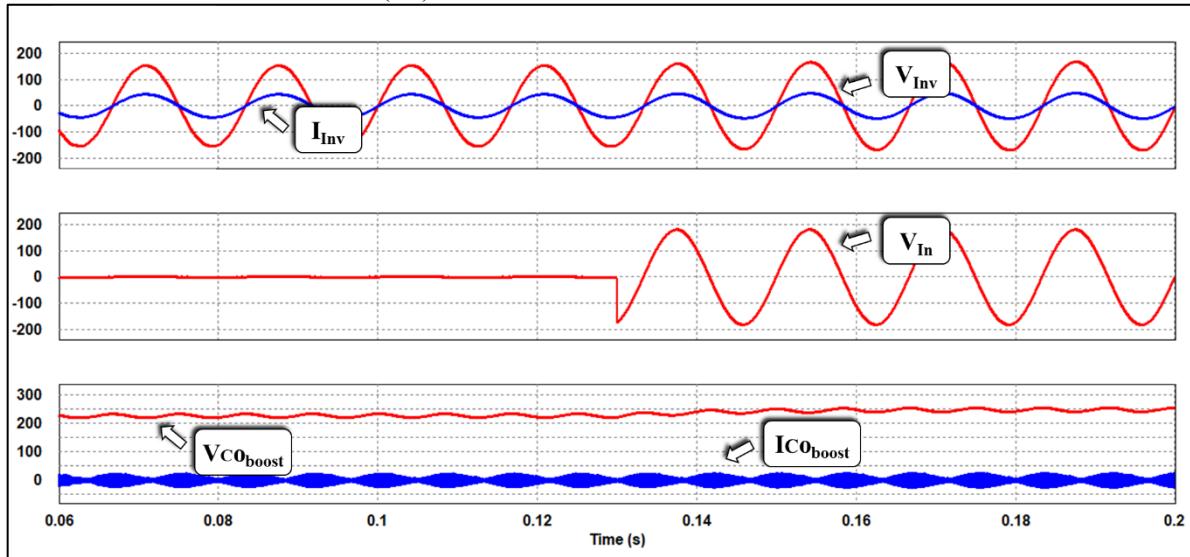

| Figura 5.5 – Formas de onda nominal da tensão de entrada ( $V_{In}$ ), tensão ( $VC_{boost}$ ) do pré-regulador, tensão ( $V_{Inv}$ ) e corrente 10x ( $I_{Inv}$ ) de saída do inversor durante uma falha e reconexão da rede CA .....    | 83 |

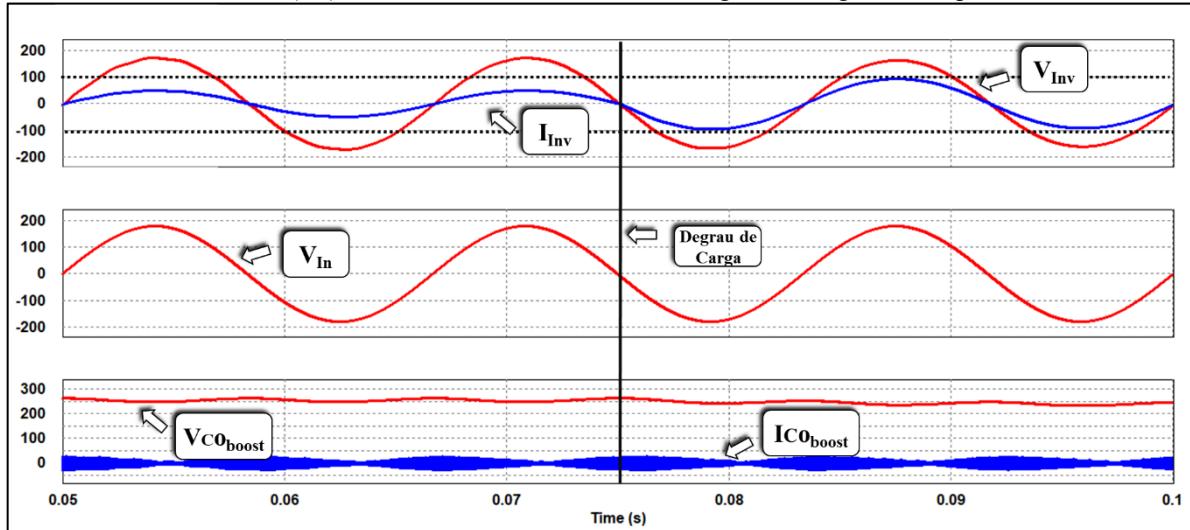

| Figura 5.6 – Formas de onda nominal da tensão de entrada ( $V_{In}$ ), tensão ( $VC_{boost}$ ) do pré-regulador, tensão ( $V_{Inv}$ ) e corrente 10x ( $I_{Inv}$ ) de saída do inversor durante um degrau de carga de 50% para 100% ..... | 84 |

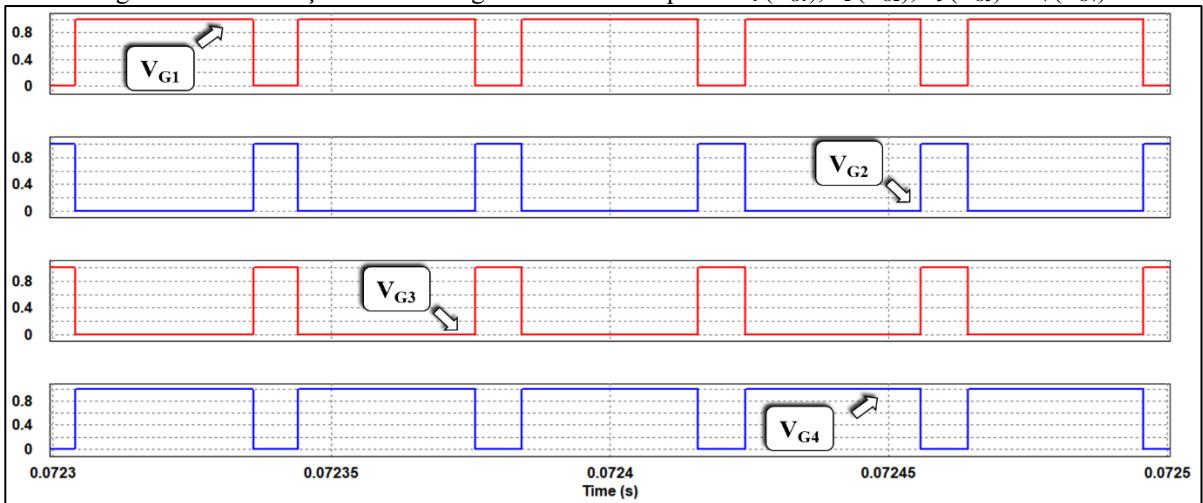

| Figura 5.7 – Simulação do sinal de gatilho dos interruptores $S1$ ( $VG1$ ), $S2$ ( $VG2$ ), $S3$ ( $VG3$ ) e $S4$ ( $VG4$ ).....                                                                                                         | 84 |

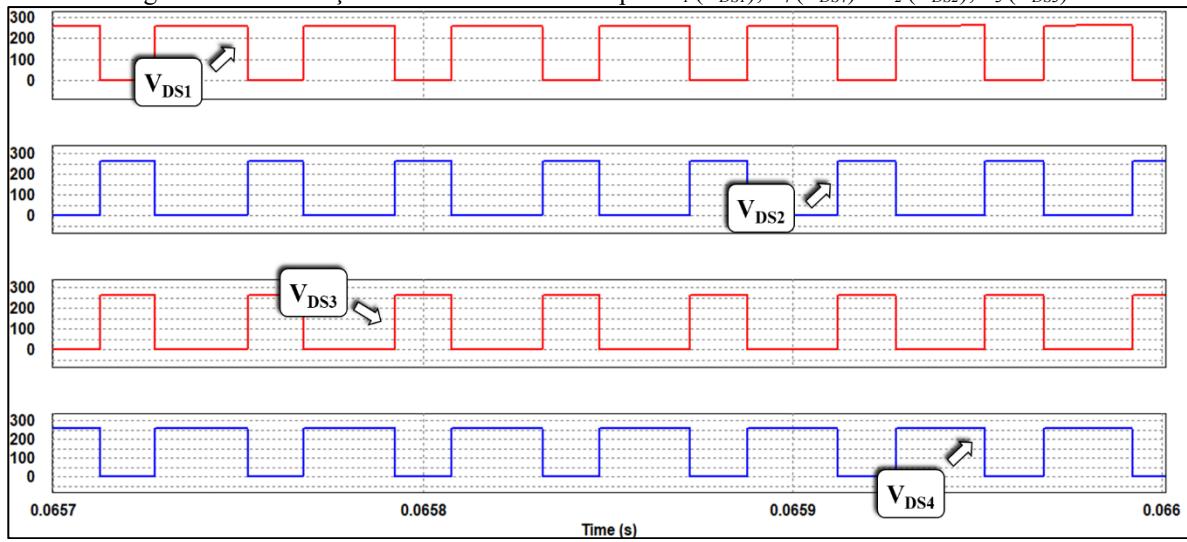

| Figura 5.8 – Simulação das tensões dos interruptor $S1$ ( $VDS1$ ), $S4$ ( $VDS4$ ) e $S2$ ( $VDS2$ ), $S3$ ( $VDS3$ ).....                                                                                                               | 85 |

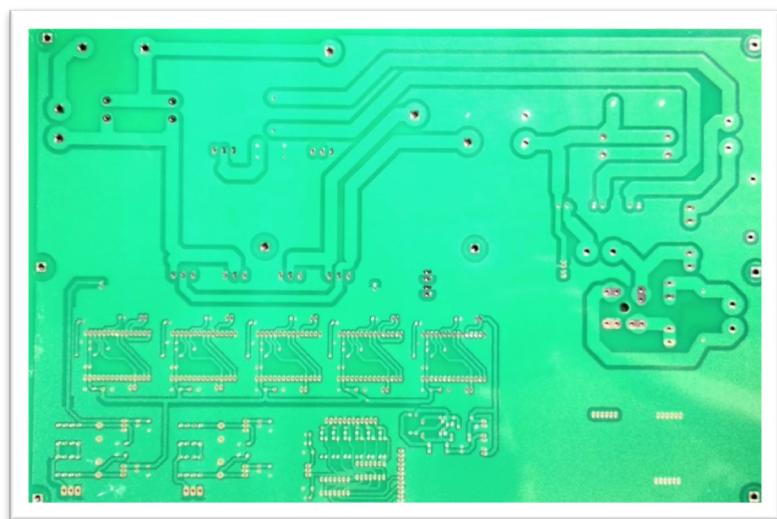

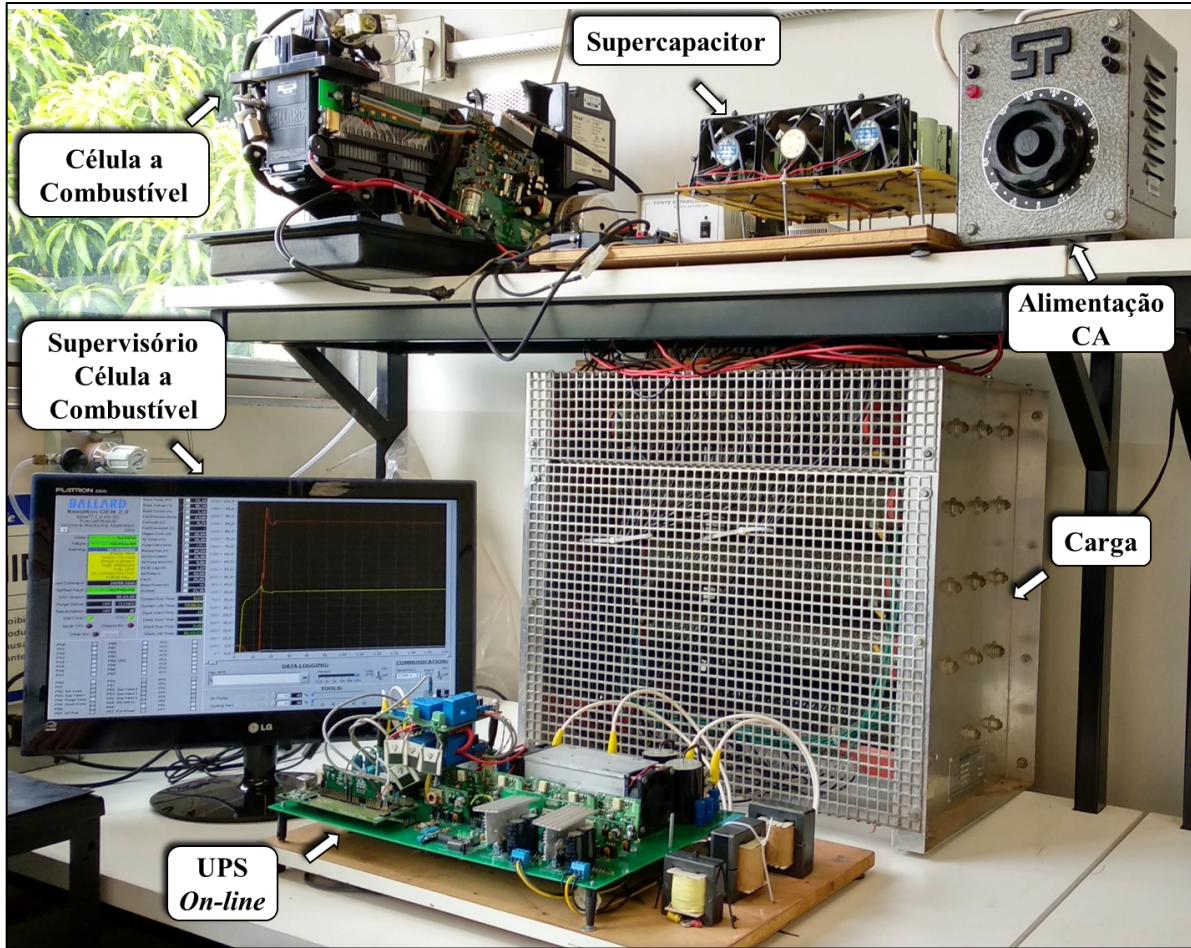

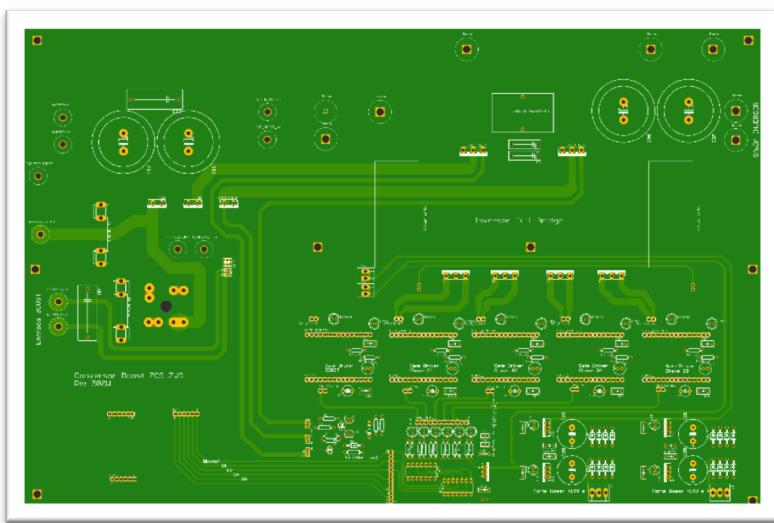

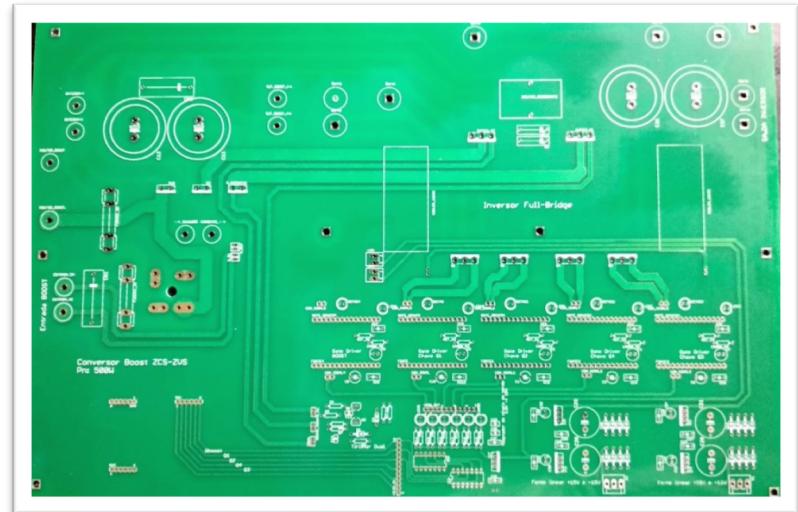

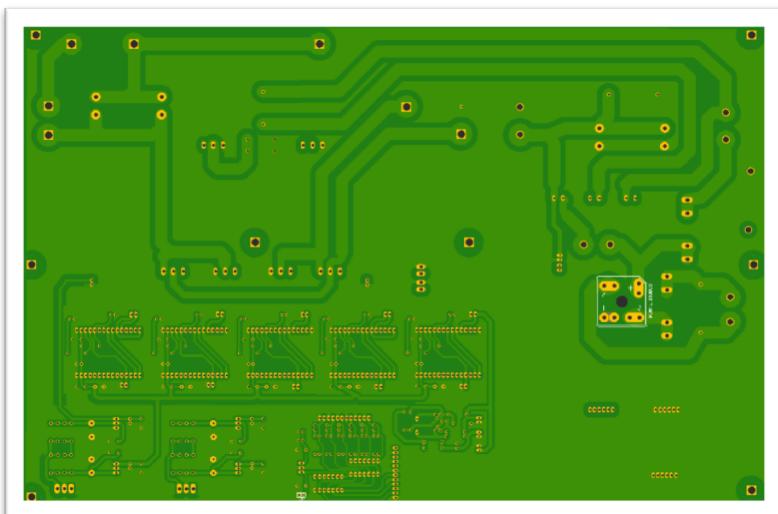

| Figura 5.9 – Protótipo do sistema UPS <i>On-line</i> .....                                                                                                                                                                                | 86 |

|                                                                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

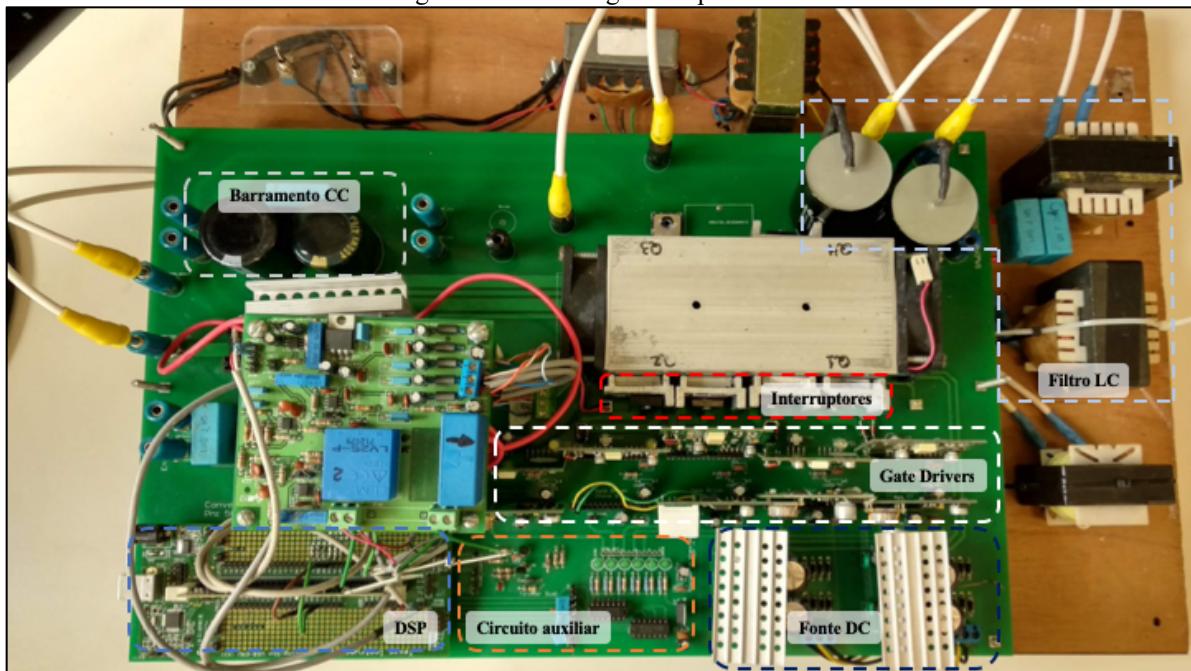

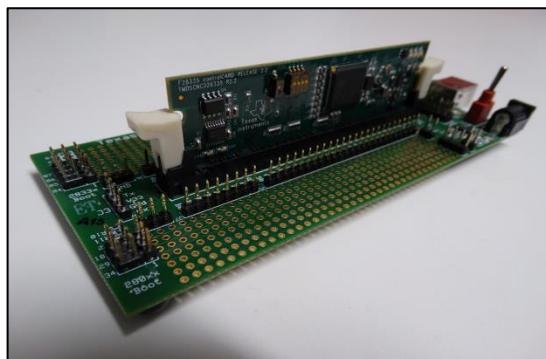

| Figura 5.10 – Vista geral da placa UPS.....                                                                                                                                                         | 86 |

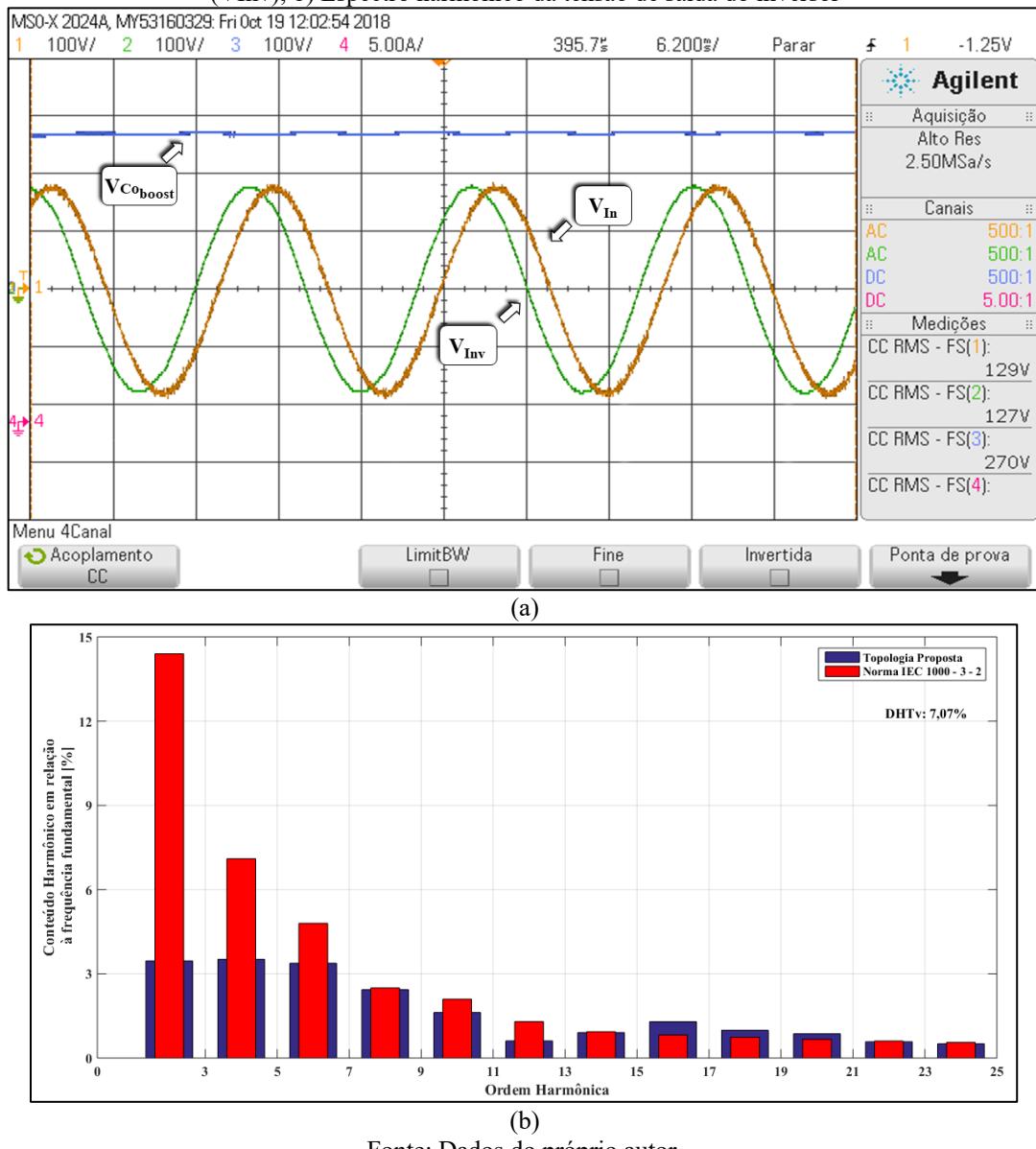

| Figura 5.11 – a) Tensão de entrada ( $V_{In}$ ), tensão do barramento CC ( $VC_{boost}$ ) e tensão de saída do inversor ( $V_{Inv}$ ); b) Espectro harmônico da tensão de saída do inversor .....   | 89 |

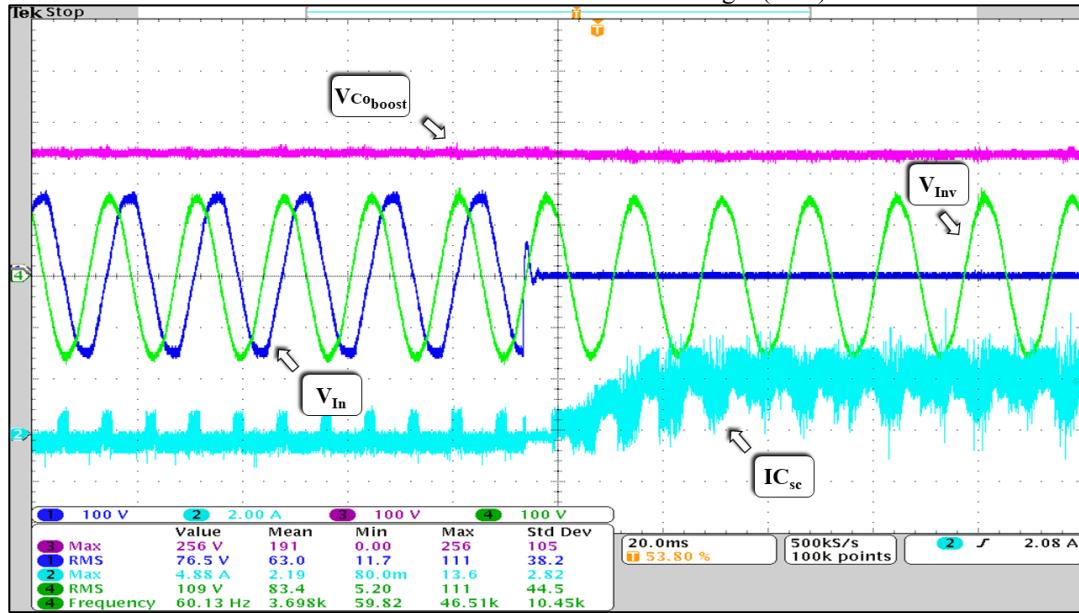

| Figura 5.12 – Tensão de entrada ( $V_{In}$ ), tensão do barramento CC ( $VC_{boost}$ ), tensão de saída do inversor ( $V_{Inv}$ ) e corrente do elemento armazenador de energia ( $IC_{sc}$ ) ..... | 90 |

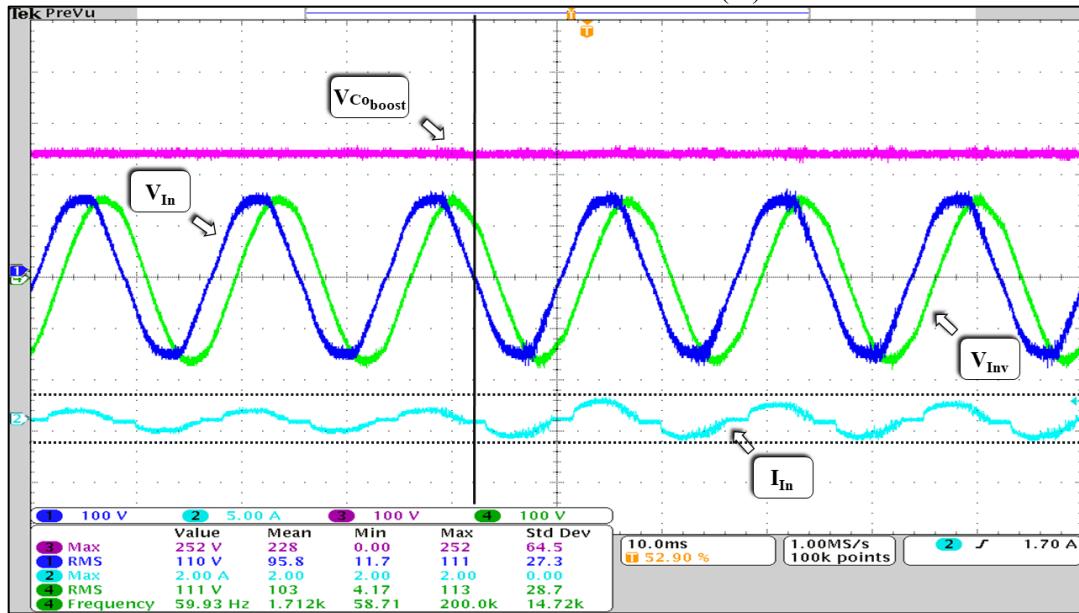

| Figura 5.13 – Tensão de entrada ( $V_{In}$ ), tensão do barramento CC ( $VC_{boost}$ ), tensão de saída do inversor ( $V_{Inv}$ ) e corrente de entrada do sistema UPS ( $I_{In}$ ).....            | 90 |

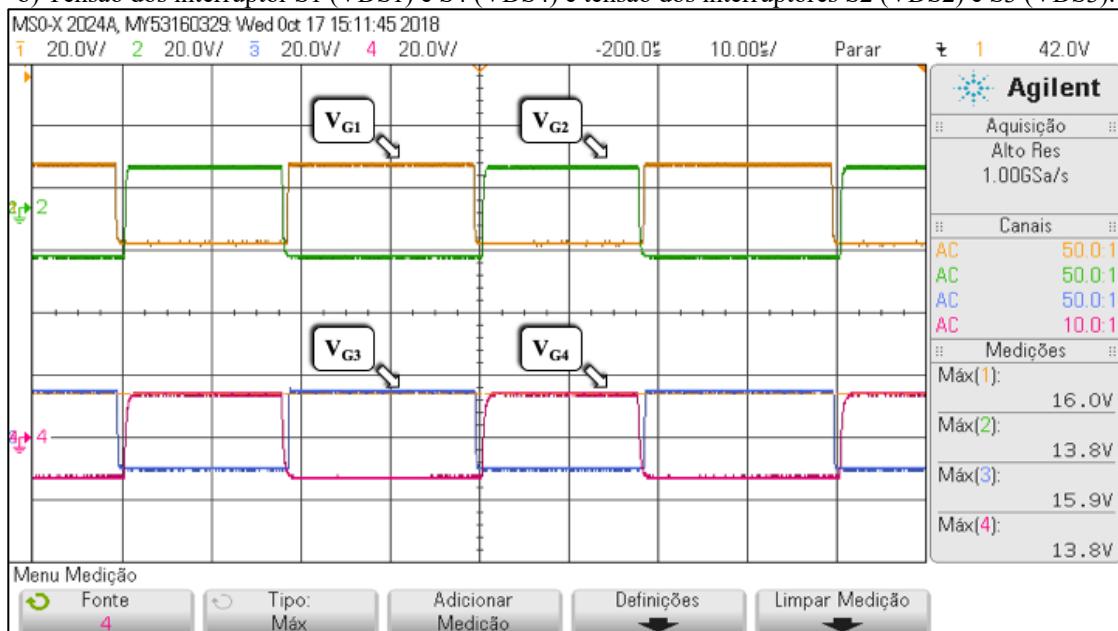

| Figura 5.14 – a) Sinal de gatilho dos interruptores S1 (VG1), S2 (VG2), S3 (VG3) e S4 (VG4).<br>.....                                                                                               | 91 |

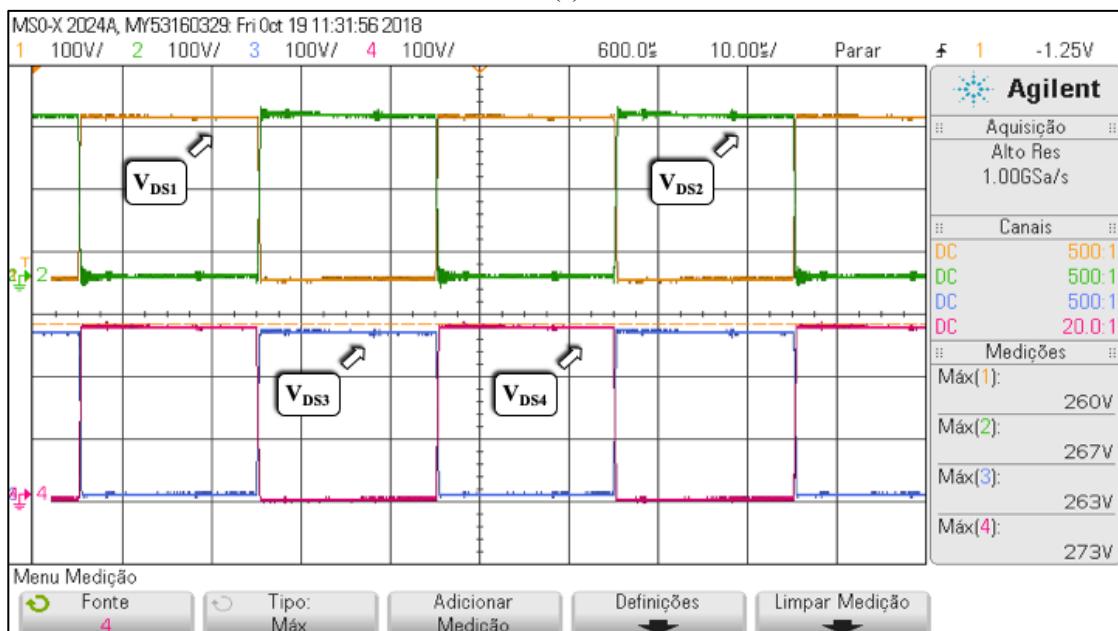

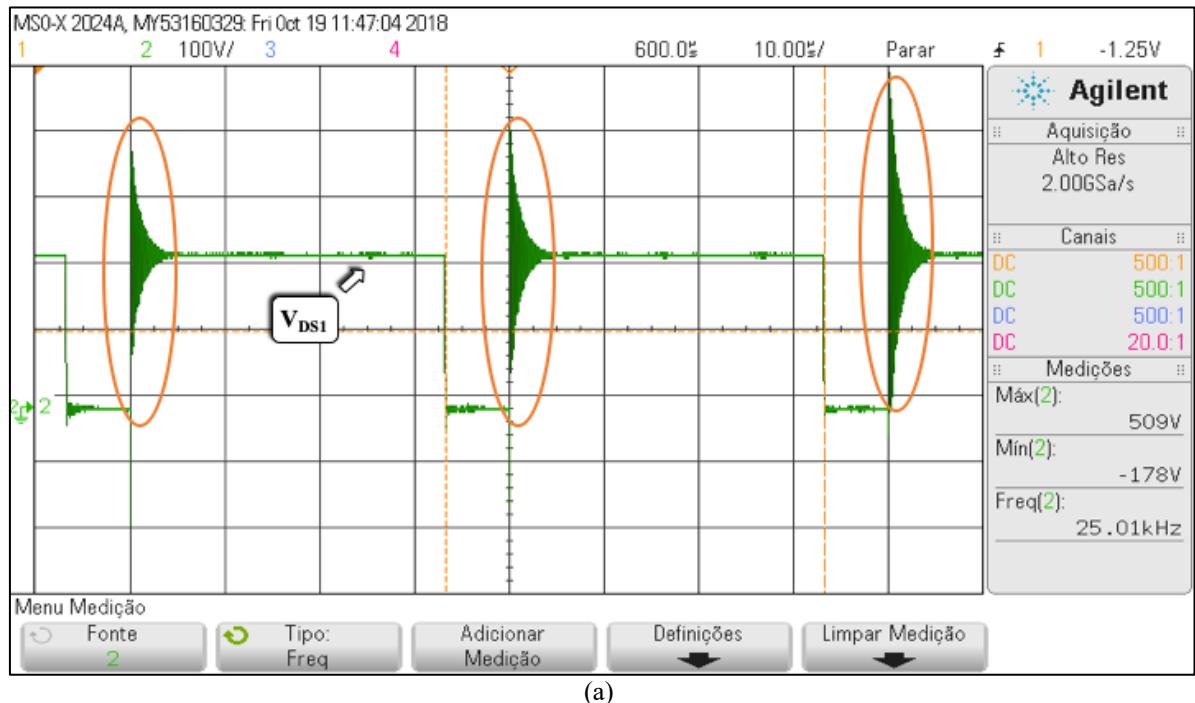

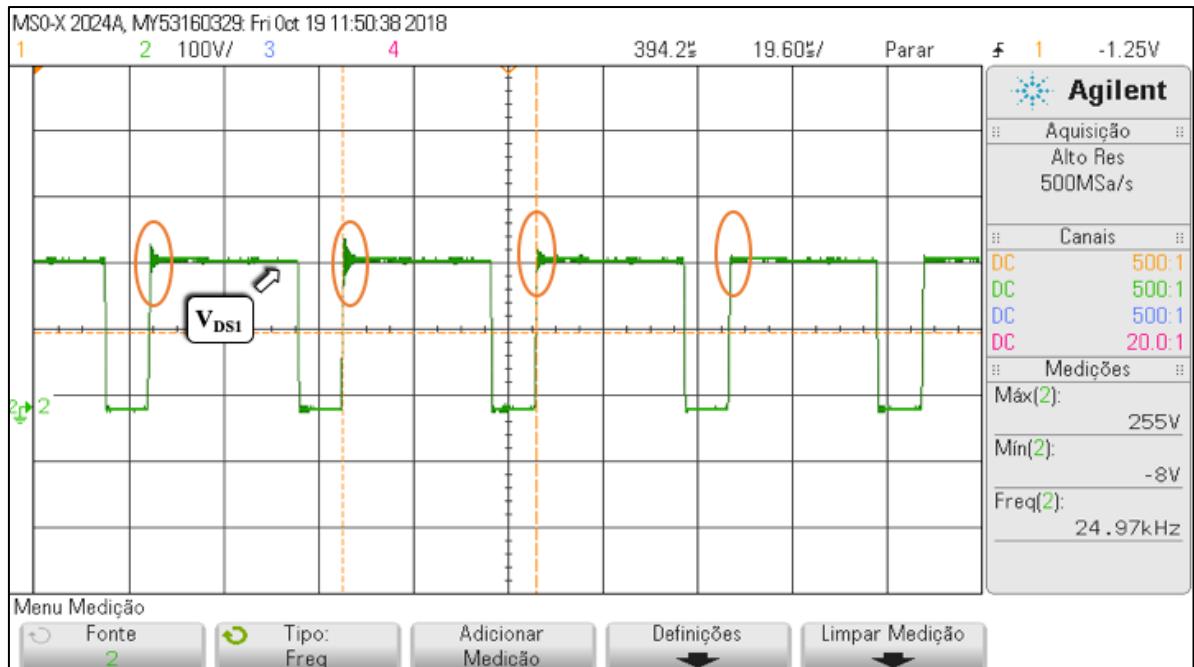

| Figura 5.15 –(a) Tensão do interruptor S1 (VDS1) sem o circuito snubber. (b) Tensão dos interruptor S1 (VDS1) com circuito snubber .....                                                            | 92 |

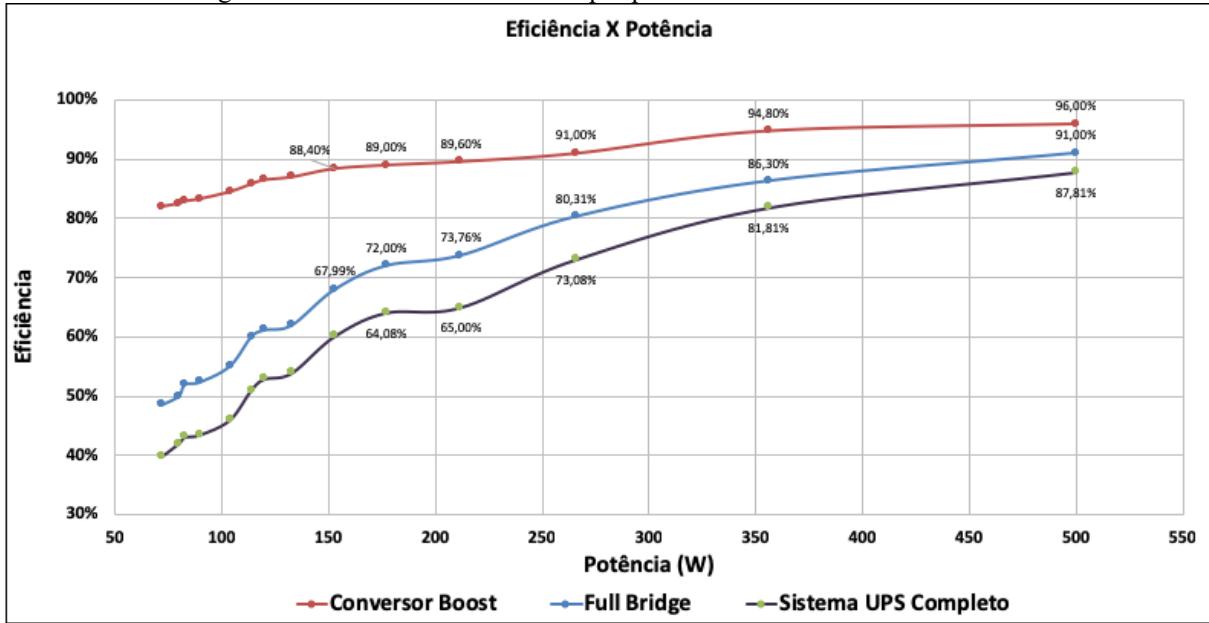

| Figura 5.16 - Gráfico de rendimento por potência de entrada do UPS <i>On-line</i> . ....                                                                                                            | 94 |

# LISTA DE TABELAS

|                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------|----|

| Tabela 2.1 - Operação do conversor com modulação PWM senoidal bipolar .....                                        | 34 |

| Tabela 2.2 - Operação do conversor com modulação PWM senoidal unipolar .....                                       | 39 |

| Tabela 3.1 - Dados de projeto.....                                                                                 | 54 |

| Tabela 3.2 - Tipos de núcleos .....                                                                                | 56 |

| Tabela 3.3 - Tamanho do núcleo .....                                                                               | 57 |

| Tabela 3.4 –Resultados obtidos das principais equações .....                                                       | 62 |

| Tabela 3.5 – Dados MOSFET IRFP 460.....                                                                            | 63 |

| Tabela 3.6 – Dados do projeto UPS .....                                                                            | 66 |

| Tabela 5.1 - Especificações do microprocessador DSP TMS320F28335 da <i>Texas Instruments</i> ®.                    |    |

| .....                                                                                                              | 87 |

| Tabela 5.2 - Especificações do módulo de conversão dos sinais da faixa de 0 a 3,3 V para a faixa de 0 a 15 V ..... | 87 |

| Tabela 5.3 - Especificações do circuito simples para acionamento de interruptores SKHI 10 opA da Semikron.....     | 88 |

| Tabela 5.4 - Fonte para gate driver SKHI PS2 da Semikron.....                                                      | 88 |

| Tabela 5.5 – Comparaçāo do sistema proposto .....                                                                  | 94 |

# LISTA DE ABREVIATURAS E SIGLAS

|                |                                                   |

|----------------|---------------------------------------------------|

| A              | Ampère, unidade de corrente elétrica              |

| $A_{cu}$       | Área do cobre                                     |

| $A_e$          | Área efetiva do núcleo magnético                  |

| $A_l$          | Fator de indutância                               |

| $A_p$          | Tamanho do núcleo de ferrite                      |

| $B_{max}$      | Densidade máxima de fluxo magnético               |

| $B_{sat}$      | Densidade de saturação de fluxo magnético         |

| $C_{oboot}$    | Capacitor de saída do conversor Boost             |

| $C_{inv}$      | Capacitor de saída do inversor Full-bridge        |

| CA             | Corrente alternada                                |

| CC             | Corrente Contínua                                 |

| $c(pk)$        | amplitude onda triangular                         |

| D              | Razão cíclica do conversor Boost                  |

| $D_{inv}$      | Razão cíclica do inversor Full-bridge             |

| $D_0$          | Diodo de saída                                    |

| $D_1$          | Diodo 1 do inversor Full-Bridge                   |

| $D_2$          | Diodo 2 do inversor Full-Bridge                   |

| $D_3$          | Diodo 3 do inversor Full-Bridge                   |

| $D_4$          | Diodo 4 do inversor Full-Bridge                   |

| DSP            | Digital Signal Processor                          |

| E              | Energia armazenada no indutor                     |

| F              | Farad, unidade de capacitância                    |

| F              | Constante de Faraday                              |

| $f_0$          | Frequência da tensão de saída                     |

| $F_{activ}$    | Perdas por ativação                               |

| $F_{conc}$     | Perdas por concentração                           |

| FP             | Fator de potência                                 |

| $f_{S(boost)}$ | Frequência de chaveamento do conversor Boost      |

| $f_{S(inv)}$   | Frequência de chaveamento do inversor Full-bridge |

| H              | Henry, unidade de indutância                      |

|                        |                                                                |

|------------------------|----------------------------------------------------------------|

| Hz                     | Hertz, unidade de frequência                                   |

| I <sub>0</sub>         | Corrente circulante no indutor Boost                           |

| I <sub>Cinv(rms)</sub> | Corrente eficaz do capacitor de filtro do inversor Full-bridge |

| ID <sub>1</sub>        | Corrente do diodo3 do inversor Full-bridge                     |

| ID <sub>1(med)</sub>   | Corrente média do diodo D <sub>3</sub>                         |

| ID <sub>1(rms)</sub>   | Corrente eficaz do diodo D <sub>3</sub>                        |

| ID <sub>1(pk)</sub>    | Pico da corrente do diodo D <sub>3</sub>                       |

| ID <sub>2</sub>        | Corrente do diodo2 do inversor Full-bridge                     |

| ID <sub>3</sub>        | Corrente do diodo3 do inversor Full-bridge                     |

| ID <sub>4</sub>        | Corrente do diodo4 do inversor Full-bridge                     |

| I <sub>in</sub>        | Corrente de entrada                                            |

| I <sub>in(max)</sub>   | Corrente máxima da entrada do inversor Full-bridge             |

| I <sub>in(min)</sub>   | Corrente mínima da entrada do inversor Full-bridge             |

| I <sub>inv</sub>       | Corrente de saída do inversor Full-bridge                      |

| I <sub>inv(pk)</sub>   | Pico da Corrente de saída do inversor Full-bridge              |

| I <sub>inv(rms)</sub>  | Corrente eficaz de saída do inversor Full-bridge               |

| I <sub>Linv(pk)</sub>  | Pico da Corrente do indutor de filtro do inversor Full-bridge  |

| I <sub>Linv(rms)</sub> | Corrente eficaz do indutor de filtro do inversor Full-bridge   |

| I <sub>S2</sub>        | Corrente da chave S <sub>2</sub>                               |

| I <sub>S2(med)</sub>   | Corrente média da chave S <sub>2</sub>                         |

| I <sub>S2(pk)</sub>    | Pico da corrente da chave S <sub>2</sub>                       |

| I <sub>S2(rms)</sub>   | Corrente eficaz da chave S <sub>2</sub>                        |

| I <sub>S3</sub>        | Corrente da chave S <sub>3</sub>                               |

| I <sub>S4</sub>        | Corrente da chave S <sub>4</sub>                               |

| I <sub>S7</sub>        | Corrente da chave S <sub>7</sub>                               |

| J                      | Joule, Unidade de energia                                      |

| j                      | Seção transversal dos condutores                               |

| K                      | Kelvin, Unidade de temperatura                                 |

| k                      | Eficiência                                                     |

| K <sub>j</sub>         | Coeficiente de densidade de corrente nos fios                  |

| L                      | Indutância auxiliar do modelo da célula a combustível          |

| L <sub>B</sub>         | Indutor do conversor Boost                                     |

| l <sub>e</sub>         | Comprimento efetivo do núcleo magnético                        |

| l <sub>g</sub>         | Espessura do entreferro                                        |

|                  |                                                              |

|------------------|--------------------------------------------------------------|

| $L_{inv}$        | Indutor de filtro do inversor Full-bridge                    |

| M                | Índice de modulação                                          |

| MOSFET           | Transistor de efeito de campo de metal-óxido semicondutor    |

| N                | Número de espiras                                            |

| NUPEP            | Núcleo de Pesquisa em Eletrônica de Potência                 |

| $P_{armazenada}$ | Potência armazenada no capacitor                             |

| $P_{comutS2}$    | Perdas de comutação na chave $S_2$                           |

| $P_{condS2}$     | Perdas de condução na chave $S_2$                            |

| $P_{e(boost)}$   | Potência de entrada do conversor Boost                       |

| $P_{e(inv)}$     | Potência de entrada do inversor Full-bridge                  |

| PFC              | Correção do fator de potência                                |

| $P_{O(inv)}$     | Potência de saída do inversor Full-bridge                    |

| $P_{totS2}$      | Perdas totais na chave $S_2$                                 |

| PWM              | Pulse With Modulate                                          |

| $R_O$            | Resistência da carga                                         |

| s                | Segundos, unidade de tempo                                   |

| $S_1$            | Chave 1 do inversor Full-bridge                              |

| $S_2$            | Chave 2 do inversor Full-bridge                              |

| $S_3$            | Chave 3 do inversor Full-bridge                              |

| $S_4$            | Chave 4 do inversor Full-bridge                              |

| T                | Período total                                                |

| t                | Variável de tempo                                            |

| $T_a$            | Temperatura ambiente                                         |

| $t_f$            | Tempo de descida                                             |

| $t_n$            | Tempo de início de cada etapa onde $n=1,2,3\dots$            |

| $t_r$            | Tempo de subida                                              |

| $T_{Sboost}$     | Período da frequência de chaveamento do conversor Boost      |

| $T_{Sinv}$       | Período da frequência de chaveamento do inversor Full-bridge |

| UPS              | Uninterruptible Power Supply                                 |

| V                | Volts, unidade de tensão elétrica                            |

| $V_{AB}$         | Tensão de saída do bloco inversor                            |

| $V_{AC}$         | Módulo da tensão de entrada do conversor                     |

| $V_0$            | Tensão de saída                                              |

| $V_{0(med)}$     | Tensão média de saída                                        |

|                      |                                                                |

|----------------------|----------------------------------------------------------------|

| $V_{C_{inv}}$        | Tensão de saída do capacitor de filtro do inversor Full-bridge |

| $V_{C(pk)}$          | Pico da Tensão da moduladora senoidal                          |

| $V_{C_{boost}}$      | Tensão de saída do conversor Boost                             |

| $V_{C_{boost(max)}}$ | Tensão máximo de saída do conversor Boost                      |

| $V_{C_{boost(min)}}$ | Tensão mínima de saída do conversor Boost                      |

| $V_{cr}$             | Tensão da portadora triangular                                 |

| $VD_0$               | Tensão diodo de saída                                          |

| $VD_{0(max)}$        | Tensão máxima do diodo $D_0$                                   |

| $VD_{0(med)}$        | Tensão média diodo do diodo $D_0$                              |

| $VD_{3(max)}$        | Tensão máxima do diodo $D_3$                                   |

| $VgS_1$              | Tensão gate chave $S_1$                                        |

| $VgS_2$              | Tensão gate chave $S_2$                                        |

| $VgS_3$              | Tensão gate chave $S_3$                                        |

| $VgS_4$              | Tensão gate chave $S_4$                                        |

| $V_{in}$             | Tensão de entrada                                              |

| $V_{in(max)}$        | Tensão máxima de entrada                                       |

| $V_{in(med)}$        | Tensão média de entrada                                        |

| $V_{in(min)}$        | Tensão mínima de entrada                                       |

| $V_{in(pk)}$         | Pico da tensão de entrada                                      |

| $V_{inv}$            | Tensão de saída do inversor Full-bridge                        |

| $V_{inv(max)}$       | Tensão de saída máxima do inversor Full-bridge                 |

| $V_{inv(pk)}$        | Pico da tensão de saída do inversor Full-bridge                |

| $V_{inv(rms)}$       | Tensão de saída eficaz do inversor Full-bridge                 |

| $V_m$                | Tensão senoidal                                                |

| $V_{ref}$            | Tensão de referência                                           |

| $V_{tri}$            | Tensão da portadora triangular                                 |

| $VS_{1(max)}$        | Tensão máxima da chave $S_1$                                   |

| $V_{tri(pk)}$        | Pico da tensão da portadora triangular                         |

| $W$                  | Watts, unidade de potência                                     |

| $W_c$                | Energia capacitor                                              |

| $ZCS$                | Chaveamento a corrente nula                                    |

| $ZVS$                | Chaveamento a tensão nula                                      |

| $\Delta t_n$         | Variação do tempo, onde $n=1,2,3,\dots$                        |

| $\Delta i_L$         | Variação da corrente do inversor Full-bridge                   |

|                      |                                                     |

|----------------------|-----------------------------------------------------|

| $\Delta i_{L_{max}}$ | Variação máxima da corrente do inversor Full-bridge |

| $\Delta v$           | Variação da tensão de saída do conversor Boost      |

| $\Delta V_{inv}$     | Variação da tensão de saída do inversor Full-bridge |

| $\eta$               | Rendimento                                          |

| $\mu_e$              | Permeabilidade efetiva do núcleo                    |

| $\mu_0$              | Permeabilidade do vácuo                             |

| $\omega_0$           | Frequência natural                                  |

| $\Omega$             | Ohm, unidade de resistência elétrica.               |

# SUMÁRIO

|                                                                                                  |           |

|--------------------------------------------------------------------------------------------------|-----------|

| <b>CAPÍTULO 1 INTRODUÇÃO GERAL .....</b>                                                         | <b>20</b> |

| <b>CAPÍTULO 2 INVERSOR MONOFÁSICO DE TENSÃO PARA SISTEMAS UPS ....</b>                           | <b>23</b> |

| 2.1 INTRODUÇÃO.....                                                                              | 23        |

| 2.2 SISTEMA ININTERRUPTO DE ENERGIA .....                                                        | 24        |

| 2.3 INVERSOR MONOFÁSICO DE TENSÃO.....                                                           | 25        |

| 2.3.1 O Inversor Monofásico em Ponte Completa .....                                              | 25        |

| 2.3.2 Inversor de Tensão monofásico em Meia-Ponte .....                                          | 26        |

| 2.3.3 Inversor de Tensão Monofásico Push-Pull.....                                               | 27        |

| 2.4 TOPOLOGIAS DE UPS MONOFÁSICAS DO TIPO <i>ON-LINE</i> .....                                   | 28        |

| 2.4.1 Conversor CA-CC e conversor CC-CA em Ponte Completa .....                                  | 28        |

| 2.4.2 Conversor CA-CC e conversor CC-CA em Meia-Ponte .....                                      | 29        |

| 2.5 ESTRATÉGIA DE MODULAÇÃO .....                                                                | 30        |

| 2.5.1 Modulação PWM Senoidal Bipolar.....                                                        | 31        |

| 2.5.2 Modulação PWM Senoidal Unipolar .....                                                      | 31        |

| 2.6 ANÁLISE DA MODULAÇÃO .....                                                                   | 33        |

| 2.6.1 ETAPAS DE OPERAÇÃO – PWM BIPOLAR.....                                                      | 34        |

| 2.6.2 ETAPAS DE OPERAÇÃO – PWM UNIPOLAR .....                                                    | 38        |

| 2.7 CONSIDERAÇÕES FINAIS .....                                                                   | 47        |

| <b>CAPÍTULO 3 PROJETO E ESPECIFICAÇÃO DO INVERSOR MONOFÁSICO COM MODULAÇÃO BIPOLAR.....</b>      | <b>48</b> |

| 3.1 INTRODUÇÃO.....                                                                              | 48        |

| 3.2 ESFORÇOS NOS SEMICONDUTORES DO INVERSOR.....                                                 | 49        |

| 3.2.1 Esforços nas Chaves S <sub>1</sub> e S <sub>4</sub> .....                                  | 49        |

| 3.2.2 Esforços nos Diodos em Antiparalelo das chaves S <sub>2</sub> -S <sub>3</sub> .....        | 52        |

| 3.2.3 Esforços no Indutor do Inversor .....                                                      | 53        |

| 3.2.4 Esforços no Capacitor do Inversor .....                                                    | 53        |

| 3.3 ESPECIFICAÇÕES DE PROJETO .....                                                              | 54        |

| 3.3.1 Determinação dos Valores Eficazes, Médios, Máximos e Mínimos do inversor Full-Bridge ..... | 54        |

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| 3.3.2 Determinação da Carga Linear Resistiva .....                     | 55         |

| 3.3.3 Determinação do indutor $L_{inv}$ do filtro. ....                | 55         |

| 3.3.4 Determinação do capacitor $C_{0inv}$ do filtro.....              | 60         |

| 3.3.5 Determinação dos componentes semicondutores .....                | 61         |

| 3.3.6 Perdas nas Chaves .....                                          | 63         |

| 3.3.7 Resistência Térmica do Dissipador .....                          | 64         |

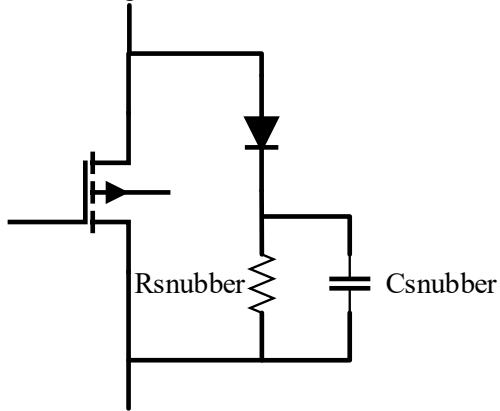

| 3.3.8 Snubbers .....                                                   | 64         |

| 3.4 CONSIDERAÇÕES FINAIS .....                                         | 66         |

| <b>CAPÍTULO 4 ESTRATÉGIA DE CONTROLE DO SISTEMA UPS COMPLETO .....</b> | <b>67</b>  |

| 4.1 INTRODUÇÃO.....                                                    | 67         |

| 4.2 ESTRÁTEGIA DE CONTROLE.....                                        | 67         |

| 4.2.1 Circuito de comando do conversor Boost.....                      | 67         |

| 4.2.2 Modelagem Matemática do Inversor.....                            | 68         |

| 4.2.3 Circuito de comando do inversor Full-bridge.....                 | 78         |

| 4.3 CONSIDERAÇÕES FINAIS .....                                         | 79         |

| <b>CAPÍTULO 5 RESULTADOS DE SIMULAÇÃO E EXPERIMENTAIS.....</b>         | <b>80</b>  |

| 5.1 INTRODUÇÃO.....                                                    | 80         |

| 5.2 RESULTADOS DE SIMULAÇÃO COMPUTACIONAL .....                        | 80         |

| 5.3 RESULTADOS EXPERIMENTAIS .....                                     | 85         |

| 5.3.1 Análise dos resultados práticos.....                             | 88         |

| 5.4 CONSIDERAÇÕES FINAIS .....                                         | 93         |

| <b>CAPÍTULO 6 CONCLUSÃO GERAL .....</b>                                | <b>95</b>  |

| <b>REFERÊNCIAS.....</b>                                                | <b>97</b>  |

| <b>LISTA DE PUBLICAÇÕES ASSOCIADA A PESQUISA .....</b>                 | <b>101</b> |

| <b>APÊNDICE A CÓDIGO IMPLEMENTADO DSP .....</b>                        | <b>102</b> |

| <b>APÊNDICE B PLACA DESENVOLVIDA.....</b>                              | <b>110</b> |

# CAPÍTULO 1

## INTRODUÇÃO GERAL

---

---

A energia elétrica é um elemento de extrema importância na vida de um grande número de pessoas. Aonde quer que se vá, a eletricidade é indispensável, seja nos lares, no comércio ou mesmo nos ambientes de lazer. Ela ilumina os ambientes, aciona eletrodomésticos e equipamentos eletrônicos, aquece e esfria ambientes entre tantas outras aplicações encontradas no dia a dia.

Sendo assim, com a evolução da tecnologia, principalmente da indústria eletroeletrônica, pode-se afirmar que os equipamentos eletrônicos estão presentes em todos, ou quase todos, os setores da sociedade. Neste contexto, em setores essenciais à sociedade, tais como: telecomunicações, informática, saúde, transporte, financeiro, indústria e energia, existe a necessidade de que alguns equipamentos operem de modo adequado e ininterrupto, a fim de evitar falhas nos mesmos e possíveis danos aos consumidores (GONÇALVES, 2008).

O suprimento de energia elétrica pode sofrer perturbações que a desviam significativamente da sua condição ideal. Surtos de tensão, perda momentânea de tensão e oscilações transitórias de tensão são algumas destas perturbações. Essas interrupções são inadmissíveis em algumas aplicações consideradas críticas como, por exemplo, nos sistemas de emergência hospitalar, de informática, industrial e de telecomunicação (LINARD, 2009).

Idealmente, as concessionárias de energia elétrica deveriam ser capazes de garantir o seu serviço sem interrupções ou sem distúrbios, porém, isto ainda não é possível. A energia elétrica não está livre de interrupções, falhas e distúrbios. Tais fenômenos estão presentes nas instalações elétricas internas e externas, sendo que todo equipamento eletrônico está suscetível a estes problemas.

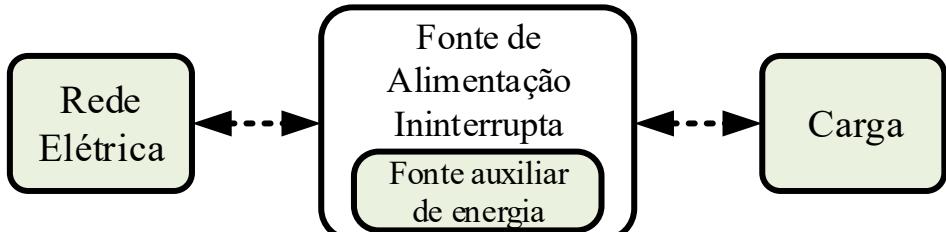

Diante destes fatos, várias empresas investem em pesquisas para o desenvolvimento de equipamentos eletrônicos associados a uma fonte auxiliar de energia independente, capazes de garantir o funcionamento dos equipamentos essenciais de seus sistemas, quando ocorrer eventuais falhas no abastecimento de energia da rede de corrente alternada (CA) de alimentação. Os equipamentos produzidos para este fim foram denominados Sistemas Ininterruptos de Suprimento de Energia ou, em inglês, *Uninterruptible Power Supply* (UPS), e conhecido popularmente no Brasil como *Nobreak*, sendo a sua estrutura genérica ilustrada na Figura 1.1.

Figura 1.1 – Estrutura Genérica Sistema UPS

Fonte: Dados do próprio autor.

Um sistema UPS genérico é constituído por um conversor de energia que processa a energia proveniente da rede CA ou da fonte auxiliar de energia e alimenta a carga. Pela Figura 1.1, observa-se a possibilidade de o conversor processar energia da rede CA e entregar parte desta à fonte auxiliar de energia (processo comum quando há o uso de banco de baterias), como também a possibilidade do conversor interligar a fonte auxiliar de energia com a rede CA, através de um conversor bidirecional, onde a fonte auxiliar de energia é capaz de suprir a carga e entregar o excedente de energia à rede CA (processo comum quando há o uso de geradores).

Estes equipamentos podem ser divididos em três categorias, que se diferem em aspectos construtivos e de operação, sendo elas: *UPS off-line*, *UPS line-interactive* e *UPS on-line*. Informações mais detalhadas sobre os sistemas citados podem ser encontradas em (MACIEL, 2019).

Nesse contexto, o presente trabalho de dissertação apresenta o estudo, a metodologia de projeto e a implementação prática de um inversor Full-Bridge, com a finalidade de integrar um sistema UPS do tipo *on-line*. Este apresenta como estágio de entrada o conversor Boost SR-ZCS-ZVS-PWM, apresentado em (MACIEL, 2019) e (MACIEL e COSTA, 2015). O sistema UPS em pauta tem a vantagem de integrar as funções de um conversor com correção do fator de potência (CFP) e de um conversor CC-CC elevador necessário na maioria das aplicações. Além disso, apresenta uma tensão de saída puramente senoidal e com baixa Distorção Harmônica (THD), dentro dos critérios estabelecidos pela norma IEC 63040-3. A técnica de controle do inversor é implementada com um DSP (*Digital Signal Processor*) e se baseia na técnica denominada controle de modulação bipolar de malha aberta.

Para apresentação dos resultados desta pesquisa, este documento se encontra dividido em seis capítulos incluindo este capítulo introdutório. No Capítulo 2 é apresentada uma revisão sobre os tipos de inversores monofásicos, algumas topologias *UPS* e os tipos de modulação *PWM* empregados em conversores CC-CA – estágio de saída de sistemas UPS. Em seguida, no Capítulo 3, a topologia proposta é apresentada, incluindo o desenvolvimento das equações matemáticas necessárias para dimensionamento dos dispositivos semicondutores utilizados na

implementação protótipo. Para o Capítulo 4, tem-se o estudo da estratégia de controle e a modelagem do inversor. O Capítulo 5 apresenta os resultados de simulação seguido dos resultados experimentais obtidos. Por fim, o Capítulo 6 apresenta as conclusões gerais e sugestões para trabalhos futuros. O diagrama esquemático do bloco de potência e a placa de controle podem ser vistos no Apêndice B.

# CAPÍTULO 2

## INVERSOR MONOFÁSICO DE TENSÃO PARA SISTEMAS UPS

---

### 2.1 INTRODUÇÃO

Na atualidade, as UPS não se limitam a garantir a continuidade do fornecimento da energia elétrica à carga. Alguns modelos focam-se também na qualidade da energia elétrica. No passado, os problemas relacionados com a qualidade da energia elétrica deviam-se quase exclusivamente a falhas de energia, a sobretensões e a sobrentensões, uma vez que as cargas a alimentar eram principalmente lineares (BAPTISTA, 2012). Os sistemas UPS do tipo *on-line* tipicamente apresenta dois estágios de conversão de energia.

No primeiro estágio, o retificador opera como conversor de tensão CA da rede elétrica em tensão CC e referente ao segundo estágio, o inversor converte tensão contínua CC em alternada CA para a saída. Deste modo, dependendo da topologia utilizada, a tensão de saída fornecida para a carga possui amplitude, frequência e forma independentes da entrada. Esta é a única arquitetura de *UPS* que protege a carga contra os principais distúrbios da rede elétrica, sempre fornecendo tensão senoidal na saída além de não apresentar interrupção nas transferências de carga.

É conhecido que a frequência da tensão de saída do inversor é determinada pelo chaveamento dos dispositivos semicondutores que o formam, dependendo, portanto, do circuito de controle e o método de modulação escolhido. Neste trabalho foi adotado o controle da tensão por largura de pulsos (*PWM*) senoidal.

Neste capítulo são apresentadas as principais características dos sistemas UPS, os tipos de inversores monofásicos de tensão e também os tipos de modulação por largura de pulsos senoidal. Também são apresentadas a topologia e a modulação adotada no desenvolvimento deste trabalho.

## 2.2 SISTEMA ININTERRUPTO DE ENERGIA

De acordo com (BEKiarov e EMADI, 2002) e (EMADI, NASIRI e BEKiarov, 2005), a UPS ideal deve ser capaz de prover energia elétrica à carga de forma que esta mantenha um perfeito funcionamento. A capacidade de uma UPS comutar o modo de alimentação da carga, do sistema primário (rede elétrica) para o sistema secundário (sistema armazenador de energia), garante várias características inerentes à qualidade da energia elétrica (LEE, KINOSHITA e SANADA, 2012).

Deste modo, a UPS deve ter as seguintes características: alta confiabilidade, alta eficiência, regulação senoidal com baixa taxa de distorção harmônica (THD), baixa interferência eletromagnética, tamanhos reduzidos, baixa manutenção, custo, ruído e peso.

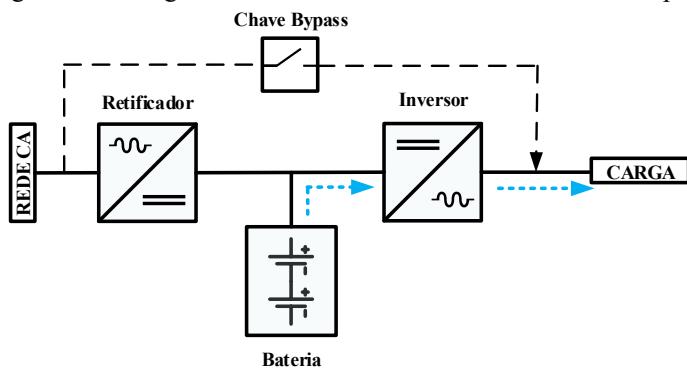

A UPS do tipo *on-line* é o interesse deste trabalho e, a seguir, é feita uma breve explanação sobre esta UPS. Este tipo de sistema UPS tem como característica marcante o fornecimento contínuo de energia elétrica à carga, a qual está ligada mesmo quando ocorre ausência da rede de alimentação devido a qualquer distúrbio. A Figura 2.1 apresenta um diagrama de blocos para esta topologia.

Figura 2.1 – Diagrama de blocos de um sistema UPS *On-line* típico

Fonte: Dados do próprio autor.

Como pode ser observado através da Figura 2.1, o sistema UPS *On-line* é composto por: carregador de baterias (retificador), inversor (conversor CC-CA), sistema armazenador de energia e um circuito *by-pass*. O retificador (conversor CA-CC) é utilizado para suprir o barramento CC, que alimenta o inversor e o sistema armazenador de energia. O inversor converte a tensão contínua em alternada, de forma que o sistema forneça sempre uma tensão estável para a carga e seja dimensionado para operar tanto no modo rede (normal) como em modo *backup*.

O sistema armazenador de energia é usado para alimentar a carga durante uma interrupção da rede de alimentação por um determinado período de autonomia. E a chave *bypass* é utilizada para conectar a carga diretamente a rede de alimentação CA caso haja uma falta ou seja necessário dar manutenção na UPS. A entrada em funcionamento do *bypass* pode ser feita de forma automática, dependendo da decisão a ser tomada pela supervisão do sistema, ou de forma manual (BEKiarov e EMADI, 2002) e (EMADI, NASIRI e BEKiarov, 2005).

Nos subitens a seguir, são apresentadas algumas topologias dos conversores CC-CA aplicados em UPS *On-line*.

## 2.3 INVERSOR MONOFÁSICO DE TENSÃO

Nos próximos tópicos, o foco principal é o inversor monofásico de tensão que é o mais comum dos conversores CC-CA. Este conversor é capaz de transformar uma forma de onda continua em alternada, geralmente na forma de onda quadrada ou modulada em PWM. Dentre as várias topologias encontradas na literatura, as mais comuns são os conversores CC-CA de tensão, as quais são apresentadas a seguir.

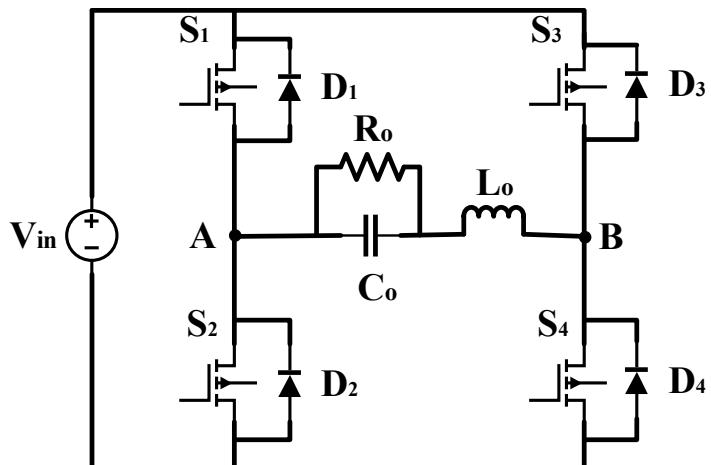

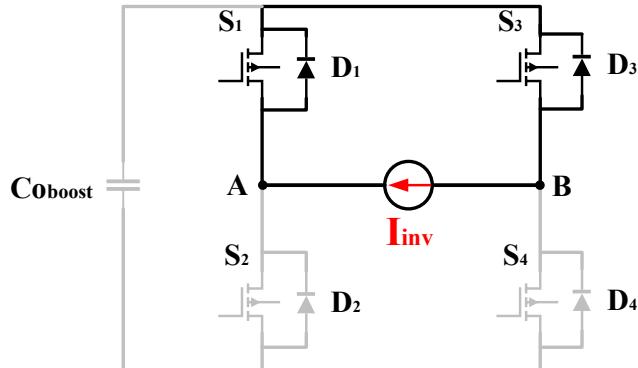

### 2.3.1 O Inversor Monofásico em Ponte Completa

Esta estrutura é recomendada para inversores de altas potências e altas tensões de saída. A saída produzida é uma tensão senoidal, que é resultante deste inversor aliada a uma técnica de modulação e filtro apropriados (OLIVEIRA, 2007) e (BARBI, 2005).

Figura 2.2 – Conversor CC-CA em ponte completa (Full-Bridge)

Fonte: Dados do próprio autor.

O inversor de tensão monofásico ponte completa apresentado na Figura 2.2 pode ser encontrado em (BARBI, 2005) e (GOPINATH e SANGSUN, 2004). Ele é formado por dois braços: um braço do inversor é formado pelos interruptores  $S_1$  e  $S_4$ , e o outro braço, pelos interruptores  $S_2$  e  $S_3$ . As chaves semicondutoras são acionadas em pares em diagonal, ou seja, é feito de forma complementar com desfasamento de  $180^\circ$ . No momento em que os interruptores  $S_1$  e  $S_4$  estão conduzindo, a tensão de saída aplicada à carga é igual à tensão de entrada ( $+V_{in}$ ). Quando os interruptores  $S_2$  e  $S_3$  estão conduzindo, a tensão de entrada com polaridade invertida é aplicada à carga ( $-V_{in}$ ). Sendo assim, o resultado é uma forma de onda quadrada de magnitude igual à da fonte de entrada (barramento CC).

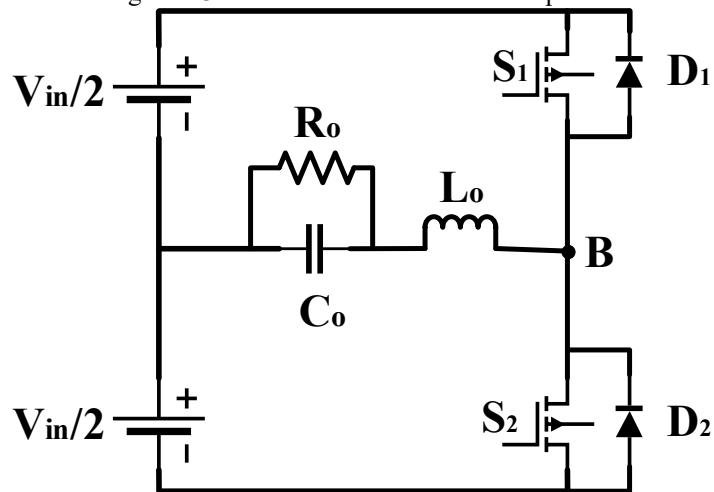

### 2.3.2 Inversor de Tensão monofásico em Meia-Ponte

O inversor meia ponte também é conhecido na literatura como inversor Ponto Médio ou *Half-Bridge* (meia ponte) e pode ser visto na Figura 2.3. Essa estrutura é a mais simples e possui apenas um braço com um único par de chaves semicondutores e precisa de uma fonte de alimentação CC com ponto médio. Este circuito é utilizado em aplicações em baixas potências, pois o nível de tensão na carga é a metade que a aplicada por uma topologia em ponte completa, resultando em uma corrente duas vezes maior para uma mesma potência.

Figura 2.3 – Conversor CC-CA em meia ponte

Fonte: Dados do próprio autor.

O seu funcionamento pode ser descrito da seguinte forma: a chave semicondutora  $S_1$  é colocada em condução, a corrente cresce de forma exponencialmente e a fonte de alimentação entrega energia à carga. Quando  $S_1$  está aberta, a corrente de carga é mantida no mesmo sentido,

já que a indutância de carga não permite alterações bruscas na corrente, decrescendo através do diodo em antiparalelo  $D_2$ .

A corrente circulará pelo diodo  $D_2$  até se anular, provocando a entrada em condução da chave semicondutora  $S_2$ . A partir deste momento, a corrente irá inverter o sentido e crescerá exponencialmente. Nesta etapa, a carga recebe energia da fonte. E ao ocorrer a anulação da corrente, irá reiniciar um novo ciclo de operação.

Pode ser verificado através da descrição do funcionamento desta topologia que seus interruptores  $S_1$  e  $S_2$  conduzem ou são bloqueados de forma alternada, fazendo com que a tensão de saída aplicada à carga seja uma onda quadrada, cuja frequência irá ser determinada pela frequência de chaveamento.

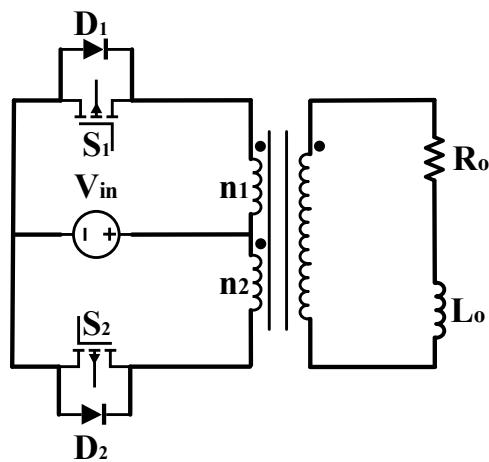

### 2.3.3 Inversor de Tensão Monofásico Push-Pull

A configuração do inversor *push-pull* é bem adaptado às modulações em baixas frequências e baixas potências (BARBI, 2005). A configuração deste inversor pode ser observada na Figura 2.4, e apresenta as seguintes características: emprega apenas uma fonte de alimentação CC ( $V_{in}$ ), emprega apenas duas chaves semicondutoras comandadas ( $S_1$  e  $S_2$ ), a carga é isolada da fonte de alimentação CC - estrutura naturalmente isolada empregando um transformador com ponto médio no primário, a fonte de alimentação CC e as chaves semicondutores estão ligadas na mesma referência.

Figura 2.4 – Conversor CC-CA Push-Pull

Fonte: Dados do próprio autor.

Quando a chave semicondutora  $S_1$  entra em condução, a  $S_2$  é mantida bloqueada. A corrente na carga cresce significativamente e, durante esta etapa, a fonte de alimentação fornece

energia à carga. Ao abrir  $S_1$ , a corrente se mantém no mesmo sentido devido a indutância da carga, de forma que passa a decrescer pelo diodo  $D_2$ .

Com a anulação da corrente, se dá início a outra etapa de operação na qual a chave semicondutora  $S_2$  é colocada em condução e a corrente passa a crescer novamente no sentido contrário. Durante esta etapa a fonte volta a transferir energia a carga. Quando  $S_2$  é aberta, a corrente passa a decrescer pelo diodo  $D_1$  e a energia armazenada no indutor de carga será transferida para a fonte de alimentação. Esta etapa termina quando a corrente de carga se anula.

## 2.4 TOPOLOGIAS DE UPS MONOFÁSICAS DO TIPO *ON-LINE*

De acordo com os retificadores apresentados em (LINARD, 2009), os mesmos podem alimentar os inversores apresentados no item 2.3. Sendo assim, alguns dos circuitos utilizados em sistemas UPS com dupla conversão serão demonstrados, mencionando vantagens e desvantagens, assim como a justificativa para a escolha da topologia adotada. As demais estruturas são apresentadas em (AAMIR, KALWAR E MEKHILEF, 2016).

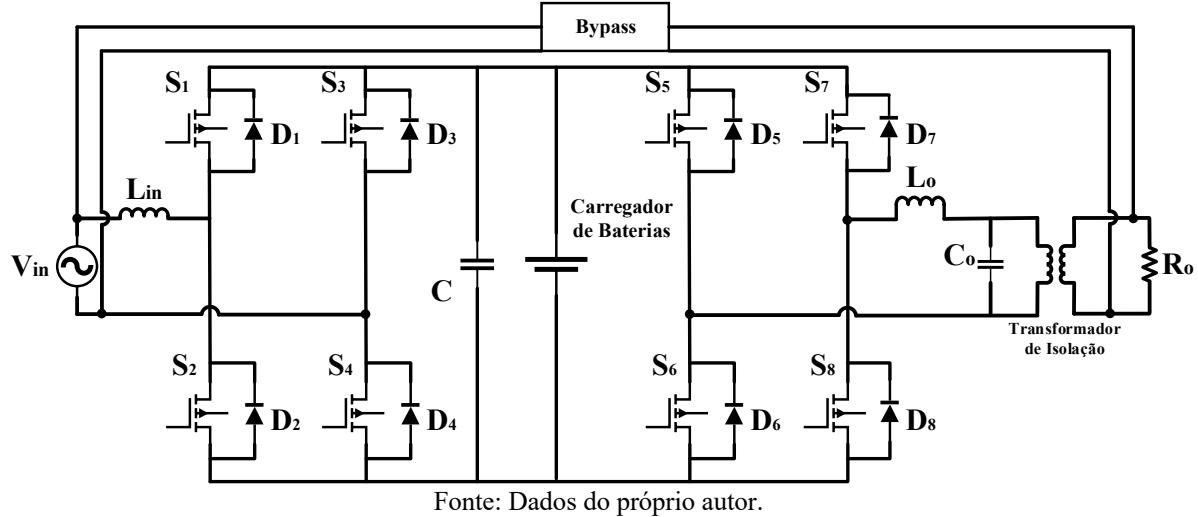

### 2.4.1 Conversor CA-CC e conversor CC-CA em Ponte Completa

Representado na Figura 2.5, esta topologia em ponte completa apresenta um retificador CA-CC com tensão CC de qualidade suprimindo o inversor CC-CA. A estrutura apresenta algumas vantagens sobre os conversores com topologia em meia ponte. Dentre elas, pode-se citar: melhor utilização do *link* CC de tensão e possui a opção de “estado zero” para os interruptores devido a possibilidade do uso de estratégias de controle mais avançadas (EMADI, NASIRI e BEKiarov, 2005). Devido as suas vantagens, esta topologia é preferível para aplicações em média e alta potência. Contudo, possui como desvantagem o fato de possuir muitas chaves semicondutoras e a necessidade de um transformador de isolamento, contribuindo para ser um sistema volumoso, pesado e de alto custo.

Figura 2.5 – Conversores CA-CC e CC-CA em ponte completa.

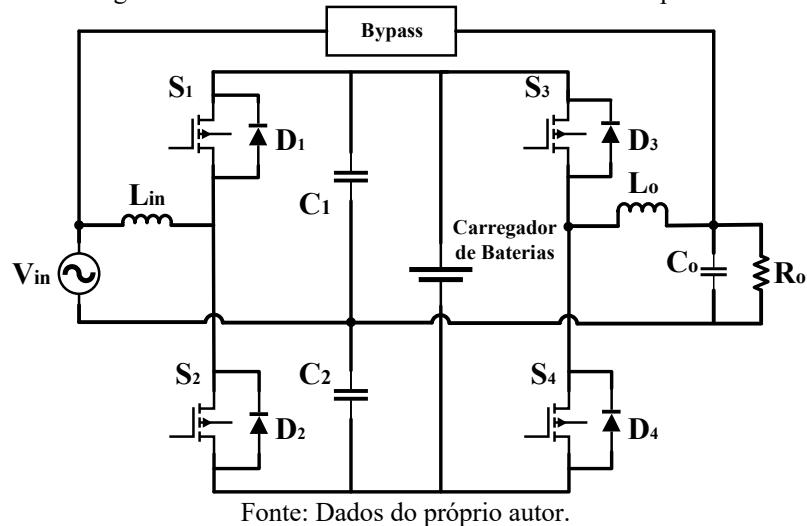

#### 2.4.2 Conversor CA-CC e conversor CC-CA em Meia-Ponte

Comparando com a estrutura em ponte completa, a configuração em meia ponte é a escolha preferível para baixas potências, pois, apresenta a metade do número de chaves semicondutoras, além de possuir um ponto comum entre a entrada e saída do sistema, eliminando a necessidade de um transformador de isolamento. Esta topologia é apresentada na Figura 2.6. Todavia, considerando que esse sistema é um dobrador de tensão no estágio CA-CC, o barramento CC deve operar, no mínimo, com o dobro da tensão de pico de entrada.

Figura 2.6 – Conversores CA-CC e CC-CA em meia ponte

Porém, algumas desvantagens destacam-se: como o fato de não possuir controle de tensão nos capacitores  $C_1$  e  $C_2$  quando operando em modo bateria, além de necessitar de um

grande número de baterias, e por ser necessário capacitores no barramento CC com tensão de, no mínimo, a tensão de pico da entrada e de um grande número de baterias, o custo do projeto é alto, já que esses capacitores e as baterias são os componentes mais caros de um inversor, (OLIVEIRA, 2007).

## 2.5 ESTRATÉGIA DE MODULAÇÃO

O desenvolvimento de estratégias de controle PWM relaciona-se com o crescimento de diferentes técnicas para reduzir a DHTv da tensão e da corrente. Via de regra, com o aumento da frequência de comutação do controle PWM, tem-se a redução dos harmônicos de baixa frequência. Além do que, os harmônicos da frequência portadora de comutação e os da banda lateral associados, são movidos para mais distante da componente da frequência fundamental. O aumento na frequência de comutação reduz os harmônicos associados, o que resulta em uma menor DHTv. Como resultado, a forma de onda da tensão de saída fica mais próxima da desejada forma de onda senoidal. Desvios na forma de onda senoidal, resulta em correntes distorcidas-na carga, as quais provocam: interferências eletromagnéticas EMI (*Electromagnetic Interference*), perdas harmônicas e ondulações (*ripple*) de torque, no caso de acionamento de motores. Sendo assim, com o aumento da frequência de comutação, a qualidade da forma de onda de saída melhora (REDDY; BABU; SURESH, 2011).

O princípio de funcionamento do inversor de tensão está intimamente ligado a uma estratégia de modulação que, segundo (HOLMES e LIPO, 2003), é o processo de mudança de estado dos componentes eletrônicos em um conversor. As técnicas comumente utilizadas são:

- a) modulação por largura de pulsos otimizada (PWM otimizada);

- b) modulação por largura de pulso senoidal (SPWM);

- c) modulação por pulso único;

- d) e modulação por largura de pulsos múltiplos e iguais entre si.

A modulação por largura de pulso varia com a razão cíclica aplicada aos interruptores em alta frequência de comutação, com o intuito de suprir uma determinada tensão ou corrente na saída em baixa frequência, ou seja, tem-se como objetivo criar uma sequência de pulsos que devem ter o mesmo valor fundamental de uma referência desejada. Todavia, nesta sequência de pulsos existem componentes harmônicos indesejados, os quais devem ser minimizados.

Por outro lado, com a técnica SPWM, é possível levar os harmônicos a uma faixa alta de frequência e operar em frequência fixa. O emprego de frequência fixa aperfeiçoa o projeto

dos componentes magnéticos, tendo em vista que em aplicações onde a frequência é variável, os componentes magnéticos devem ser projetados para toda a faixa de frequência utilizada. Quando o conteúdo harmônico se concentra nas altas frequências, geralmente, os inversores são menos volumosos e mais compactos devido ao reduzido volume do filtro.

### 2.5.1 Modulação PWM Senoidal Bipolar

Na SPWM de dois níveis, também conhecida como SPWM bipolar, o sinal de referência  $V_{REF}$  é comparado com um sinal triangular  $V_{TRI}$  na frequência de comutação de modo a se obter os pulsos de comando para as chaves do inversor. No caso do inversor em ponte completa, quando o valor de referência é maior do que o valor da portadora, o respectivo braço comandado é comutado para o valor da tensão contínua do barramento de entrada. Quando o valor de referência é menor que o valor da portadora, tem-se como resultado a tensão de entrada invertida na saída do estágio inversor. Ou seja, este esquema apresenta saída diferencial com um braço defasado em  $180^\circ$  do outro. A Figura 2.7 (a) mostra a comparação dos sinais  $V_{TRI}$  e  $V_{REF}$  e a respectiva tensão na saída do bloco inversor ( $V_{AB}$ ).

A largura dos pulsos enviados para os interruptores depende da amplitude da referência senoidal de tensão, fazendo com que a tensão  $V_{AB}$  tenha uma componente fundamental na mesma frequência da tensão de referência e os harmônicos deslocados em torno da frequência da portadora  $V_{TRI}$ . Esta modulação apresenta a característica de possuir um único comando para cada dois interruptores, como por exemplo,  $S_1$  e  $S_4$ . Nos outros dois interruptores podem-se usar, idealmente, um comando complementar.

### 2.5.2 Modulação PWM Senoidal Unipolar

De maneira similar à SPWM bipolar, a modulação por largura de pulso senoidal de três níveis, ou SPWM unipolar, também visa deslocar o conteúdo harmônico para as altas frequências. A diferença é que os interruptores  $S_1$  e  $S_3$  ou  $S_2$  e  $S_4$  também podem conduzir simultaneamente, e a tensão diferencial de saída varia entre três níveis de tensão,  $0V$   $-V_{in}$  e  $+V_{in}$ .

A modulação por largura de pulso senoidal unipolar pode ser visualizada na Figura 2.7 (b). Esta técnica possui um nível de complexidade maior do que a modulação dois níveis, a começar pelo comando dos interruptores, que devem ser gerados dois sinais com  $180^\circ$  de desfasagem entre si. O sinal de referência  $V_{REF}$  é comparado com um sinal triangular  $V_{TRI}$  de modo a se obter os pulsos de comando para as chaves de um braço do inversor. Já os pulsos de

comando para o outro braço são obtidos através da comparação do sinal de referência com uma outra portadora triangular  $V_{TRI2}$ , complementar a  $V_{TRI}$ .

De acordo com (HOLMES e LIPO, 2003), é apresentado a diferença entre os tipos de portadoras, pois, embora utilize-se a portadora triangular, pode-se aplicar uma portadora do tipo dente-de-serra. Onde é demonstrado que a portadora do tipo dente-de-serra apresenta resultados inferiores com relação ao espectro harmônico da tensão  $V_{AB}$ , tanto para a modulação unipolar quanto para a bipolar.

Observando-se a Figura 2.7(b), nota-se que o número de pulsos na tensão  $V_{AB}$  é duas vezes maior na modulação três níveis do que o encontrado nos dois níveis, para a mesma frequência de comutação. Este número está diretamente relacionado com a frequência das harmônicas de  $V_{AB}$ .

Figura 2.7 – (a) PWM senoidal bipolar. (b) PWM senoidal unipolar

Fonte: Dados do próprio autor.

Comparando a modulação SPWM unipolar com a modulação bipolar, a primeira apresenta algumas vantagens. Dentre elas, cabe salientar:

- A ondulação de corrente e tensão nos componentes do filtro de saída é significativamente menor, o que reduz os componentes passivos usados na filtragem do sinal de saída;

- Apresenta menores perdas nos interruptores e reduzidas emissões eletromagnéticas, haja vista que as derivadas de corrente e tensão são menores, pois a tensão  $V_{AB}$  varia somente  $V_{ref}$  em cada transição, ao passo que na SPWM bipolar a variação é de  $2V_{ref}$ . (BAKER e AGELIDIS, 1997).

- O desempenho com relação ao espectro harmônico da tensão  $V_{AB}$  também apresenta resultado superior (HOLMES e LIPO, 2003).

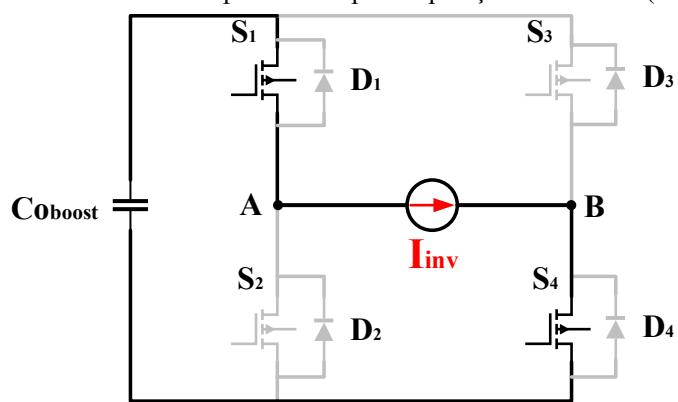

## 2.6 ANÁLISE DA MODULAÇÃO

Nos itens a seguir serão descritas as etapas de operação para o inversor utilizando tanto a modulação bipolar, quanto a modulação unipolar. A fim de simplificar a análise, algumas condições devem ser escolhidas:

1. Todos os elementos semicondutores são vistos como ideais. Portanto, a resistência em estado de condução é nula; em estado de bloqueio é infinita e os tempos de acionamento e desligamento são desprezíveis;

2. Os elementos indutores e capacitores são considerados com resistência nula;

3. O conversor está operando no modo de condução contínua, com frequência de chaveamento fixa e em regime permanente;

4. A carga do inversor possui propriedade de fonte de corrente de valor  $I_{Inv}$ . Logo, para efeito de simplificação, na descrição das etapas a seguir considera-se a carga como uma fonte de corrente;

5. E no decorrer de todo o semiciclo positivo da tensão de saída a corrente não muda de sentido na carga, modificando somente no semiciclo negativo da tensão de saída.

Baseado nas considerações acima descritas, utiliza-se o circuito simplificado ilustrado na Figura 2.8 para explicar as etapas de funcionamento, considerando um único período de chaveamento.

Figura 2.8 – Circuito simplificado do inversor Full-Bridge

Fonte: Dados do próprio autor.

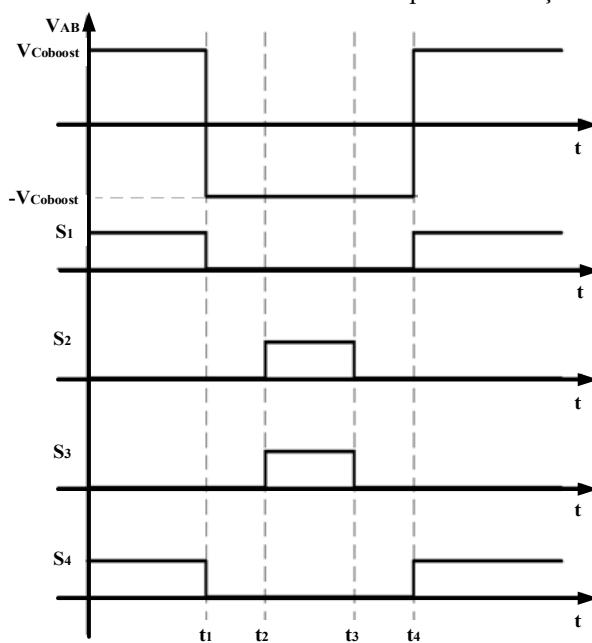

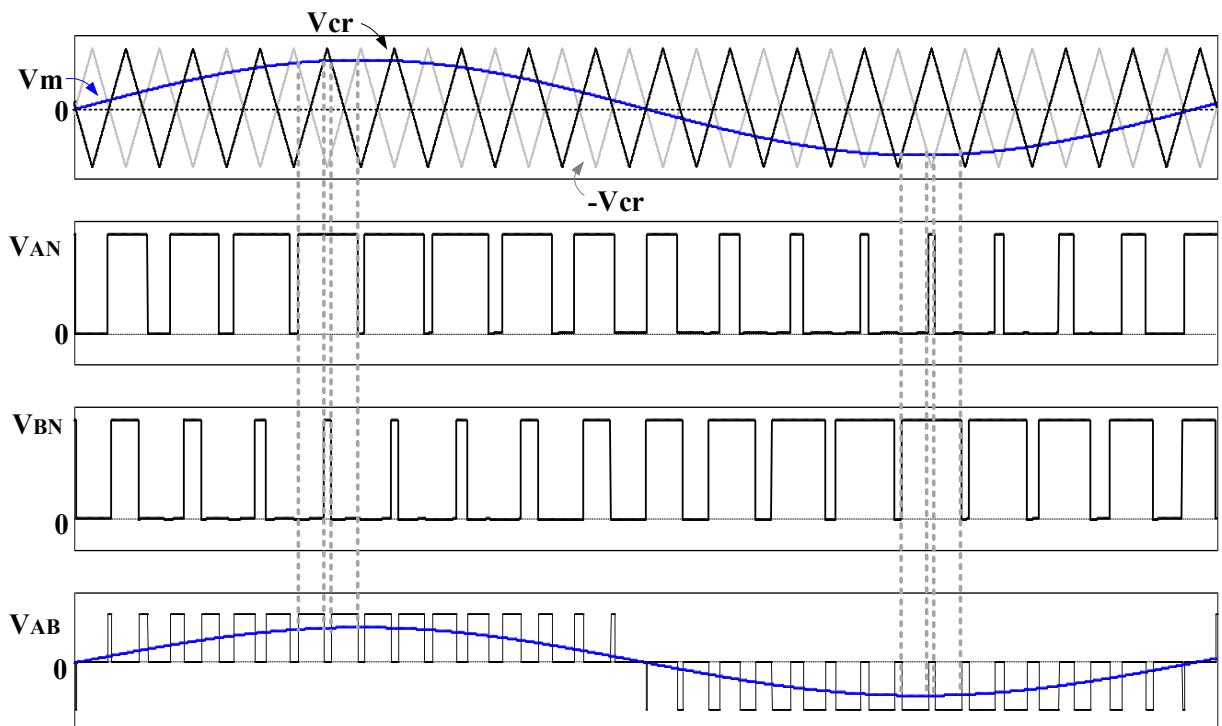

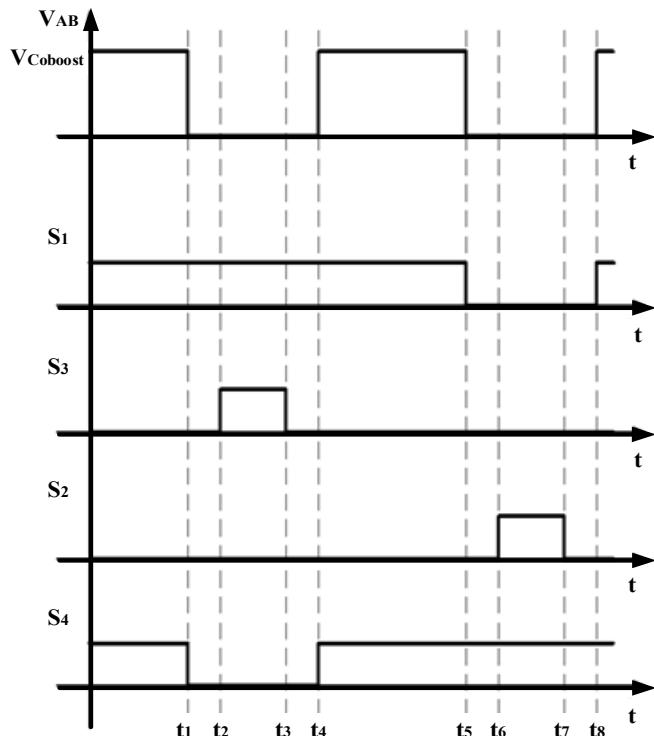

### 2.6.1 ETAPAS DE OPERAÇÃO – PWM BIPOLAR

A modulação bipolar PWM senoidal compõe de dois semiciclo, positivo e negativo, de acordo com a tensão de saída. Sendo capaz de produzir uma tensão de saída senoidal de valor médio nulo, simétrica em amplitude e com frequência constante. A Figura 2.9 apresenta o comportamento da tensão  $V_{AB}$  na saída do inversor e o chaveamento de cada interruptor utilizando a modulação proposta.

Na modulação bipolar, o inversor apresenta quatro etapas de operação, sendo que cada semiciclo da tensão de saída é responsável por duas etapas.

A Tabela 2.1 tem o objetivo de mostrar resumidamente o princípio de operação do inversor PWM bipolar.

Tabela 2.1 - Operação do conversor com modulação PWM senoidal bipolar

| Etapa    | Comparação              | Em condução                       | Bloqueados                                                        | Tensão $V_{AB}$      |

|----------|-------------------------|-----------------------------------|-------------------------------------------------------------------|----------------------|

| Primeira | $V_m(t) \geq V_{cr}(t)$ | S <sub>1</sub> e S <sub>4</sub>   | S <sub>2</sub> e S <sub>3</sub>                                   | +V <sub>Cboost</sub> |

| Segunda  | $V_m(t) \leq V_{cr}(t)$ | D <sub>S2</sub> e D <sub>S3</sub> | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> e S <sub>4</sub> | -V <sub>Cboost</sub> |

| Terceira | $V_m(t) \geq V_{cr}(t)$ | S <sub>2</sub> e S <sub>3</sub>   | S <sub>1</sub> e S <sub>4</sub>                                   | -V <sub>Cboost</sub> |

| Quarta   | $V_m(t) \leq V_{cr}(t)$ | D <sub>S1</sub> e D <sub>S4</sub> | S <sub>1</sub> , S <sub>2</sub> , S <sub>3</sub> e S <sub>4</sub> | +V <sub>Cboost</sub> |

Fonte: Dados do próprio autor.

Figura 2.9 – Modulação PWM senoidal bipolar

Fonte: Dados do próprio autor.

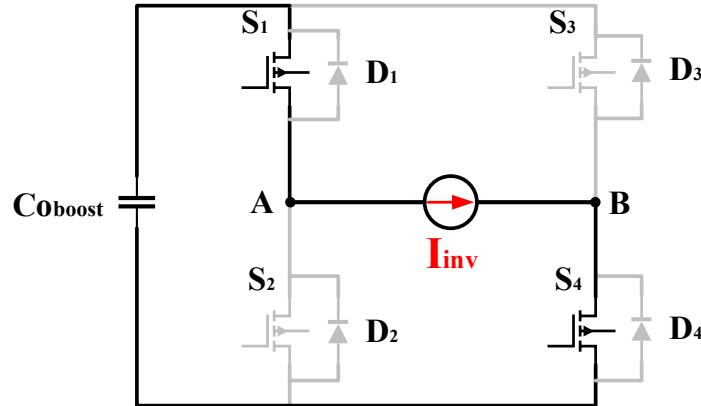

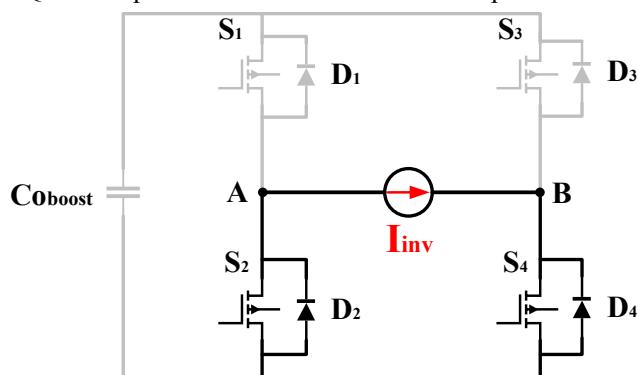

- **Primeira etapa:  $\Delta t_1 [t_0-t_1]$ :**

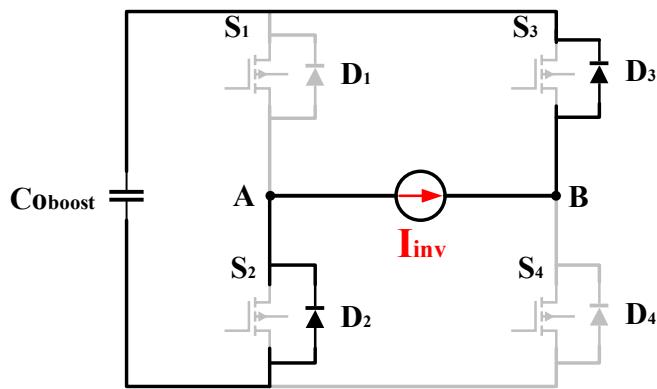

Esta etapa inicia-se quando, no tempo  $t_0$ , a chave  $S_1$  e  $S_4$  são colocadas em condução e termina, no tempo  $t_1$ , quando as chaves  $S_3$  e  $S_2$  são abertas e as chaves  $S_1$  e  $S_4$  são colocadas em condução. A Figura 2.10 exemplifica o circuito equivalente desta primeira etapa. A parte em cinza em todos os desenhos que seguem, indicam as partes do circuito que não atuam ativamente na etapa em questão.

Figura 2.10 – Circuito da primeira etapa de operação do inversor ( $t_0 - t_1$ ).

Fonte: Dados do próprio autor.

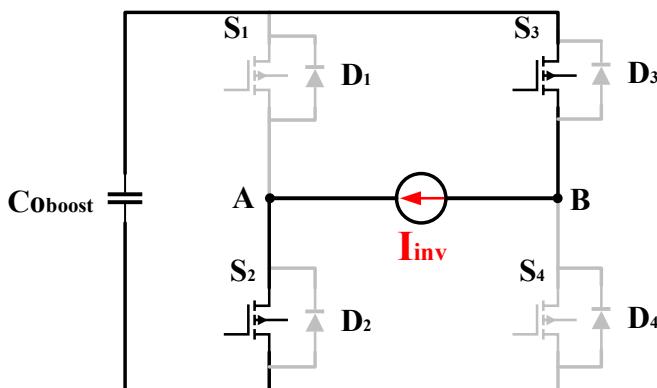

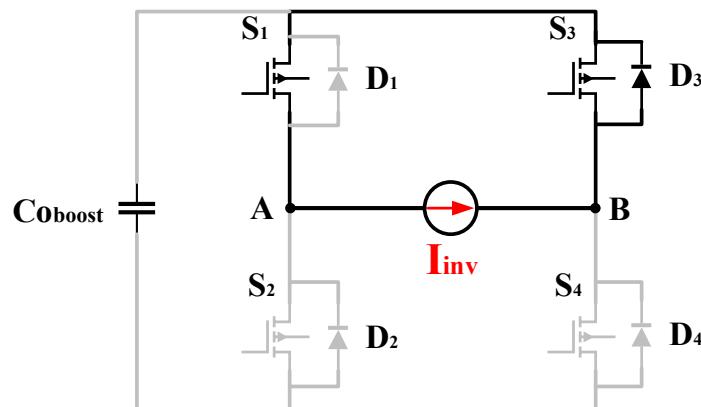

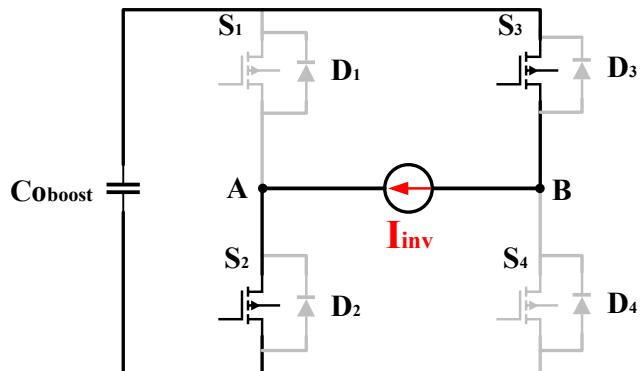

- Segunda etapa:  $\Delta t_2 [t_1-t_2]$ :

O processo se inicia no tempo  $t_1$ , quando as chaves  $S_1$  e  $S_4$  são comandadas para abrir e as chaves  $S_2$  e  $S_3$  são comandadas para fechar. Como a corrente não muda de sentido, neste semiciclo, os diodos  $D_2$  e  $D_3$  são polarizados diretamente e assumem a corrente de carga  $I_{inv}$ . Tal fase termina no tempo  $t_2$ , quando as chaves são  $S_2$  e  $S_3$  assumem a corrente da carga. A Figura 2.11 ilustra o circuito equivalente.

Figura 2.11 – Circuito da segunda etapa de operação do inversor ( $t_1 - t_2$ ).

Fonte: Dados do próprio autor.

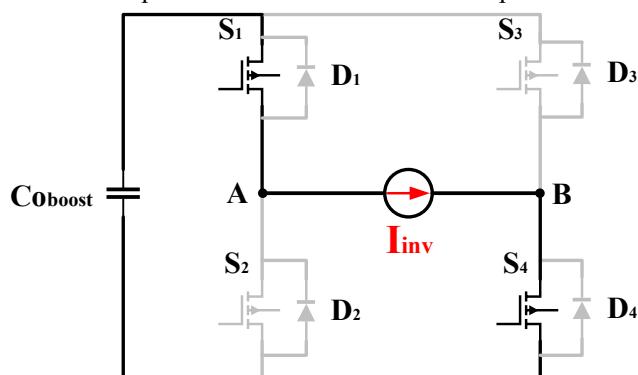

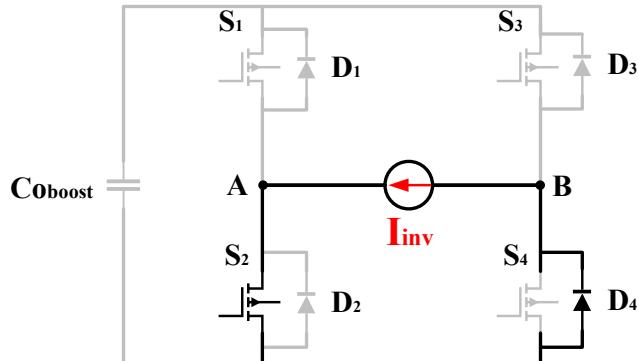

- Terceira etapa:  $\Delta t_3 [t_2-t_3]$ :

É iniciada quando, no tempo  $t_2$ , a chave  $S_2$  e  $S_3$  assumem a corrente da carga e termina, no tempo  $t_3$ , quando as chaves são  $S_2$  e  $S_3$  são comandadas para abrir e as chaves  $S_1$  e  $S_4$  são colocadas em condução. O circuito equivalente deste estágio pode ser observado na Figura 2.12.

Figura 2.12 – Circuito da terceira etapa de operação do inversor ( $t_2 - t_3$ ).

Fonte: Dados do próprio autor.

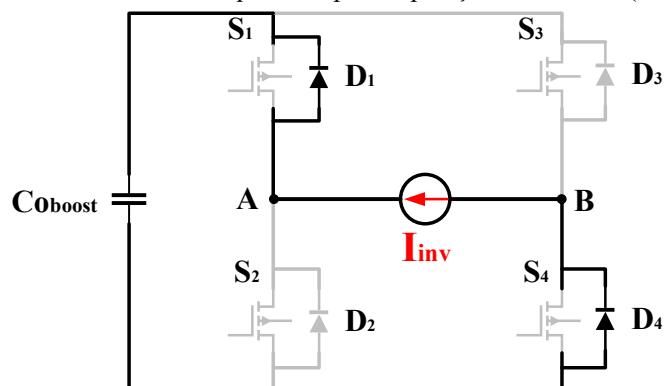

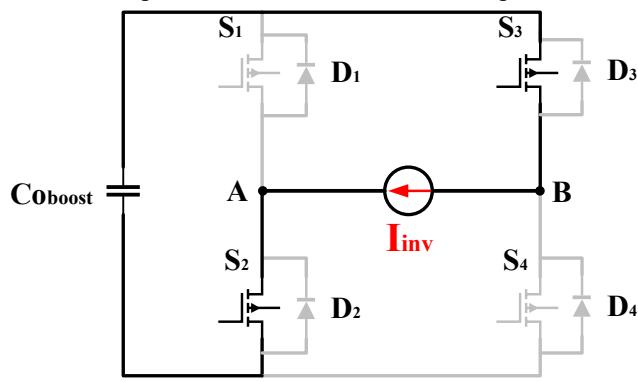

- **Quarta etapa:  $\Delta t_4$  [t<sub>3</sub>-t<sub>4</sub>]:**

Esse estágio é análogo à segunda etapa e inicia-se no tempo t<sub>3</sub>, quando as chaves S<sub>2</sub> e S<sub>3</sub> são comandadas para abrir e as chaves S<sub>1</sub> e S<sub>4</sub> são comandadas para fechar. Como a corrente não muda de sentido neste semiciclo, os diodos D<sub>1</sub> e D<sub>4</sub> são polarizados diretamente e assumem a corrente de carga I<sub>inv</sub>. A fase termina no tempo t<sub>4</sub>, quando as chaves S<sub>1</sub> e S<sub>4</sub> assumem a corrente da carga, iniciando o ciclo de comutação novamente. Assim, na Figura 2.13 é demonstrado o circuito equivalente desta etapa. A Figura 2.14 ilustra as formas de onda teóricas das tensões nos principais elementos do conversor, em um período de chaveamento.

Figura 2.13 – Circuito da quarta etapa de operação do inversor (t<sub>3</sub> – t<sub>4</sub>).

Fonte: Dados do próprio autor.

Figura 2.14 – Forma de onda da tensão V<sub>AB</sub> para modulação bipolar

Fonte: Dados do próprio autor.

### 2.6.2 ETAPAS DE OPERAÇÃO – PWM UNIPOLAR

A topologia do inversor ponte completa com a modulação PWM senoidal unipolar apresenta oito etapas de operação, sendo elas: quatro para o semiciclo positivo da tensão de saída em um período de comutação e as quatro restantes para o semiciclo negativo da tensão de saída. A Figura 2.15 apresenta o comportamento da tensão  $V_{AB}$  na saída do inversor e o chaveamento de cada interruptor utilizando a modulação proposta.

Figura 2.15 – Modulação PWM senoidal unipolar

Fonte: Dados do próprio autor.

A Tabela 2.2 tem o objetivo de mostrar resumidamente o princípio de operação do inversor PWM unipolar.

Tabela 2.2 - Operação do conversor com modulação PWM senoidal unipolar

| Semiciclo positivo |                                                     |                                  |                                                  |                        |

|--------------------|-----------------------------------------------------|----------------------------------|--------------------------------------------------|------------------------|

| Etapa              | Comparação                                          | Em condução                      | Bloqueados                                       | Tensão V <sub>AB</sub> |

| Primeira           | $V_m(t) \geq V_{cr}(t)$<br>$V_m(t) \leq V_{cr-}(t)$ | S <sub>1</sub> e S <sub>4</sub>  | S <sub>2</sub> e S <sub>3</sub>                  | +V <sub>Cobooost</sub> |

| Segunda            | $V_m(t) \geq V_{cr}(t)$<br>$V_m(t) \geq V_{cr-}(t)$ | S <sub>1</sub> e Ds <sub>3</sub> | S <sub>2</sub> , S <sub>3</sub> e S <sub>4</sub> | Zero                   |

| Terceira           | $V_m(t) \geq V_{cr}(t)$<br>$V_m(t) \leq V_{cr-}(t)$ | S <sub>1</sub> e S <sub>4</sub>  | S <sub>2</sub> e S <sub>3</sub>                  | +V <sub>Cobooost</sub> |

| Quarta             | $V_m(t) \leq V_{cr}(t)$<br>$V_m(t) \leq V_{cr-}(t)$ | S <sub>4</sub> e Ds <sub>2</sub> | S <sub>1</sub> , S <sub>2</sub> e S <sub>3</sub> | Zero                   |

| Semiciclo negativo |                                                     |                                  |                                                  |                        |

| Etapa              | Comparação                                          | Em condução                      | Bloqueados                                       | Tensão V <sub>AB</sub> |

| Primeira           | $V_m(t) \leq V_{cr}(t)$<br>$V_m(t) \geq V_{cr-}(t)$ | S <sub>2</sub> e S <sub>3</sub>  | S <sub>1</sub> e S <sub>6</sub>                  | -V <sub>Cobooost</sub> |

| Segunda            | $V_m(t) \leq V_{cr}(t)$<br>$V_m(t) \geq V_{cr-}(t)$ | S <sub>2</sub> e Ds <sub>4</sub> | S <sub>1</sub> , S <sub>3</sub> e S <sub>4</sub> | Zero                   |

| Terceira           | $V_m(t) \leq V_{cr}(t)$<br>$V_m(t) \geq V_{cr-}(t)$ | S <sub>2</sub> e S <sub>3</sub>  | S <sub>1</sub> e S <sub>4</sub>                  | -V <sub>Cobooost</sub> |

| Quarta             | $V_m(t) \geq V_{cr}(t)$<br>$V_m(t) \geq V_{cr-}(t)$ | S <sub>3</sub> e Ds <sub>2</sub> | S <sub>1</sub> , S <sub>2</sub> e S <sub>4</sub> | Zero                   |

Fonte: Dados do próprio autor.

- **Primeira etapa:  $\Delta t_1$  [t<sub>0</sub>-t<sub>1</sub>]:** Tensão positiva para o semiciclo positivo da tensão de saída.

No instante inicial t<sub>0</sub>, apenas os interruptores S<sub>1</sub> e S<sub>4</sub> estão em condução como mostra a Figura 2.16. Dessa forma, conectando a carga e o filtro LC diretamente à fonte de alimentação V<sub>Cobooost</sub>. A corrente no barramento CC é positiva, com isso a fonte de alimentação entrega energia para a carga e para o filtro LC. A tensão de saída V<sub>AB</sub> assume valor igual à V<sub>Cobooost</sub>. O término da etapa acontece com o desligamento do interruptor S<sub>4</sub>. A parte em cinza em todos os desenhos que seguem, indicam as partes do circuito que não atuam ativamente na etapa em questão.

Figura 2.16 – Primeira etapa de funcionamento do inversor para o semiciclo positivo

Fonte: Dados do próprio autor.

- **Segunda etapa:  $\Delta t_2$  [ $t_1-t_4$ ]:** Tensão zero para semiciclo positivo da tensão de saída.

No instante  $t=t_1$ , o interruptor  $S_4$  é bloqueado e  $S_3$  é comandado a conduzir,  $S$  continua conduzindo e a corrente que circula pelo indutor mantém a sua direção, assim polarizando o diodo em antiparalelo do interruptor, iniciando a segunda etapa. Nota-se que devido ao sentido da corrente na carga, o interruptor  $S_3$  não chega a conduzir, mesmo comandado em  $t=t_2$ . A corrente no indutor decresce, pois, a energia armazenada nele é entregue à fonte e à carga. A tensão de saída  $V_{AB}$  assume o valor zero nessa fase. Esse processo acaba com a condução de  $S_4$  novamente. A segunda etapa de operação é mostrada na Figura 2.17.

Figura 2.17 – Segunda etapa de funcionamento do inversor para o semiciclo positivo

Fonte: Dados do próprio autor.

- **Terceira etapa:  $\Delta t_3$  [t<sub>4</sub>-t<sub>5</sub>]:** Tensão positiva para o semiciclo positivo da tensão de saída.

Nesse período, é mostrado na Figura 2.18, no instante  $t=t_3$ , o interruptor  $S_2$  bloqueado e em  $t=t_4$ , o mesmo  $S_4$  volta a conduzir conectando novamente a carga e o filtro LC diretamente à fonte de alimentação. Do mesmo jeito que acontece na primeira etapa, a corrente no indutor cresce e a tensão de saída  $V_{AB}$  volta a ter o valor do barramento CC. O término da etapa é com a abertura de  $S_1$ .

Figura 2.18 – Terceira etapa de funcionamento do inversor para o semiciclo positivo.

Fonte: Dados do próprio autor.

- **Quarta etapa:  $\Delta t_4$  [t<sub>5</sub>-t<sub>8</sub>]:** Tensão zero para semiciclo positivo da tensão de saída.

Essa é a última etapa para o semiciclo positivo. No instante  $t = t_5$ , o interruptor  $S_1$  é bloqueado e a corrente no indutor não muda de sentido instantaneamente e passa a circular pelo diodo em antiparalelo do interruptor  $S_2$ . A corrente diminui, pois, a energia armazenada no indutor é entregue para a carga. O interruptor  $S_2$ , apesar de comandado em  $t = t_6$ , não chega a conduzir devido ao sentido da corrente. A Fig. 2.19 elucida o processo.

Figura 2.19 – Quarta etapa de funcionamento do inversor para o semiciclo positivo.

Fonte: Dados do próprio autor.

Em  $t = t_7$  o interruptor  $S_2$  é bloqueado e em  $t = t_8$  o interruptor  $S_1$  é novamente comandado a conduzir assumindo a corrente que circulava pelo diodo  $D_2$ . Tem-se novamente a primeira etapa de operação.

- **Primeira etapa:**  $\Delta t_1 [t_0-t_1]$ : Tensão negativa para o semiciclo negativo da tensão de saída.

No instante  $t_0$ , somente os interruptores  $S_2$  e  $S_3$  estão em condução como mostrado na Figura 2.20. Assim, conecta a carga e o filtro LC com a fonte de alimentação. A corrente no barramento CC é positiva, com isso a fonte de alimentação entrega energia para a carga e para o filtro LC. A tensão de saída  $V_{AB}$  tem o valor do barramento CC. O fim dessa etapa é com o desligamento do interruptor  $S_3$ .

Figura 2.20 – Primeira etapa de funcionamento do inversor para o semiciclo negativo

Fonte: Dados do próprio autor.

- **Segunda etapa:**  $\Delta t_2 [t_1-t_4]$ : Tensão zero para semiciclo negativo da tensão de saída.

No instante  $t=t_2$ , o interruptor  $S_3$  é aberto e  $S_4$  comandado a conduzir,  $S_2$  segue fechado. A corrente que circula pelo indutor mantém a sua direção, assim polarizando o diodo em antiparalelo do interruptor  $S_4$ . A corrente no indutor diminui, pois, a energia armazenada nele é entregue à fonte e à carga. A tensão de saída  $V_{AB}$  assume o valor zero e esse ciclo acaba com o fechamento de  $S_3$ . Essa operação é mostrada na Figura 2.21.

Figura 2.21 – Segunda etapa de funcionamento do inversor para o semiciclo negativo

Fonte: Dados do próprio autor.

- **Terceira etapa:  $\Delta t_3 [t_4-t_5]$ :** Tensão negativa para o semiciclo negativo da tensão de saída.

Na Figura 2.22, no instante  $t=t_3$ , o interruptor  $S_3$  é comandado a conduzir, conectando da mesma forma da primeira etapa a carga e o filtro LC diretamente à fonte de alimentação. A corrente no indutor cresce e a tensão de saída  $V_{AB}$  volta a ter o valor do barramento CC. O término da etapa é com a abertura de  $S_2$ .

Figura 2.22 – Terceira etapa de funcionamento do inversor para o semiciclo negativo

Fonte: Dados do próprio autor.

- **Quarta etapa:  $\Delta t_4 [t_5-t_8]$ :** Tensão zero para semiciclo negativo da tensão de saída.