UNIVERSIDADE FEDERAL DE UBERLÂNDIA

FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

**PROJETO E ANÁLISE DE UM CONVERSOR CA-CC MONOFÁSICO BOOST

ENTRELAÇADO SEM PONTE DE DIODOS E COM CORREÇÃO ATIVA DO

FATOR DE POTÊNCIA EMPREGANDO A TÉCNICA DE IMPOSIÇÃO DE

CORRENTE MÉDIA**

JULIO AUGUSTO BORGES

Uberlândia

2019

JULIO AUGUSTO BORGES

**PROJETO E ANÁLISE DE UM CONVERSOR CA-CC MONOFÁSICO BOOST

ENTRELAÇADO SEM PONTE DE DIODOS E COM CORREÇÃO ATIVA DO

FATOR DE POTÊNCIA EMPREGANDO A TÉCNICA DE IMPOSIÇÃO DE

CORRENTE MÉDIA**

Dissertação de mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), perante a banca de examinadores abaixo, como parte dos requisitos necessários para a obtenção do título de mestre em Ciências.

Área de concentração: Sistema de energia elétrica.

Orientador: Dr. Luiz Carlos Gomes de Freitas.

Banca Examinadora:

Luiz Carlos Gomes de Freitas, Dr. – Orientador (UFU)

Gustavo Brito de Lima, Dr. (UFU)

Danilo Borges Rodrigues, Dr. (UFTM)

A Bolsa de Estudos, para esta pesquisa, foi concedida pela CAPES, Brasil.

Uberlândia

2019

Dados Internacionais de Catalogação na Publicação (CIP)

Sistema de Bibliotecas da UFU, MG, Brasil.

---

B732p

2019

Borges, Julio Augusto, 1992-

Projeto e análise de um conversor CA-CC monofásico boost entrelaçado sem ponte de diodos e com correção ativa do fator de potência empregando a técnica de imposição de corrente média [recurso eletrônico] / Julio Augusto Borges. - 2019.

Orientador: Luiz Carlos Gomes de Freitas.

Dissertação (mestrado) - Universidade Federal de Uberlândia, Programa de Pós-Graduação em Engenharia Elétrica.

Modo de acesso: Internet.

Disponível em: <http://dx.doi.org/10.14393/ufu.di.2019.365>

Inclui bibliografia.

Inclui ilustrações.

1. Engenharia elétrica. 2. Conversores de corrente elétrica. 3. Eletrônica de potência. I. Freitas, Luiz Carlos Gomes de, 1976- (Orient.) II. Universidade Federal de Uberlândia. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

---

CDU: 621.3

Maria Salete de Freitas Pinheiro - CRB6/1262

JULIO AUGUSTO BORGES

**PROJETO E ANÁLISE DE UM CONVERSOR CA-CC MONOFÁSICO BOOST

ENTRELAÇADO SEM PONTE DE DIODOS E COM CORREÇÃO ATIVA DO

FATOR DE POTÊNCIA EMPREGANDO A TÉCNICA DE IMPOSIÇÃO DE

CORRENTE MÉDIA**

Dissertação de mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), como parte dos requisitos necessários para a obtenção do título de mestre em Ciências.

---

Prof. Dr. Luiz Carlos Gomes de Freitas

Orientador

---

Prof. Dr. José Rubens Macedo Júnior

Coordenador da Pós-Graduação

Uberlândia

2019

## **DEDICATÓRIA**

*À minha mãe Heloisa,

À minha namorada Ana Clara,

À toda minha família e meus amigos.*

## AGRADECIMENTOS

Agradeço primeiramente a Deus por nos amar primeiro, e por ter demonstrado esse imenso amor enviando seu filho, Jesus, para nos salvar. Obrigado Senhor por ter me capacitado até aqui.

Agradeço à minha mãe Heloisa que sempre esteve ao meu lado me apoiando e me guiando, sempre buscando o melhor pra mim. Obrigado por nunca ter medido esforços para me ajudar a todos os momentos.

Agradeço ao meu pai José Ronaldo que enquanto esteve ao meu lado sempre me amou de maneira incondicional e sempre me incentivou a dar meu melhor em busca de meus objetivos.

Agradeço à minha namorada Ana Clara que me apoia, me dá forças e me faz querer ser uma pessoa melhor a cada dia. Obrigado por seu amor, atenção e carinho. Obrigado também porque, juntos, podemos compartilhar nossos sonhos e busca-lo sempre unidos.

Agradeço também ao Aguinaldo pela amizade e apoio, e por ser essa pessoa sempre alegre, carinhosa e companheira.

Agradeço ao meu orientador Luiz Carlos Gomes de Freitas pela confiança e compreensão diante os imprevistos que enfrentei durante a jornada no mestrado.

Agradeço a todos os amigos e companheiros do NUPEP que estiveram comigo no dia a dia dessa caminhada, compartilhando experiências, conhecimentos e muitos momentos de descontração. Um agradecimento especial ao meu amigo Lucas que, além de ser meu companheiro de apartamento, me ajudou muito durante esse trabalho.

Agradeço aos irmãos de armas Marlius e Amaral, que me apoiaram e ajudaram a continuar trabalhando firme mesmo durante o ano atípico que tivemos.

A todos os amigos e familiares que contribuíram direta ou indiretamente na realização desse trabalho, incentivando e torcendo por sua conclusão.

Ao CNPq – Conselho Nacional de Desenvolvimento Científico e Tecnológico, à FAPEMIG - Fundação de Amparo à Pesquisa do Estado de Minas Gerais e à CAPES - Coordenação de Aperfeiçoamento de Pessoal de Nível Superior, pelo suporte financeiro e pela bolsa de mestrado.

O presente trabalho foi realizado com apoio da Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Código de Financiamento 001

*“Porque Deus amou o mundo de tal maneira que deu o seu Filho unigênito, para que todo aquele que nele crê não pereça, mas tenha a vida eterna”.*

***João 3:16***

## **RESUMO**

Este trabalho apresenta o projeto e análise de um Conversor CA-CC Monofásico *Boost* que emprega a técnica de entrelaçamento de células conversoras e não utiliza a ponte retificadora de diodo, que visa a regulação da tensão CC no terminal de saída e a drenagem de uma corrente de entrada em fase com a tensão da rede e com baixo conteúdo harmônico, por meio de uma correção ativa do fator de potência. A modelagem do conversor é feita para o Modo de Condução Contínua (MCC) de Corrente e as funções de transferência são obtidas por meio do modelo médio linearizado em espaço de estados. A estratégia de controle é implementada utilizando a técnica de controle por corrente média, realizando o ajuste da corrente na malha de controle interna e o ajuste da tensão na malha de controle externa. Por fim, faz-se a análise qualitativa e quantitativa do sistema por meio de resultados de simulação, além de uma comparação de perdas apresentadas pelos semicondutores para diferentes topologias *boost*.

**Palavras chaves:** Conversor CA-CC *Boost*, Correção Ativa do Fator de Potência, Entrelaçamento de Células, Modo de Condução Contínua.

## ABSTRACT

This work presents the project and analysis of a AC-DC single-phase Power Factor Corrected Boost Converter, using both the interleaving and bridgeless techniques with the purpose of regulating the DC output voltage and the input current, draining a sinusoidal current in phase with the grid voltage and with a low harmonic content. The modeling is carried out with the converter operating in the Continuous Conduction Mode (CCM) and the transfer functions are obtained using the linearization of nonlinear state space equations. The control strategy is implemented using the Average Current Mode Control, regulating the current in the inner loop and the voltage in the outer loop. Finally, this work presents a qualitative and quantitative analysis of the system using the simulation results, besides a comparison regarding the semiconductors losses presented by different boost topologies.

Keywords: AC-DC Boost Converter, Bridgeless, Continuous Conduction Mode, Interleaving, Power Factor Correction.

## LISTA DE FIGURAS

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Figura 2.1 - Conversor PFP <i>Boost</i> Clássico .....                                              | 22 |

| Figura 2.2 - Formas de onda dos modos de condução de corrente.....                                  | 23 |

| Figura 2.3 - Técnica de entrelaçamento de células <i>bridgeless boost</i> .....                     | 25 |

| Figura 2.4 - Topologia <i>Bridgeless Dual Boost</i> .....                                           | 27 |

| Figura 2.5 - Topologia <i>Bridgeless Boost</i> com chaves bidirecionais. ....                       | 28 |

| Figura 2.6 - Topologia <i>Bridgeless Two-Boost</i> .....                                            | 28 |

| Figura 2.7 - Topologia <i>Bridgeless Totem-Pole</i> .....                                           | 29 |

| Figura 2.8 - Topologia <i>Bridgeless Pseudo Totem-Pole</i> .....                                    | 29 |

| Figura 2.9 - Comparação de perdas por condução entre topologias <i>boost</i> .....                  | 30 |

| Figura 2.10 - Circuito de controle para o método de controle por corrente de pico. ....             | 32 |

| Figura 2.11 - Circuito de controle para o método de controle por corrente média. ....               | 33 |

| Figura 2.12 - Circuito de controle para o método de controle da corrente por histerese.             | 34 |

| Figura 2.13 - Circuito de controle para o método de controle por portadora programada.              |    |

| .....                                                                                               | 35 |

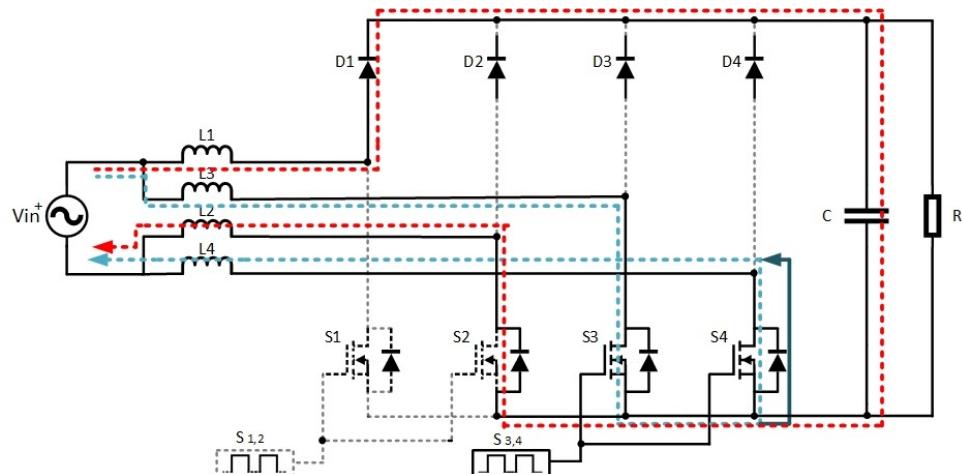

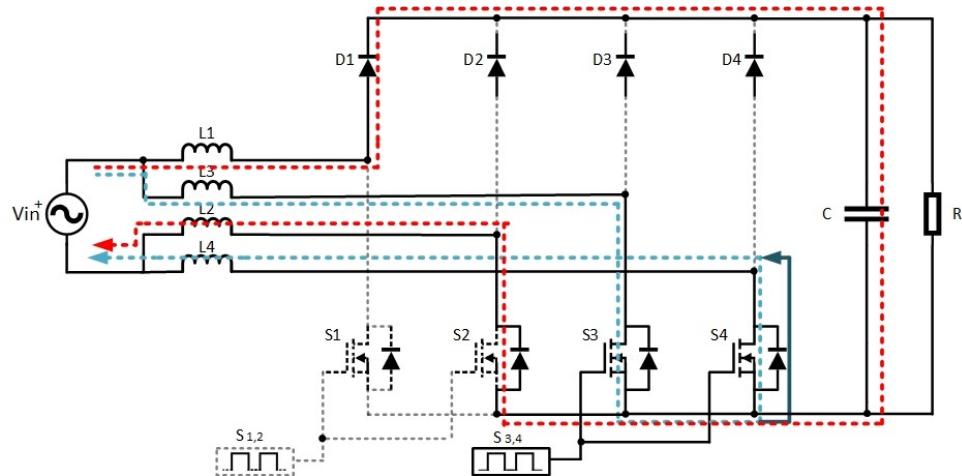

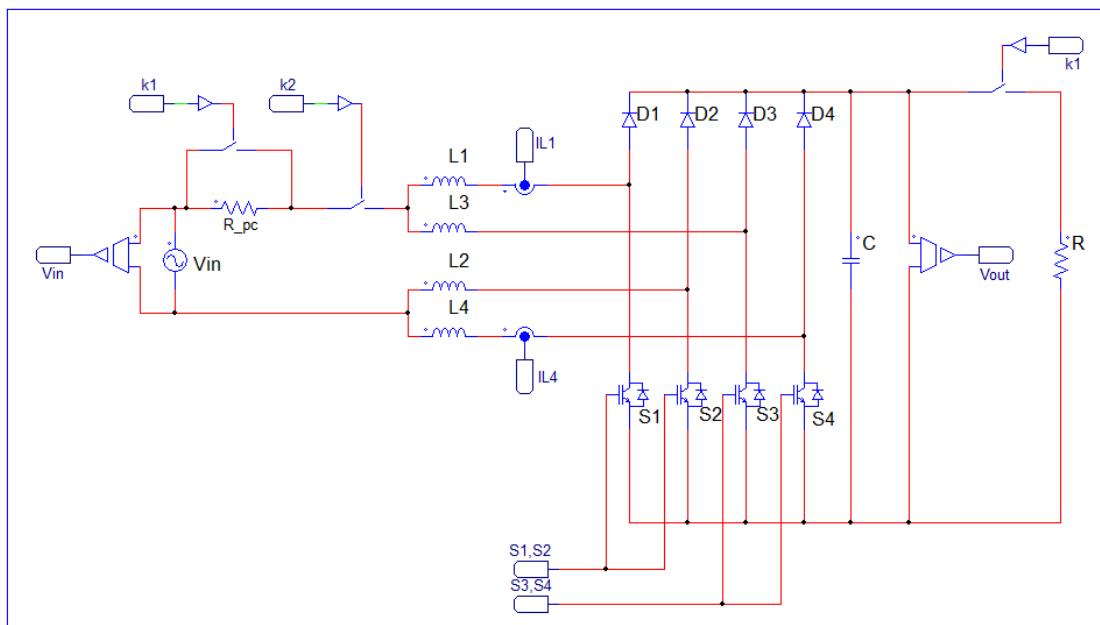

| Figura 3.1 - Conversor CA-CC <i>Boost</i> Entrelaçado Sem Ponte de Diodos.....                      | 37 |

| Figura 3.2 - Intervalo 1: Semicondutores $S_1$ , $S_2$ e diodo em antiparalelo de $S_4$ conduzindo  |    |

| .....                                                                                               | 39 |

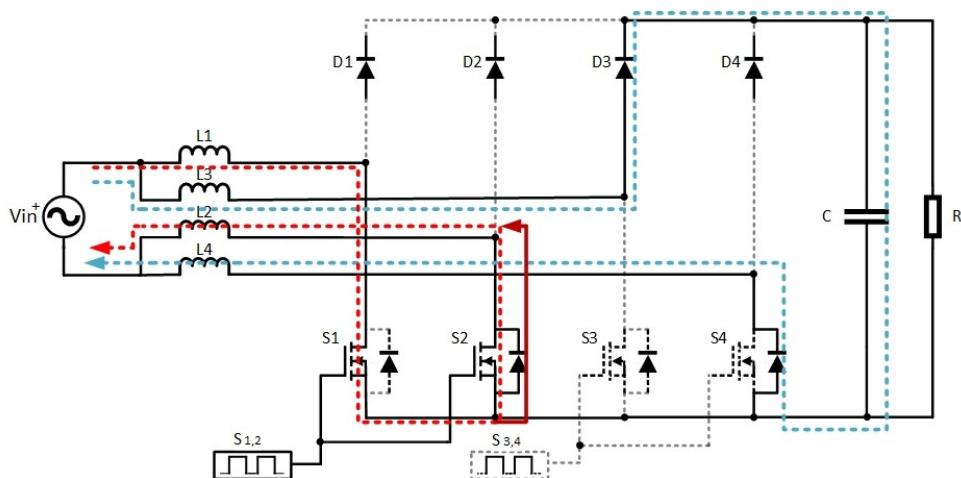

| Figura 3.3 - Intervalo 2 e 4: Semicondutores $S_1$ , $S_2$ , $S_3$ e $S_4$ conduzindo.....          | 40 |

| Figura 3.4 - Intervalo 3: Semicondutores $S_3$ , $S_4$ e diodo em antiparalelo de $S_2$ conduzindo. |    |

| .....                                                                                               | 40 |

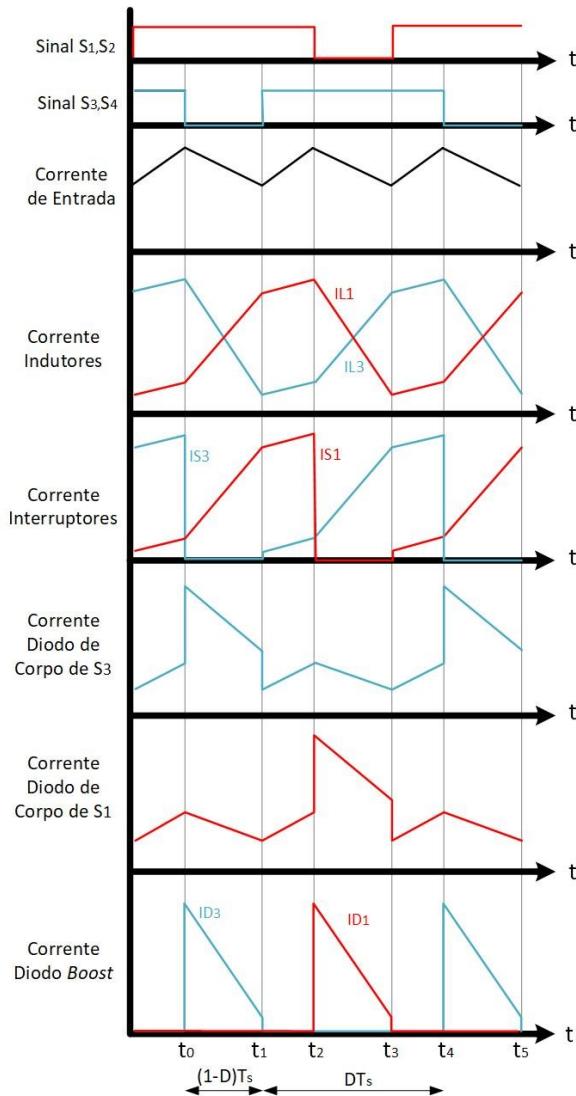

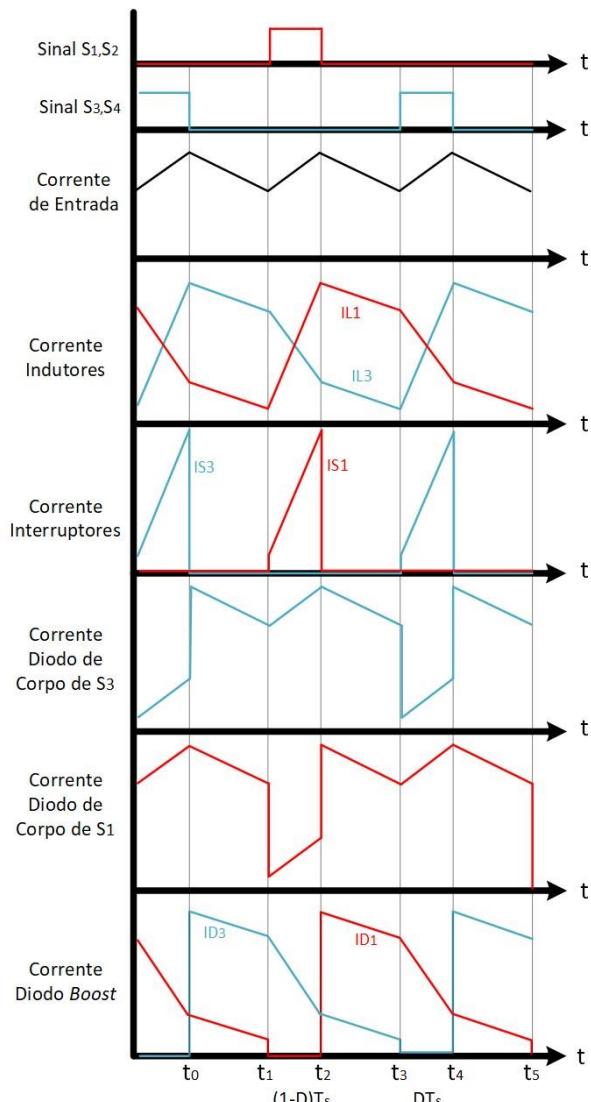

| Figura 3.5 - Formas de onda para razão cíclica maior que 0,5.....                                   | 40 |

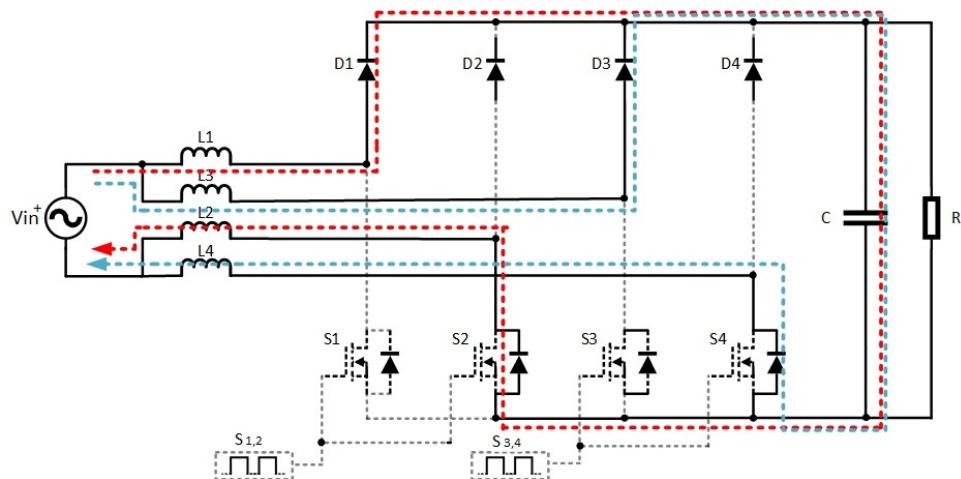

| Figura 3.6 - Intervalo 1 e 3: Diodos em antiparalelo de $S_2$ e $S_4$ conduzindo. ....              | 44 |

| Figura 3.7 - Intervalo 2: Semicondutores $S_1$ , $S_2$ e diodo em antiparalelo de $S_4$ conduzindo. |    |

| .....                                                                                               | 44 |

| Figura 3.8 - Intervalo 4: Semicondutores $S_3$ , $S_4$ e diodo em antiparalelo de $S_2$ conduzindo. |    |

| .....                                                                                               | 45 |

| Figura 3.9 - Formas de onda para razão cíclica menor que 0,5.....                                   | 45 |

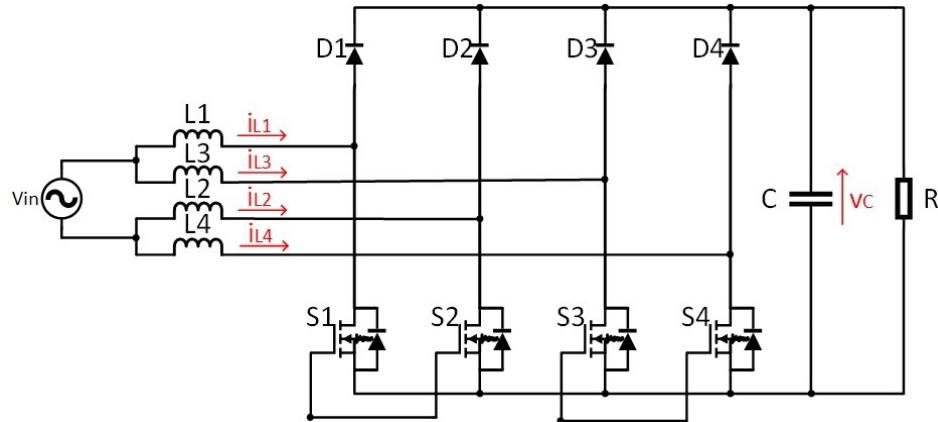

| Figura 4.1 - Variáveis de estado do circuito.....                                                   | 56 |

| Figura 4.2 - Subcírcuito durante o intervalo 1.....                                                 | 58 |

| Figura 4.3 - Subcírcuito durante os intervalos 2 e 4.....                                           | 59 |

| Figura 4.4 - Subcírcuito durante o intervalo 3.....                                                 | 60 |

|                                                                                                                                  |    |

|----------------------------------------------------------------------------------------------------------------------------------|----|

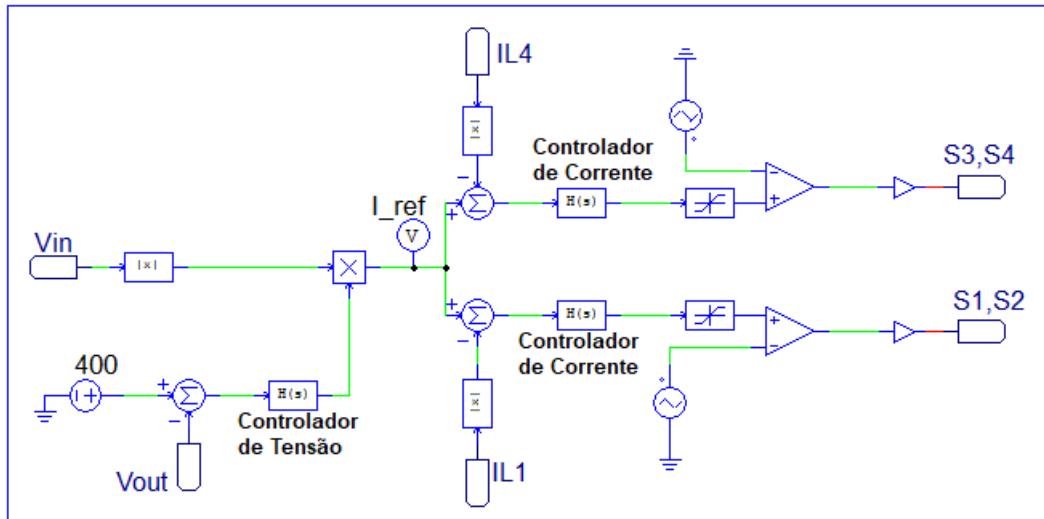

| Figura 4.5 -Diagrama de controle por corrente média para o conversor <i>bridgeless boost</i> com duas células entrelaçadas ..... | 70 |

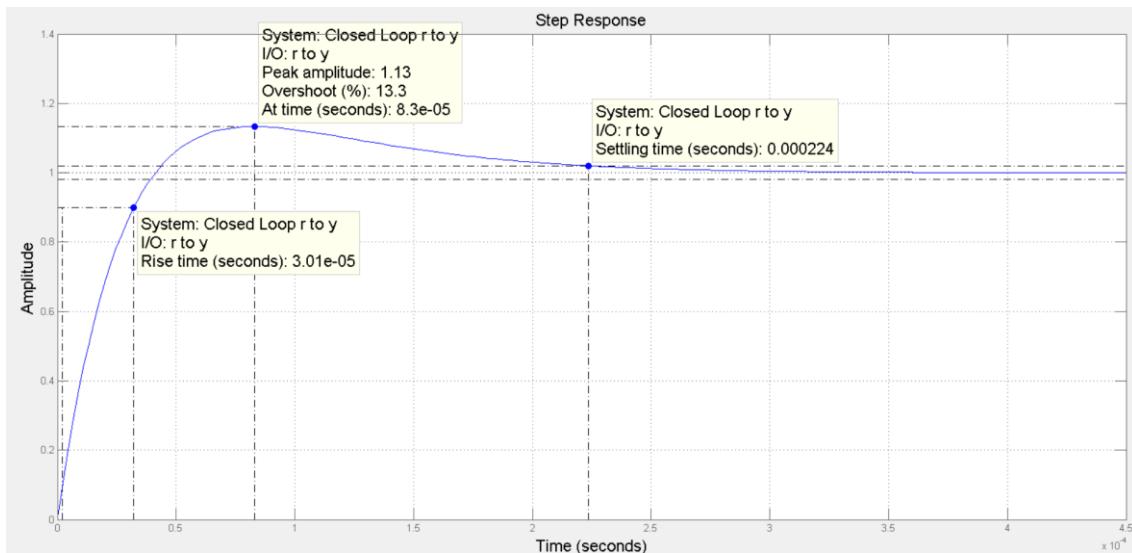

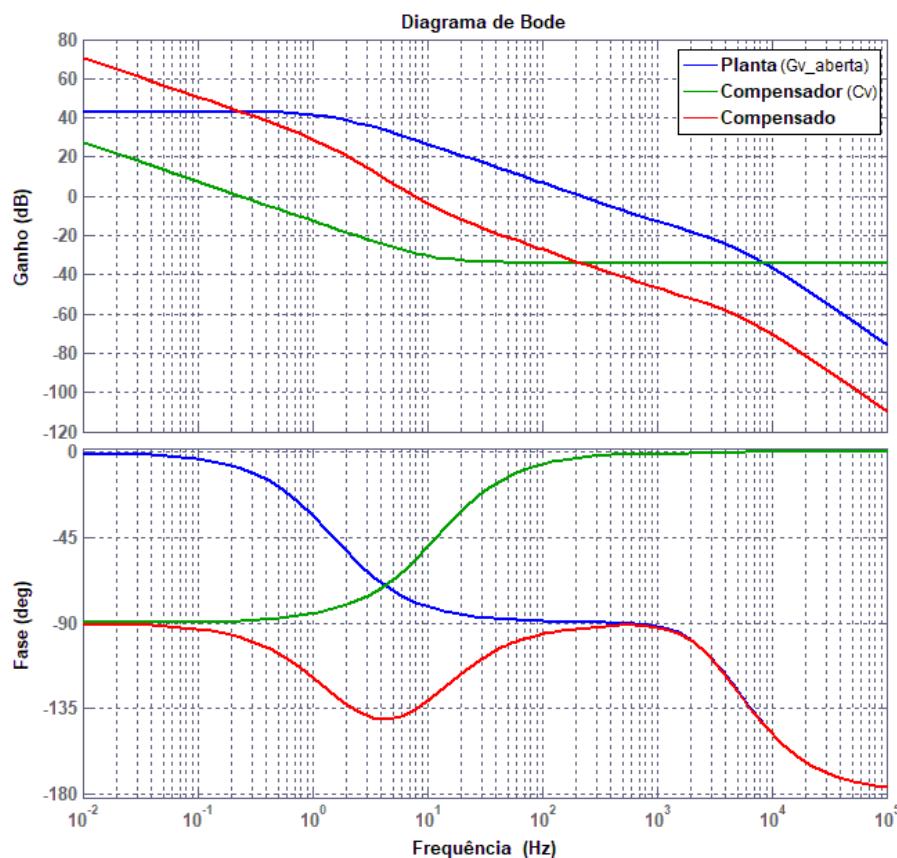

| Figura 4.6 - Diagrama de Bode - Malha Interna.....                                                                               | 72 |

| Figura 4.7 - Resposta da malha de corrente ao degrau.....                                                                        | 73 |

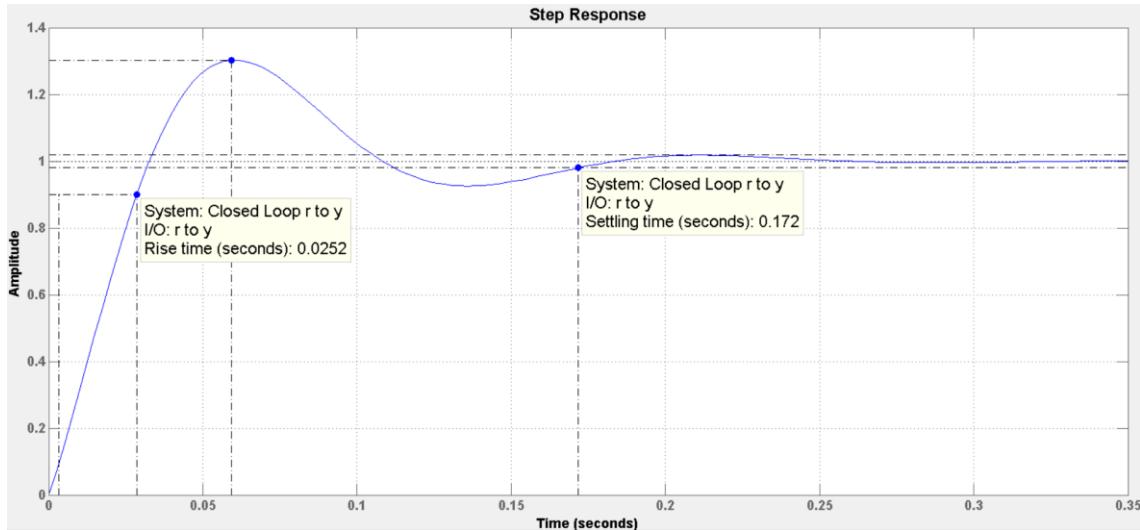

| Figura 4.8 - Diagrama de Bode - Malha Externa. ....                                                                              | 74 |

| Figura 4.9 - Resposta da malha de tensão ao degrau.....                                                                          | 75 |

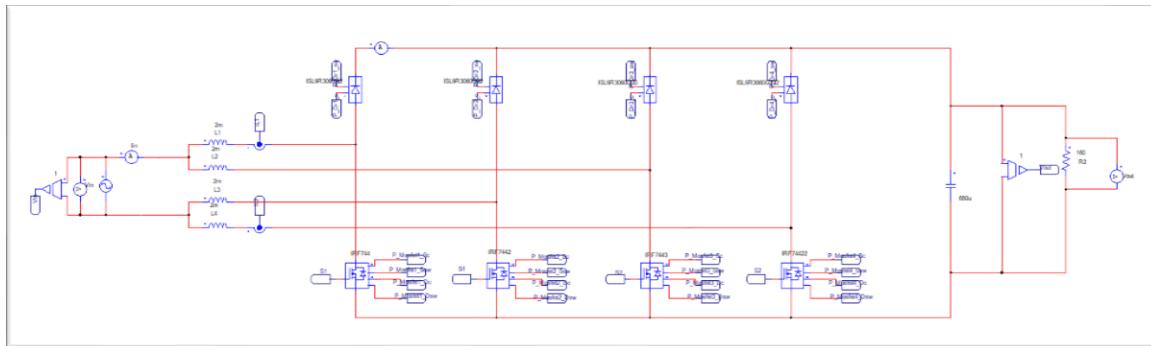

| Figura 5.1 - Circuito de Potência montado no PSIM. ....                                                                          | 77 |

| Figura 5.2 - Circuito de Controle montado no PSIM. ....                                                                          | 78 |

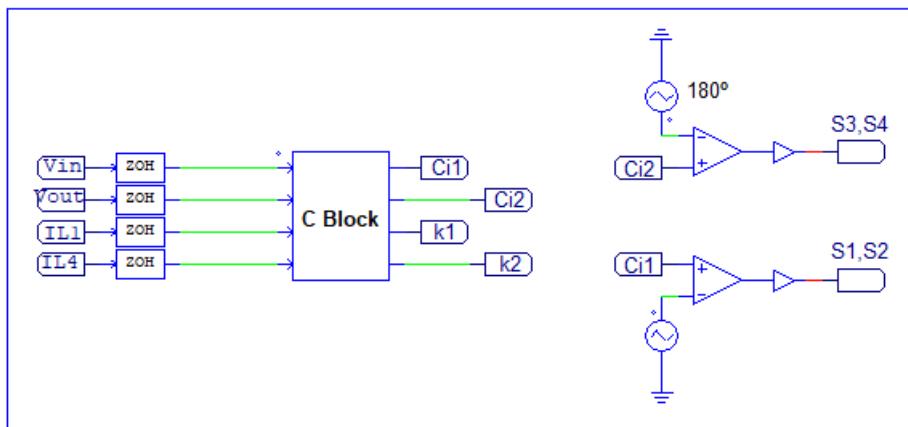

| Figura 5.3 - Circuito de Controle montado utilizando C Block. ....                                                               | 78 |

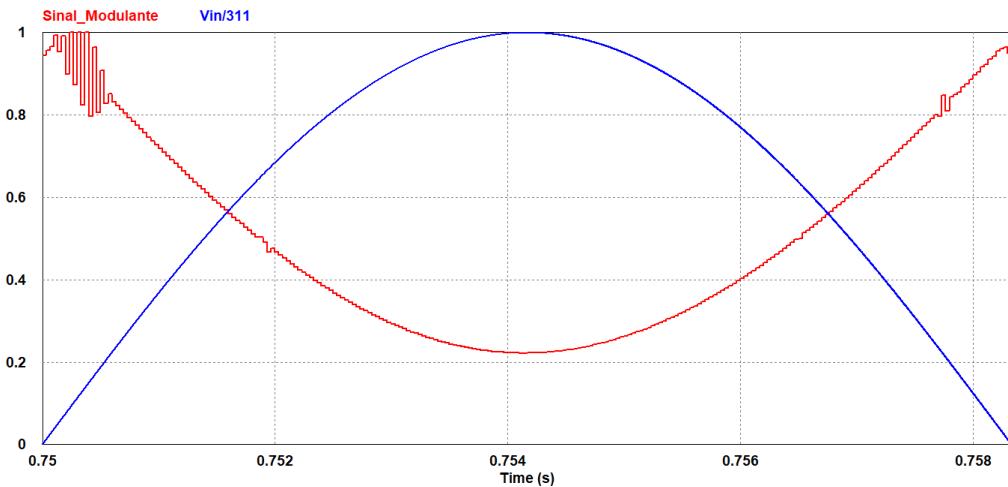

| Figura 5.4 - Sinal modulante em um semiciclo da rede. ....                                                                       | 79 |

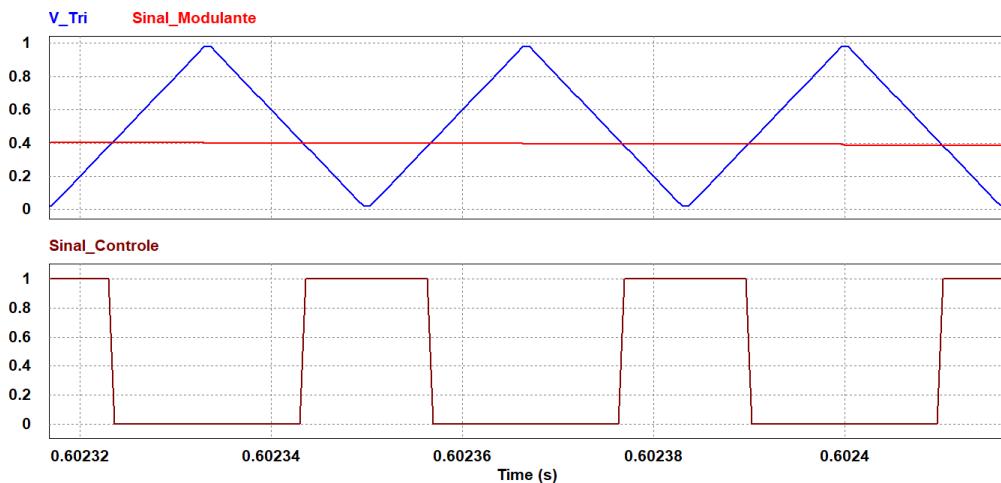

| Figura 5.5 - Modulação por largura de pulso (PWM) em plena carga. ....                                                           | 79 |

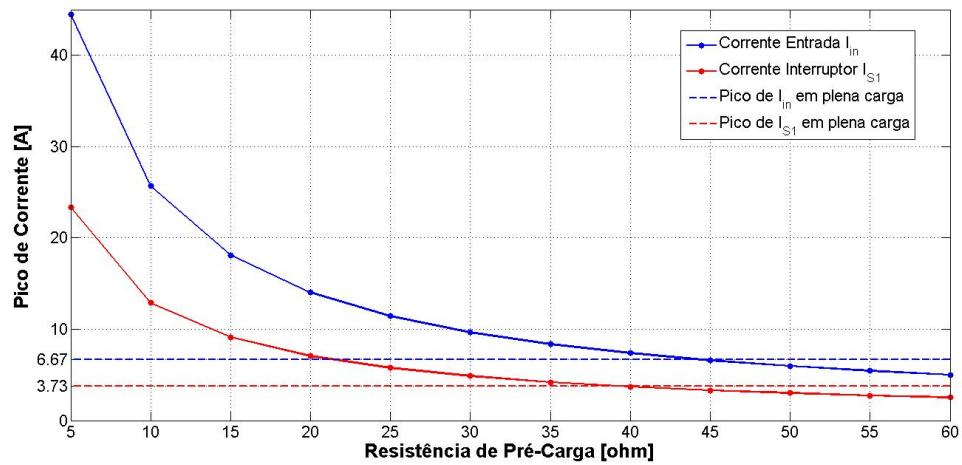

| Figura 5.6 - Pico da corrente na energização em função da resistência de pré-carga ( $R_{pc}$ ).<br>.....                        | 81 |

| Figura 5.7 - Tempo de carga do capacitor em função da resistência de pré-carga.....                                              | 81 |

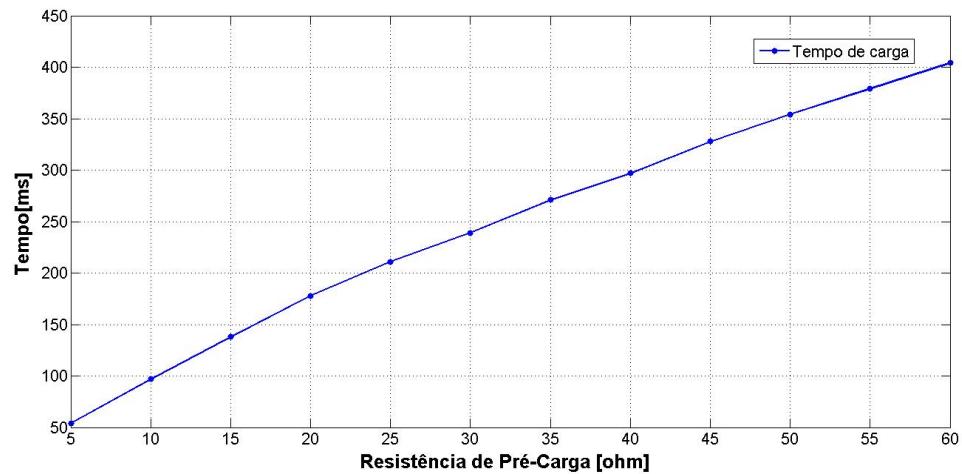

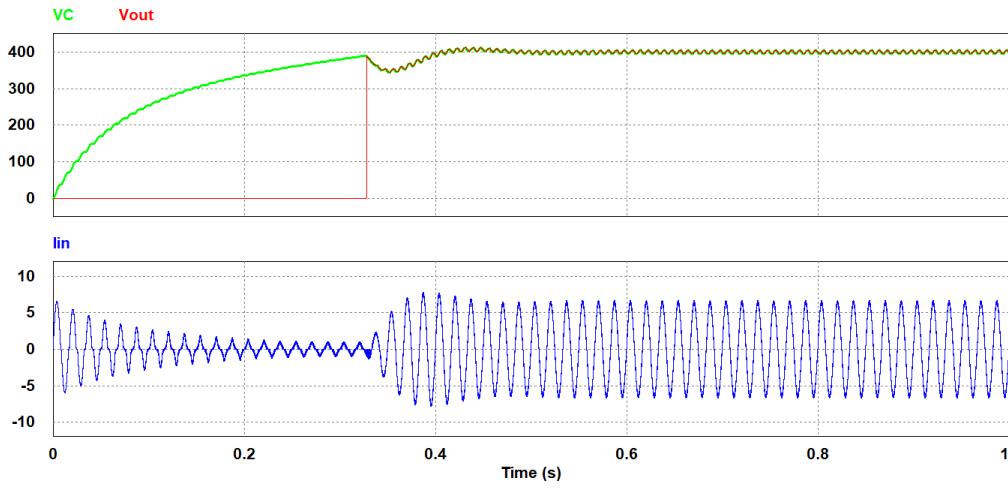

| Figura 5.8 - Tensão sobre o capacitor, tensão de saída e corrente de entrada durante a pré-carga do capacitor.....               | 82 |

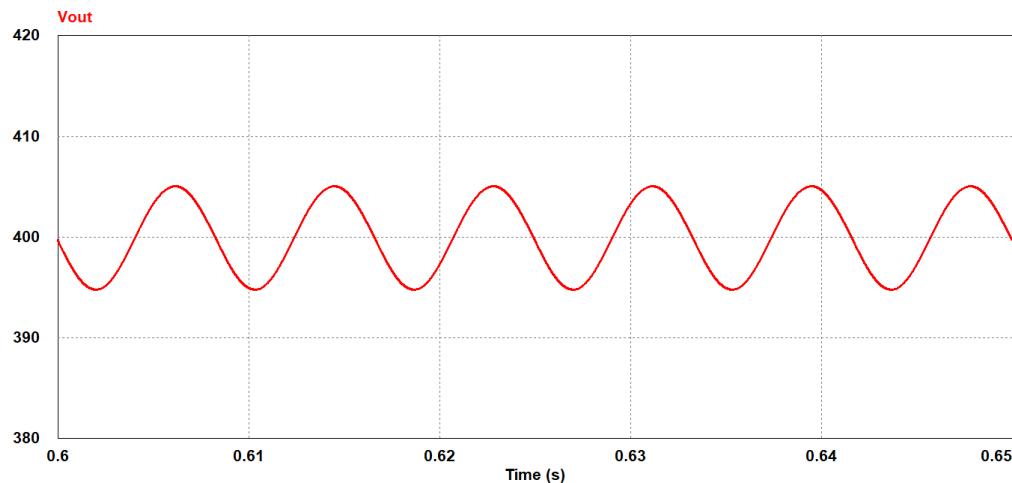

| Figura 5.9 - Tensão de saída na carga. ....                                                                                      | 82 |

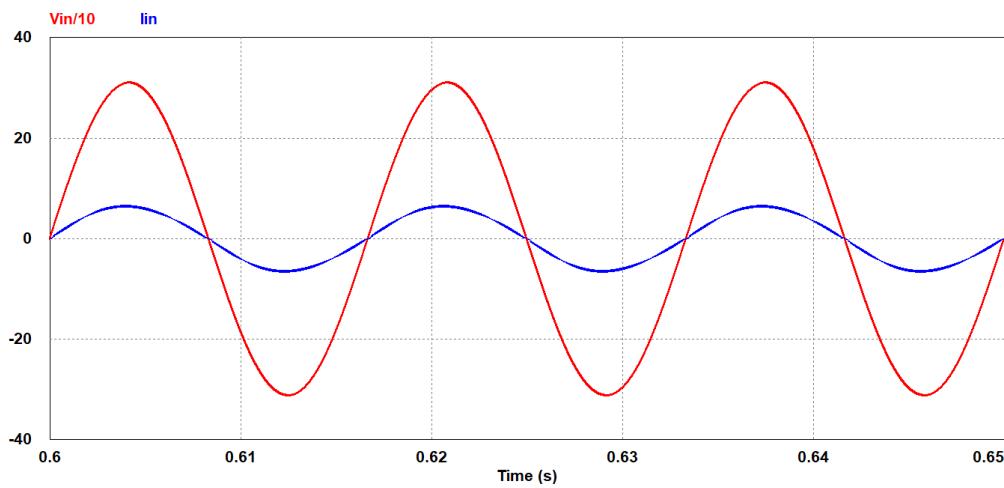

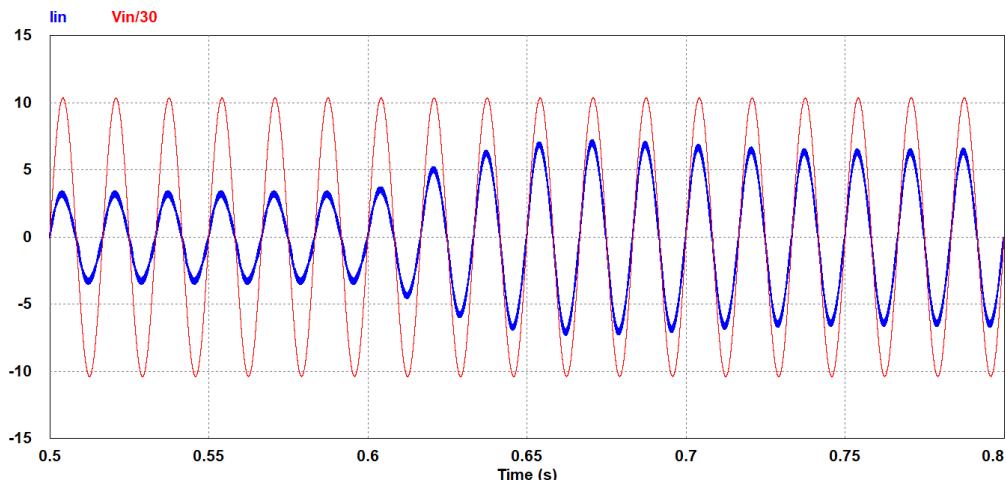

| Figura 5.10 – Tensão (escala 1:10) e corrente de entrada. ....                                                                   | 83 |

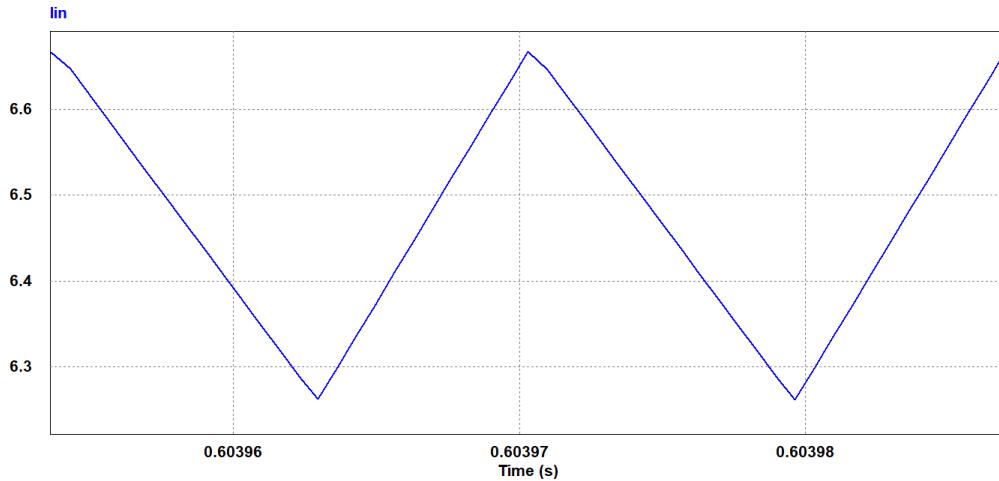

| Figura 5.11 - Detalhe do <i>ripple</i> da corrente de entrada. ....                                                              | 84 |

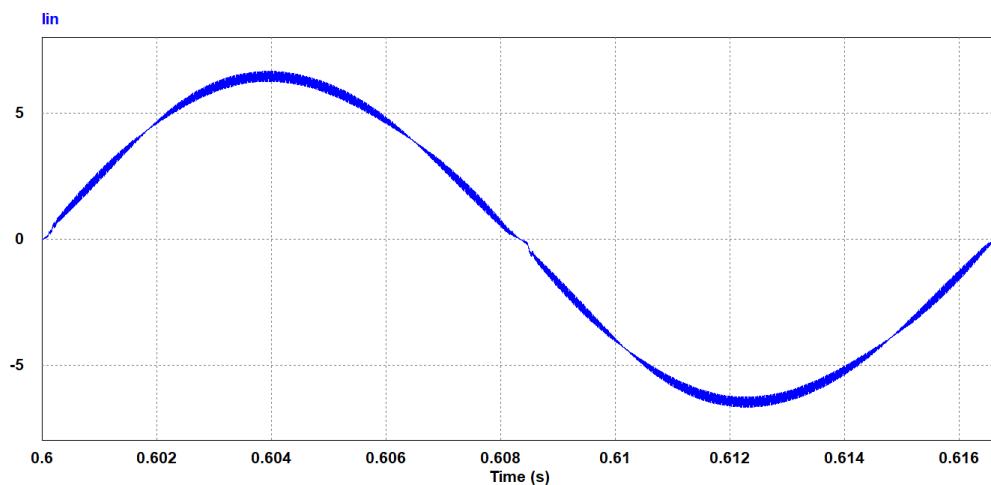

| Figura 5.12 - Corrente de entrada drenada da rede.....                                                                           | 84 |

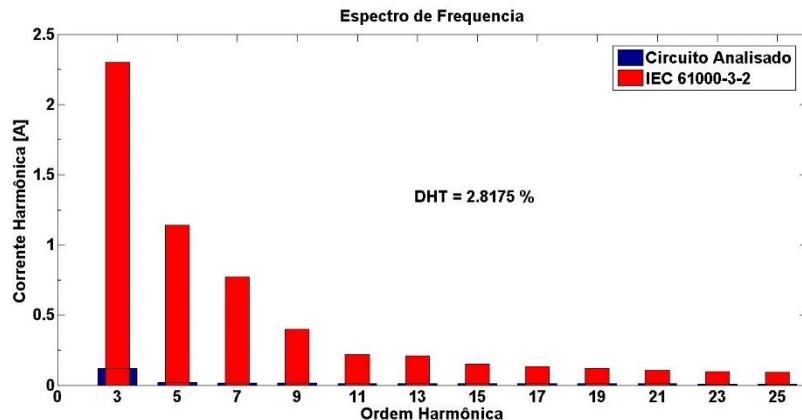

| Figura 5.13 - Componentes harmônicas da corrente de entrada.....                                                                 | 85 |

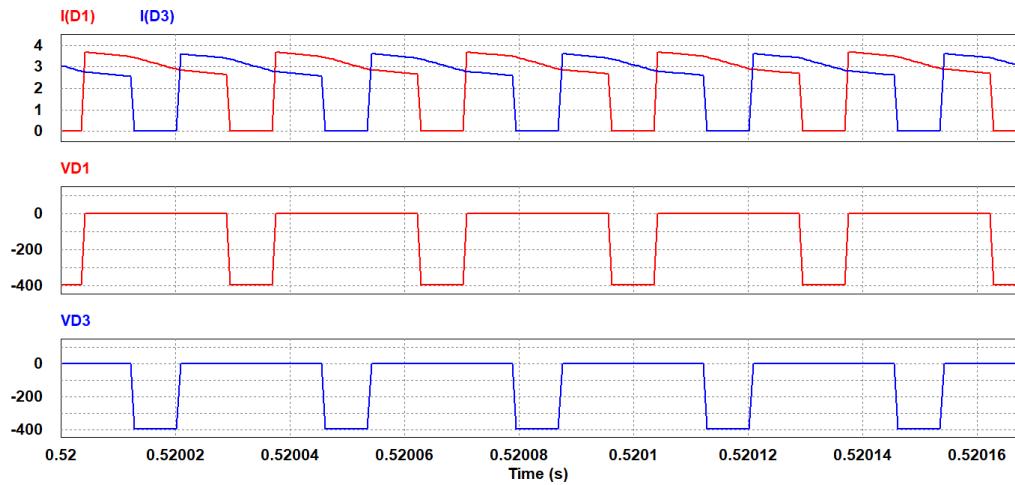

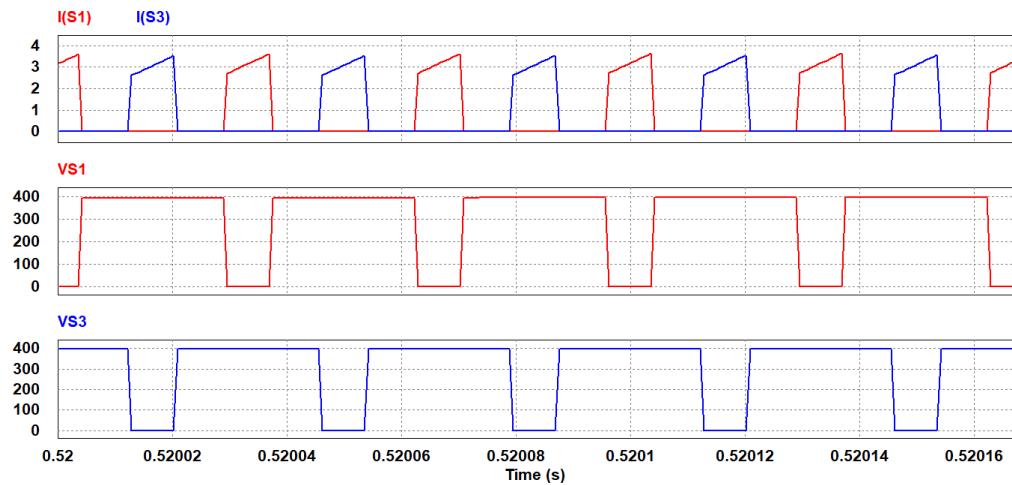

| Figura 5.14 - Corrente instantânea através dos diodos $D_1$ e $D_3$ . ....                                                       | 86 |

| Figura 5.15 - Corrente instantânea através dos interruptores $S_1$ e $S_3$ .....                                                 | 86 |

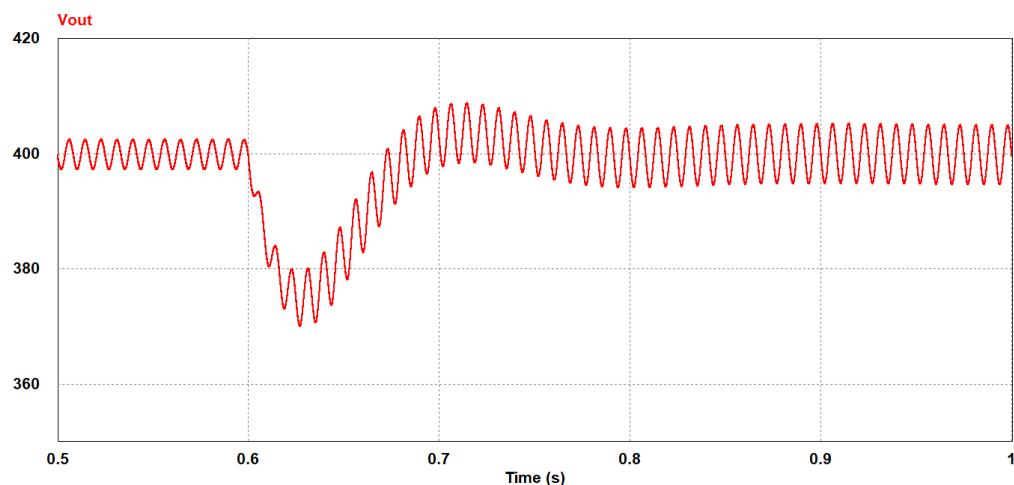

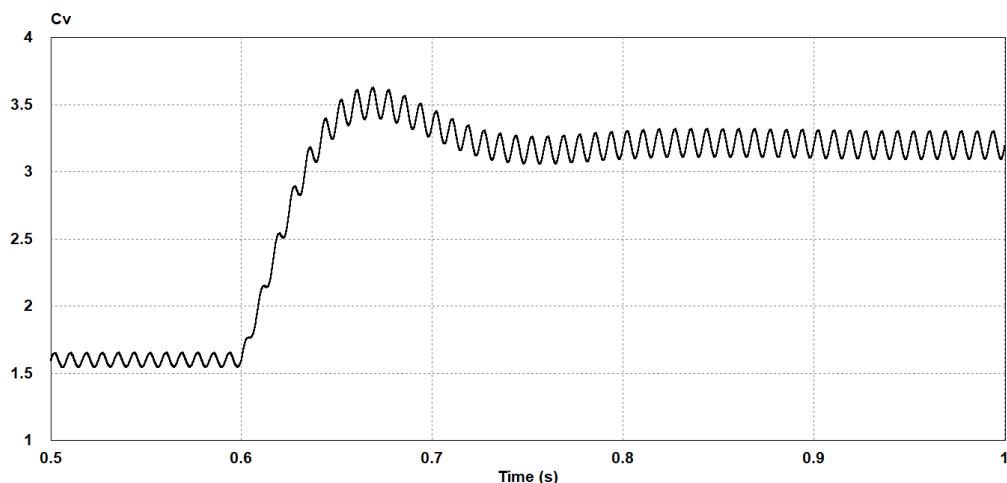

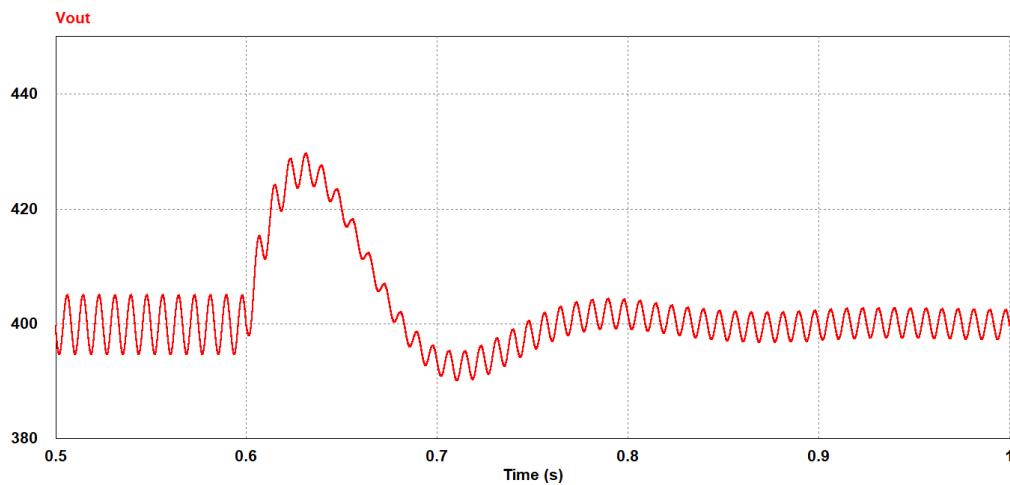

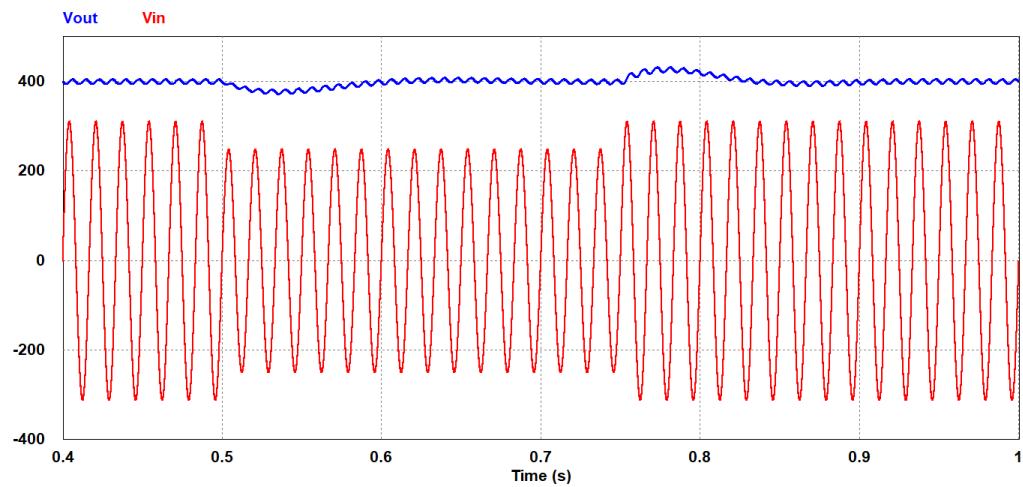

| Figura 5.16 - Tensão de saída para degrau de carga de 50% para 100% da potência nominal.....                                     | 87 |

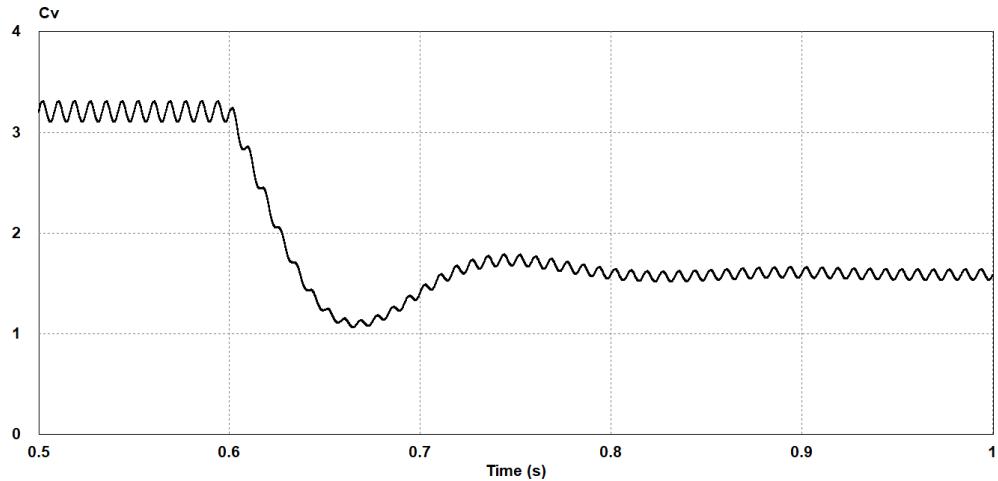

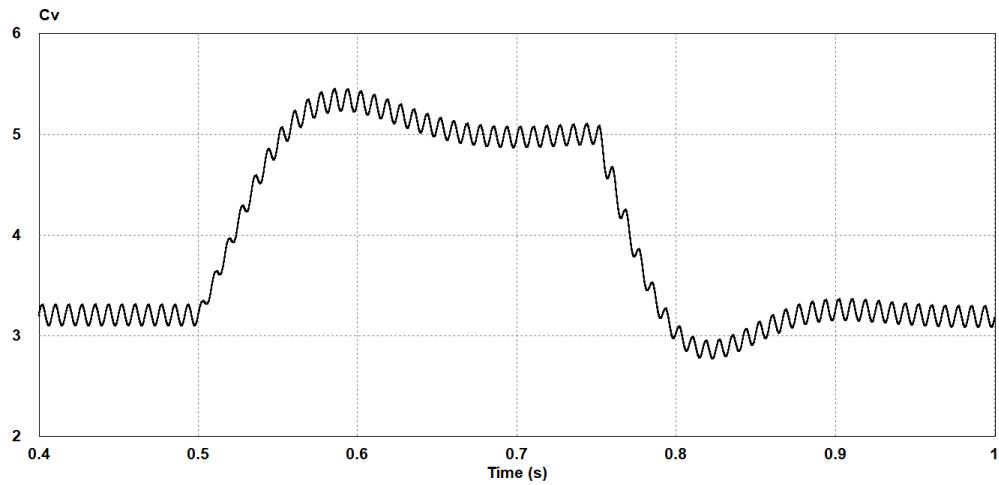

| Figura 5.17 - Resposta do controlador de tensão ao degrau de carga de 50% para 100% da potência nominal.....                     | 87 |

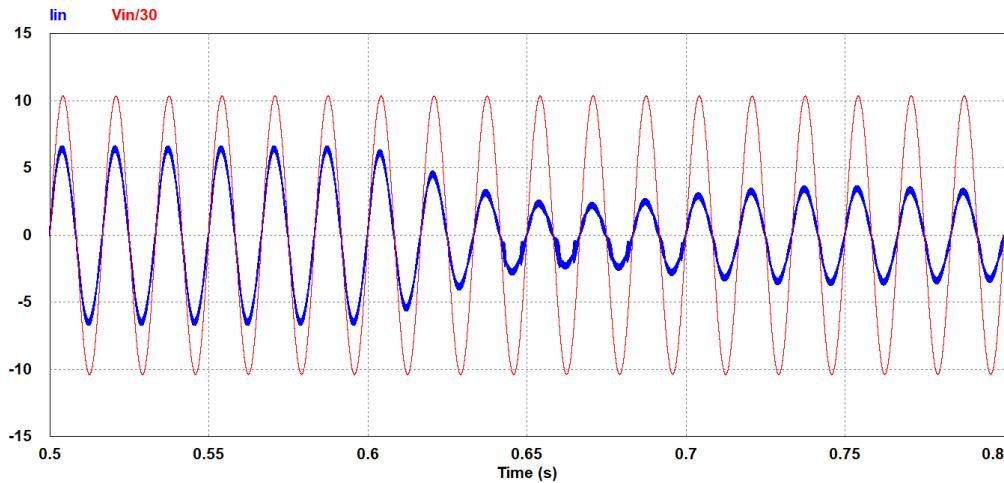

| Figura 5.18 - Corrente de saída para degrau de carga de 50% para 100% da potência nominal.....                                   | 88 |

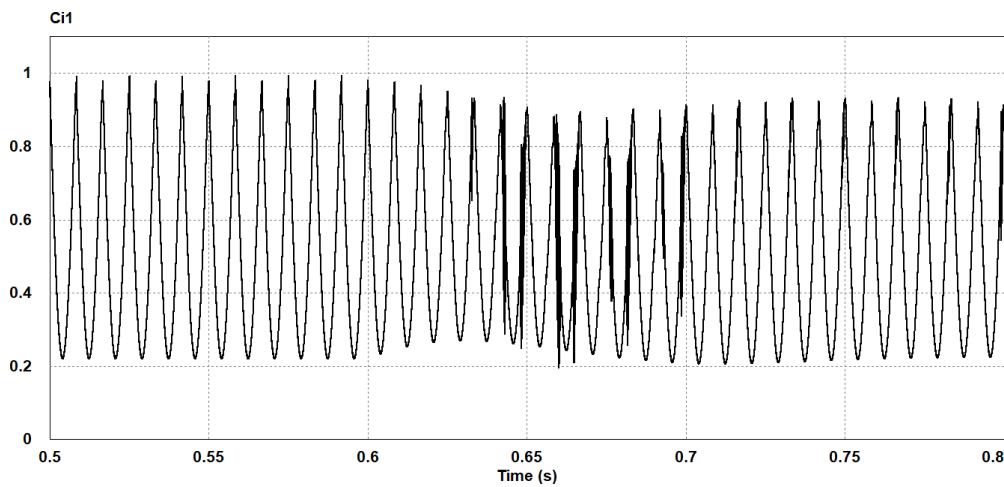

| Figura 5.19 - Resposta do controlador de corrente ao degrau de carga de 50% para 100% da potência nominal.....                   | 89 |

| Figura 5.20 - Tensão de saída para degrau de carga de 100% para 50% da potência nominal.....                                     | 89 |

|                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------|-----|

| Figura 5.21 - Resposta do controlador de tensão ao degrau de carga de 100% para 50% da potência nominal.....   | 90  |

| Figura 5.22 - Corrente de saída para degrau de carga de 100% para 50% da potência nominal.....                 | 91  |

| Figura 5.23 - Resposta do controlador de corrente ao degrau de carga de 100% para 50% da potência nominal..... | 91  |

| Figura 5.24 - Tensões de entrada e de saída durante distúrbio na tensão de entrada. ....                       | 92  |

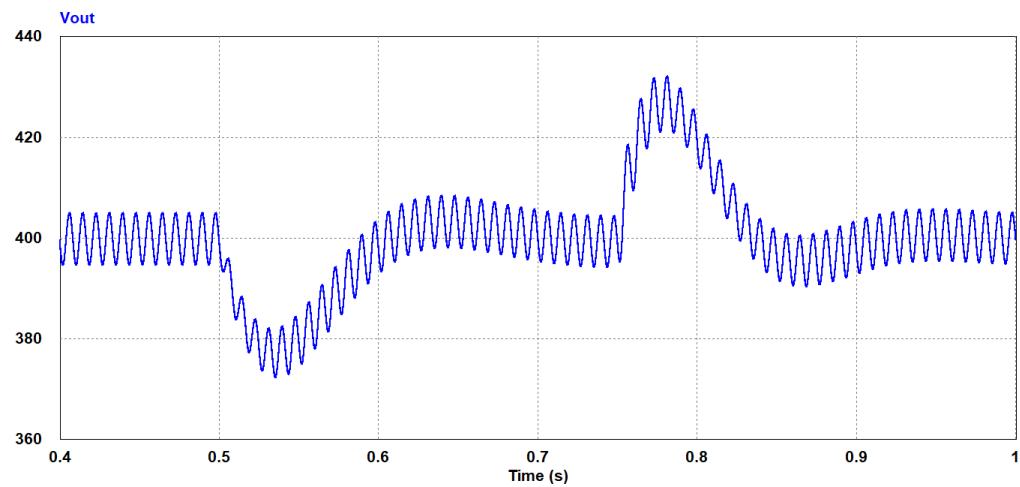

| Figura 5.25 - Detalhe da tensão de saída durante distúrbio na tensão de entrada. ....                          | 92  |

| Figura 5.26 - Resposta do controlador de tensão ao distúrbio na tensão de entrada. ....                        | 93  |

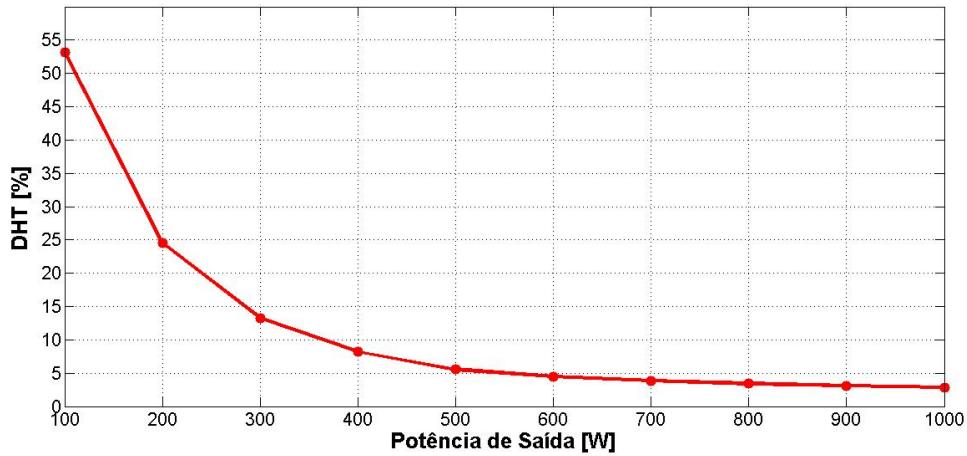

| Figura 5.27 – Distorção harmônica de corrente para diferentes condições de carregamento. ....                  | 94  |

| Figura 5.28 - Fator de Potência para diferentes condições de carregamento. ....                                | 94  |

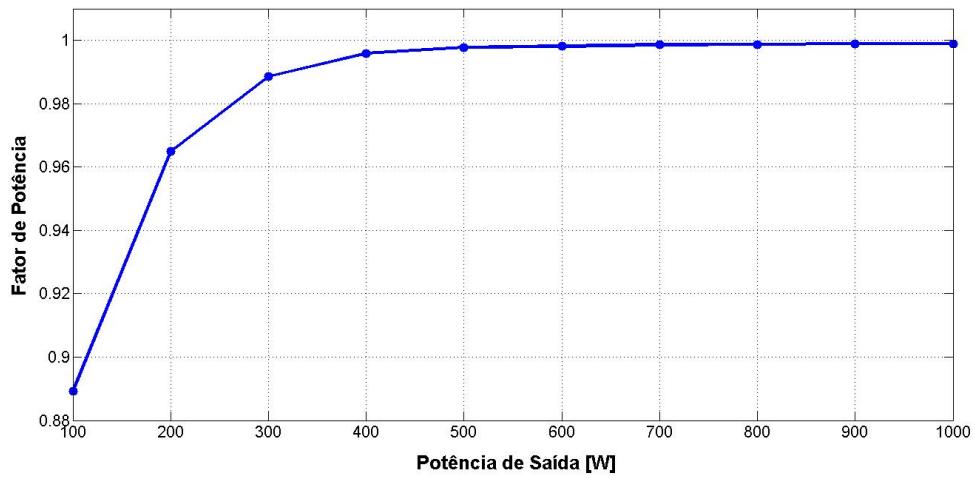

| Figura 5.29 - Perdas nos semicondutores do circuito analisado.....                                             | 95  |

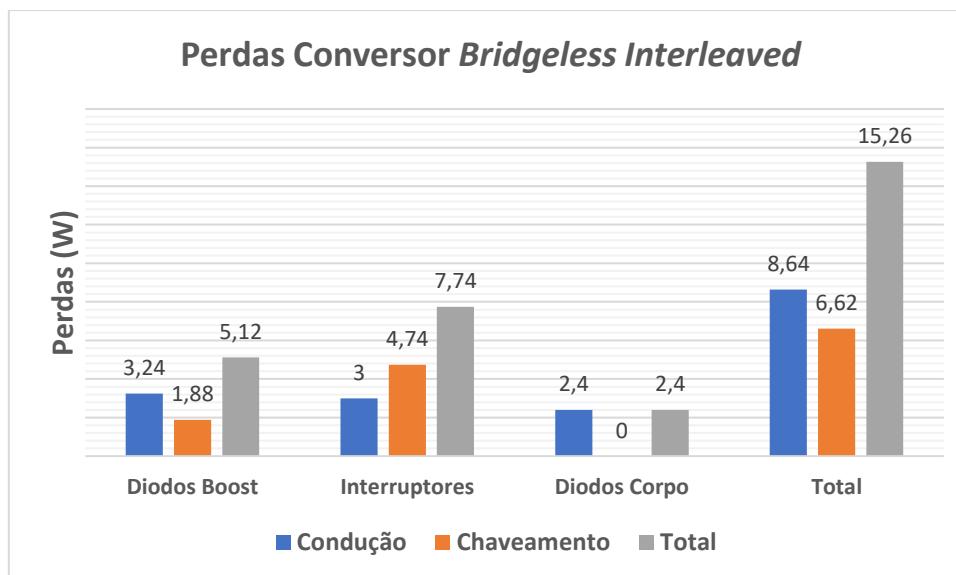

| Figura 5.30 - Perdas nos semicondutores para diferentes topologias <i>boost</i> . ....                         | 96  |

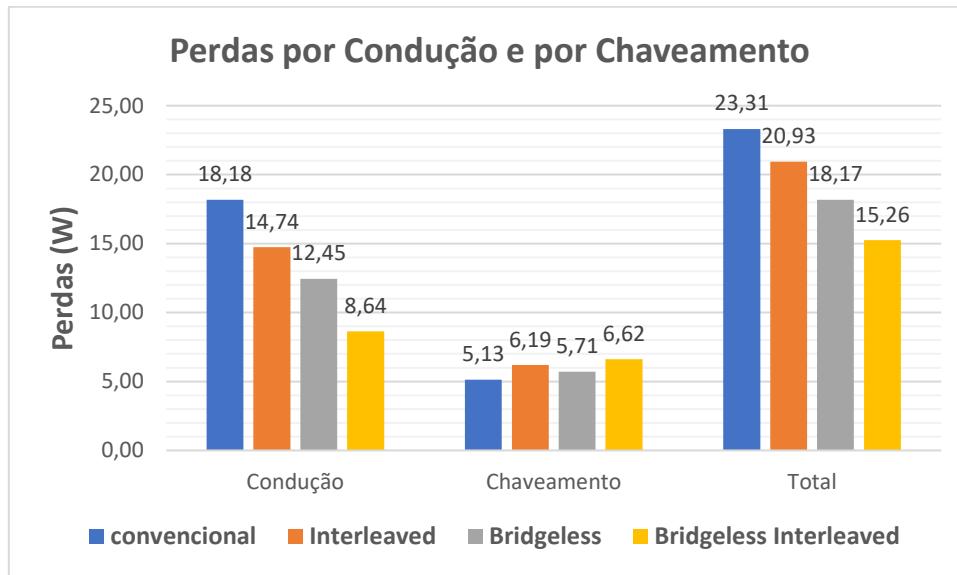

| Figura 5.31 - Perdas por condução e por chaveamento.....                                                       | 97  |

| <br>                                                                                                           |     |

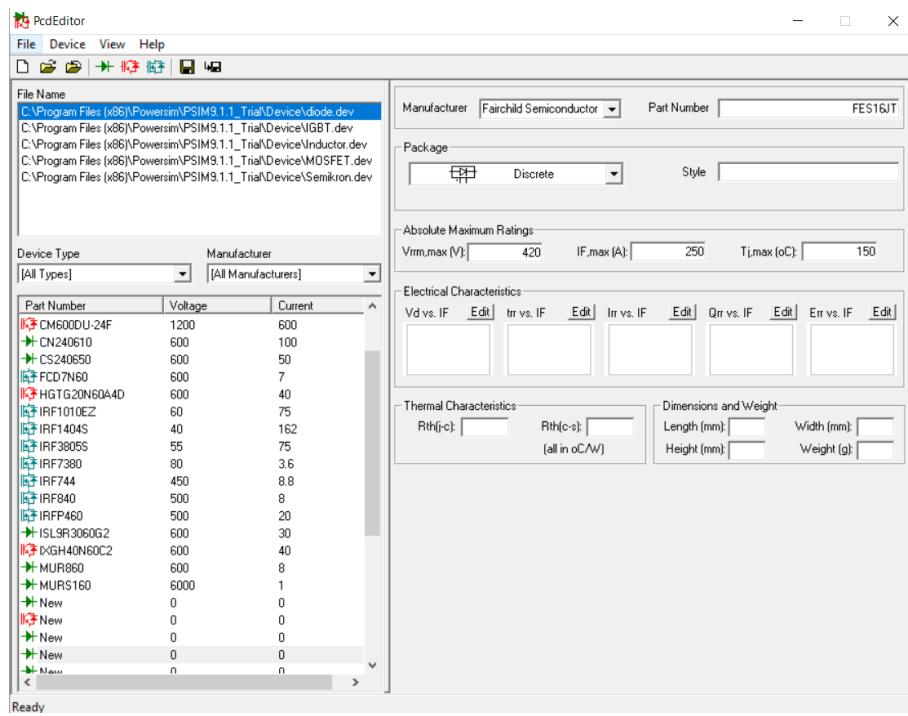

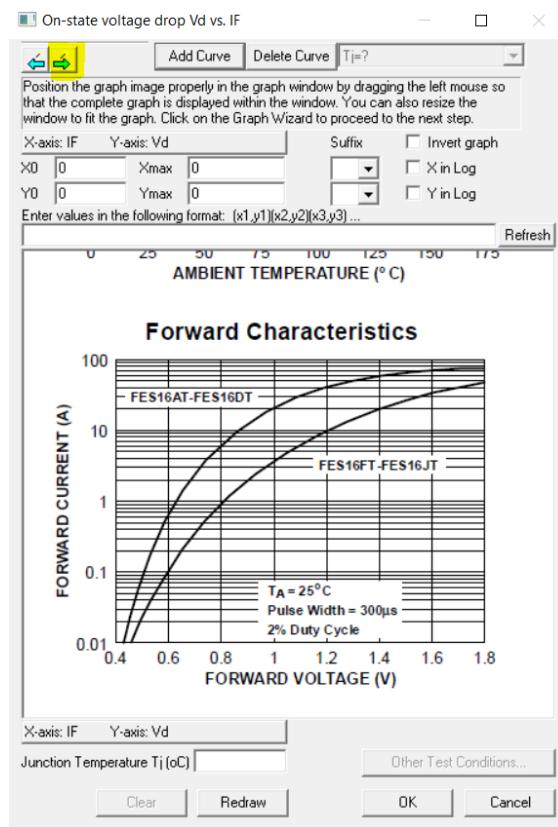

| Figura B 1 - Janela inicial da função <i>Device Database Editor</i> . ....                                     | 111 |

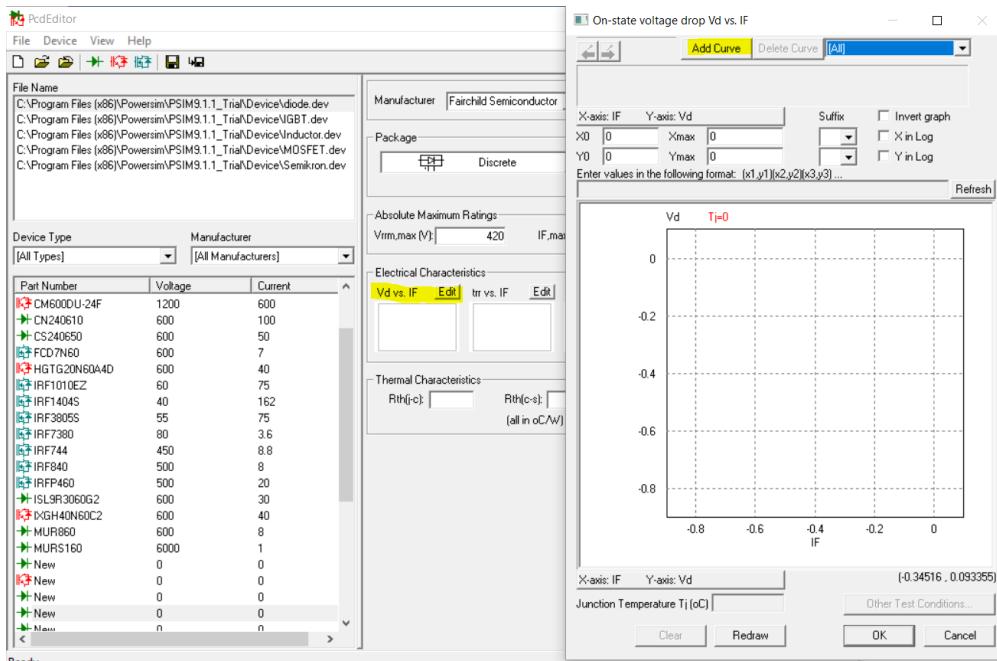

| Figura B 2 - Janela para inserir curvas características do componente. ....                                    | 113 |

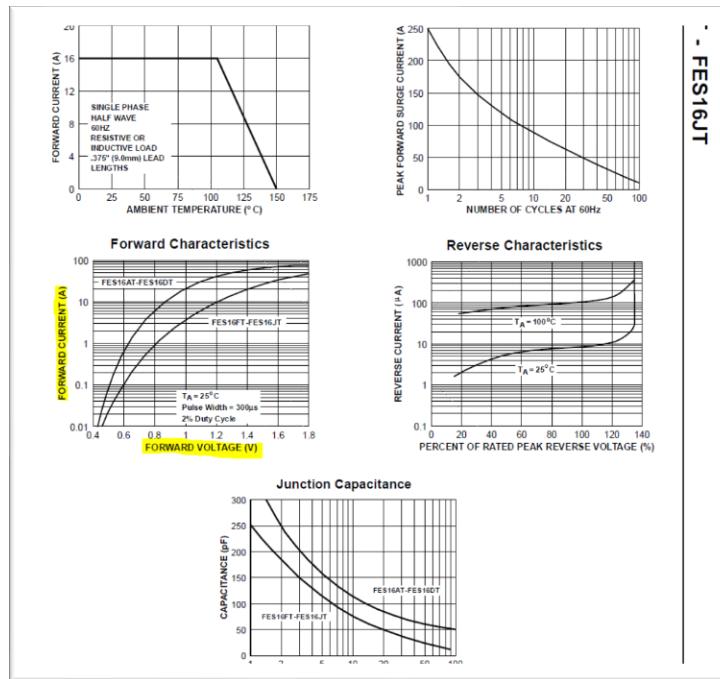

| Figura B 3 - curva que se deseja adicionar retirada do datasheet do componente. ....                           | 113 |

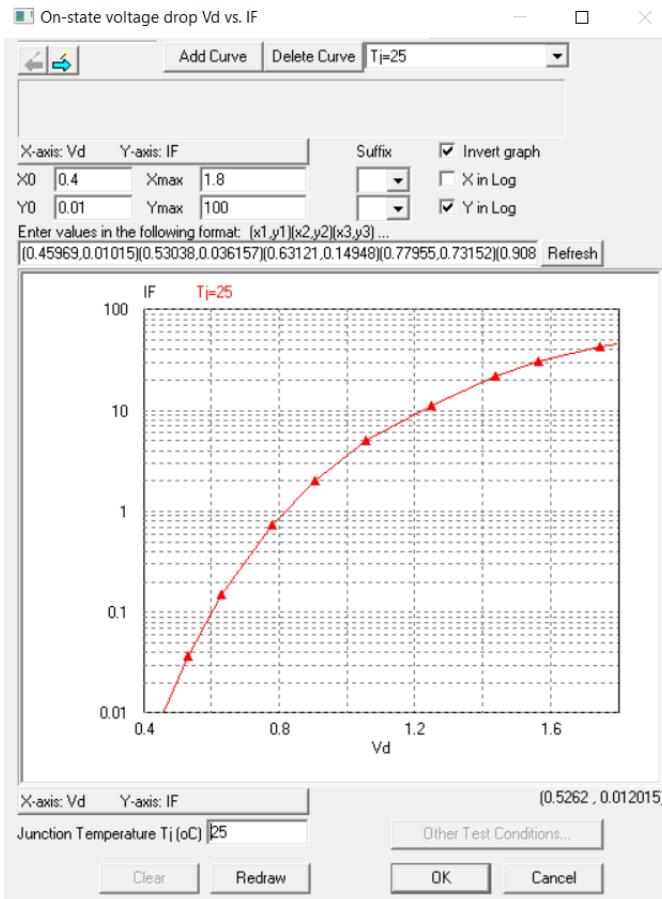

| Figura B 4 - curva adicionada à janela de curvas do editor de componentes. ....                                | 114 |

| Figura B 5 - parâmetros referentes aos eixos X e Y da curva que será adicionada. ....                          | 114 |

| Figura B 6 - curva após ser adicionada ao editor. ....                                                         | 115 |

| Figura B 7 - Circuito com componentes da biblioteca <i>Thermal Module</i> . ....                               | 116 |

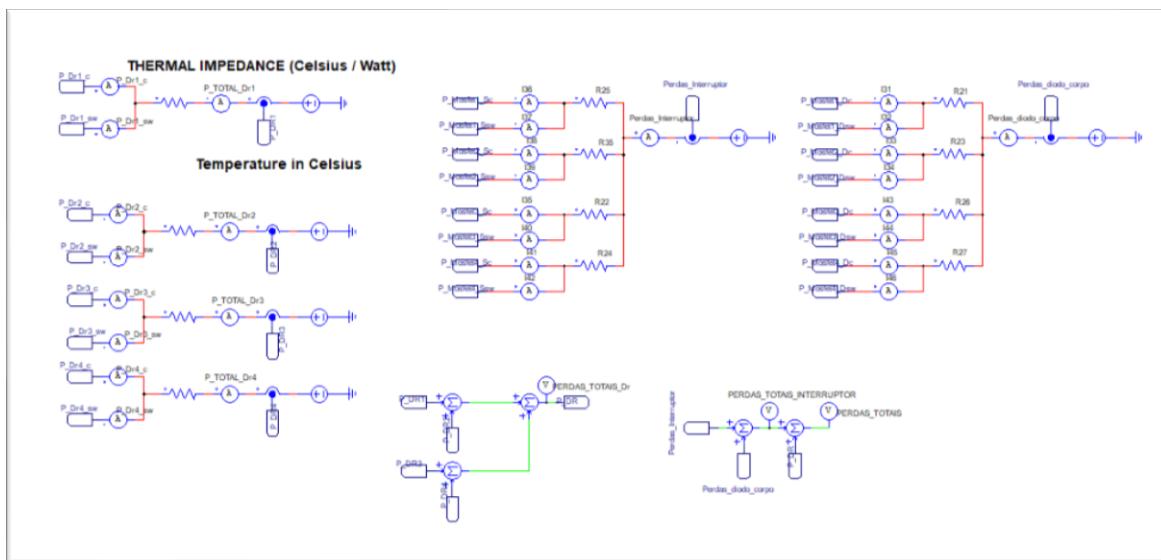

| Figura B 8 - Circuito de medição das perdas nos componentes. ....                                              | 116 |

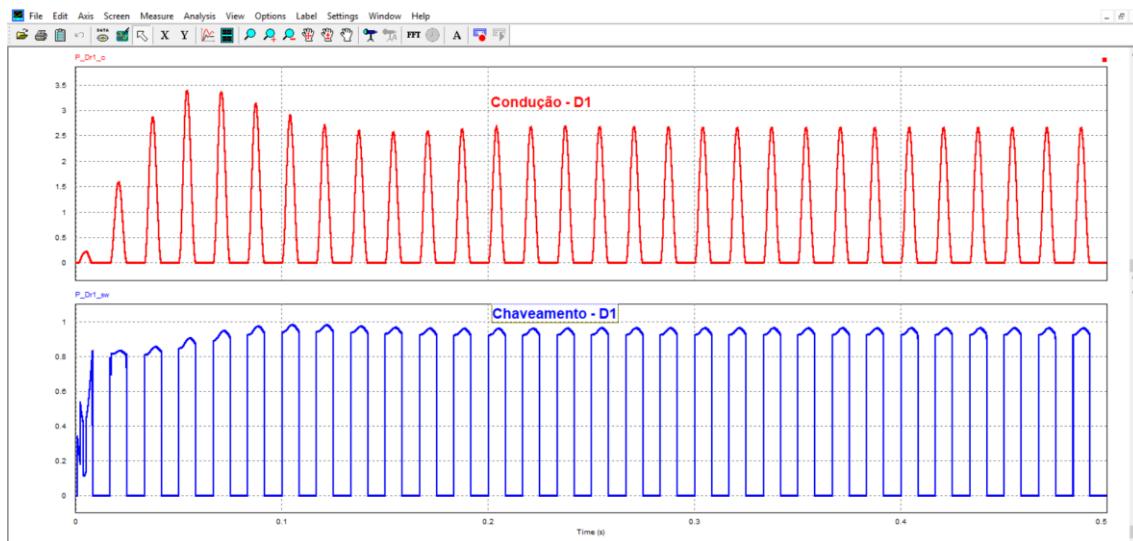

| Figura B 9 - Perdas por condução e por chaveamento no diodo D1. ....                                           | 117 |

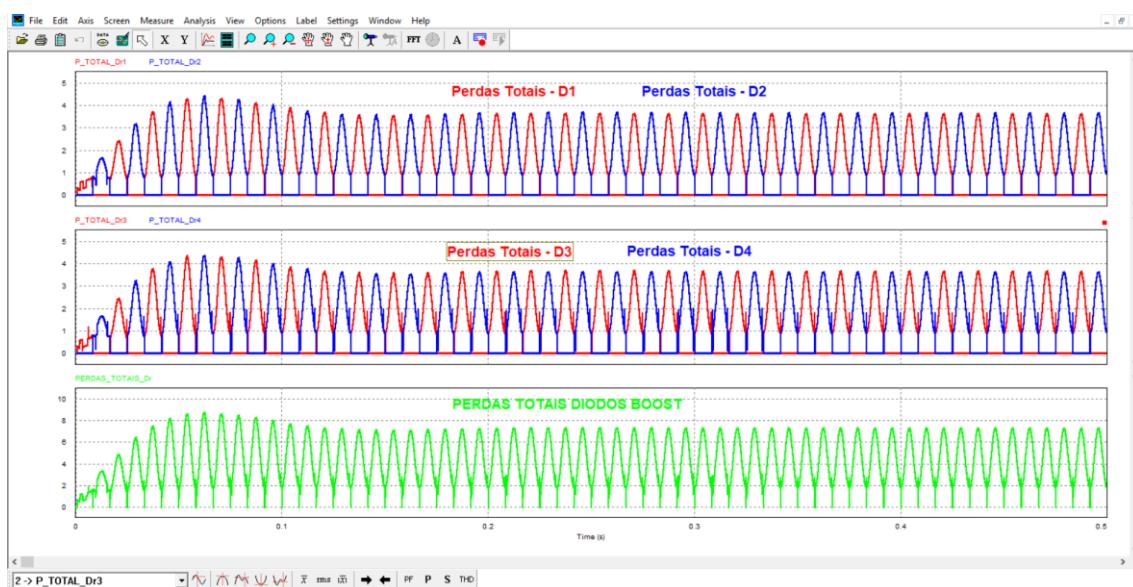

| Figura B 10 - Perdas totais em cada diodo e no conjunto de diodos boost. ....                                  | 117 |

## **LISTA DE TABELAS**

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| Tabela 1 – Valores dos componentes do estágio de potência.....                                 | 53 |

| Tabela 2 - Estados de condução e tempo de duração dos intervalos de operação (D>0,5).<br>..... | 57 |

| Tabela 3 - Parâmetros nominais de projeto. ....                                                | 76 |

## LISTA DE ABREVIATURAS E SÍMBOLOS

|                  |                                                                                 |

|------------------|---------------------------------------------------------------------------------|

| $\Delta i_{L1}$  | <i>Ripple</i> da corrente no indutor 1                                          |

| $\Delta i_{L3}$  | <i>Ripple</i> da corrente no indutor 3                                          |

| $\Delta V_C$     | <i>Ripple</i> de tensão sobre o capacitor                                       |

| $\Delta I_{in}$  | <i>Ripple</i> da corrente de entrada                                            |

| AC               | <i>Alternating current</i>                                                      |

| ANSI             | <i>American National Standards Institute</i>                                    |

| C                | Capacitor de saída                                                              |

| CA               | Corrente alternada                                                              |

| CC               | Corrente contínua                                                               |

| CCM              | <i>Continuous Conduction Mode</i>                                               |

| $C_i$            | Controlador de corrente                                                         |

| $C_v$            | Controlador de tensão                                                           |

| D                | Razão cíclica                                                                   |

| $D_1$            | Díodo 1                                                                         |

| $D_2$            | Díodo 2                                                                         |

| $D_3$            | Díodo 3                                                                         |

| $D_4$            | Díodo 4                                                                         |

| DC               | <i>Direct current</i>                                                           |

| DHI              | Distorção harmônica de corrente                                                 |

| DSP              | <i>Digital Signal Processor</i>                                                 |

| FP               | Fator de potência                                                               |

| $f_s$            | Frequência de chaveamento dos semicondutores                                    |

| $\hat{G}_{id}$   | Função de transferência que relaciona a corrente com a razão cíclica            |

| $\hat{G}_{vd}$   | Função de transferência que relaciona a tensão de saída com a razão cíclica     |

| $\hat{G}_{ivin}$ | Função de transferência que relaciona a corrente com a tensão de entrada        |

| $\hat{G}_{vi}$   | Função de transferência que relaciona a tensão de saída com a corrente          |

| $\hat{G}_{vvin}$ | Função de transferência que relaciona a tensão de saída com a tensão de entrada |

| $i_C$            | Corrente instantânea no capacitor                                               |

| IEC              | <i>International Electrotechnical Commission</i>                                |

| IEEE             | <i>Institute of Electrical and Electronics Engineers</i>                        |

|           |                                          |

|-----------|------------------------------------------|

| IEM       | Interferência Eletromagnética            |

| $i_i$     | Corrente de entrada instantânea          |

| $i_{L12}$ | Corrente que percorre os indutores 1 e 2 |

| $i_{L34}$ | Corrente que percorre os indutores 3 e 4 |

| $I_p$     | Corrente de pico de entrada              |

| $L_1$     | Indutor 1                                |

| $L_2$     | Indutor 2                                |

| $L_3$     | Indutor 3                                |

| $L_4$     | Indutor 4                                |

| MCC       | Modo de condução contínua                |

| MCCr      | Modo de condução crítica                 |

| MCD       | Modo de condução descontínua             |

| N         | Número de células entrelaçadas           |

| PFP       | <i>Power Factor Pre-Regulator</i>        |

| $p_i$     | Potência instantânea                     |

| $P_o$     | Potência de saída                        |

| PLL       | <i>Phase Locked Loop</i>                 |

| PWM       | <i>Pulse width modulation</i>            |

| R         | Resistência de carga                     |

| $S_1$     | Interruptor 1                            |

| $S_2$     | Interruptor 2                            |

| $S_3$     | Interruptor 3                            |

| $S_4$     | Interruptor 4                            |

| $T_s$     | Período de chaveamento                   |

| $v_C$     | Tensão instantânea sobre o capacitor     |

| $v_i$     | Tensão da rede instantânea               |

| $V_{in}$  | Tensão de entrada                        |

| $v_{L1}$  | Tensão sobre o indutor 1                 |

| $v_{L2}$  | Tensão sobre o indutor 2                 |

| $v_{L3}$  | Tensão sobre o indutor 3                 |

| $v_{L4}$  | Tensão sobre o indutor 4                 |

| $V_o$     | Tensão de saída                          |

| $V_p$     | Tensão de pico da rede                   |

|     |                            |

|-----|----------------------------|

| w   | Frequência angular da rede |

| ZCS | Zero current switching     |

| ZVS | Zero voltage switching     |

## SUMÁRIO

|           |                                                                                                                                                 |           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <b>1.</b> | <b>INTRODUÇÃO GERAL.....</b>                                                                                                                    | <b>19</b> |

| 1.1.      | CONSIDERAÇÕES INICIAIS .....                                                                                                                    | 19        |

| 1.2.      | ESTRUTURA DA DISSERTAÇÃO .....                                                                                                                  | 19        |

| <b>2.</b> | <b>ESTADO DA ARTE .....</b>                                                                                                                     | <b>21</b> |

| 2.1.      | CONSIDERAÇÕES INICIAIS .....                                                                                                                    | 21        |

| 2.2.      | MODOS DE CONDUÇÃO DE CORRENTE.....                                                                                                              | 23        |

| 2.3.      | TÉCNICA DE ENTRELAÇAMENTO.....                                                                                                                  | 24        |

| 2.4.      | TOPOLOGIAS DE CONVERSORES PFP <i>BRIDGELESS Boost</i> .....                                                                                     | 26        |

| 2.4.1.    | <i>Conversor PFP Bridgeless Dual Boost</i> .....                                                                                                | 26        |

| 2.4.2.    | <i>Conversor PFP Bridgeless Boost com chaves bidirecionais</i> .....                                                                            | 27        |

| 2.4.3.    | <i>Conversor PFP Bridgeless Two-Boost</i> .....                                                                                                 | 28        |

| 2.4.4.    | <i>Conversor FPF Bridgeless Totem-Pole e Pseudo Totem-Pole</i> .....                                                                            | 29        |

| 2.4.5.    | <i>Análise de perdas por condução entre as topologias Bridgeless</i> .....                                                                      | 30        |

| 2.5.      | MÉTODOS DE CONTROLE POR CORRENTE .....                                                                                                          | 30        |

| 2.5.1.    | <i>Controle por Corrente de Pico</i> .....                                                                                                      | 31        |

| 2.5.2.    | <i>Controle por Corrente Média</i> .....                                                                                                        | 32        |

| 2.5.3.    | <i>Controle da corrente por histerese</i> .....                                                                                                 | 33        |

| 2.5.4.    | <i>Controle por portadora programada</i> .....                                                                                                  | 34        |

| 2.6.      | CONSIDERAÇÕES FINAIS.....                                                                                                                       | 35        |

| <b>3.</b> | <b>CONVERSOR CA-CC BOOST ENTRELAÇADO SEM PONTE DE DIODOS OPERANDO EM MCC .....</b>                                                              | <b>37</b> |

| 3.1.      | CONSIDERAÇÕES INICIAIS .....                                                                                                                    | 37        |

| 3.2.      | ETAPAS DE OPERAÇÃO DO CONVERSOR .....                                                                                                           | 38        |

| 3.2.1.    | <i>Análise para <math>D &gt; 0,5</math></i> .....                                                                                               | 39        |

| 3.2.2.    | <i>Análise para <math>D &lt; 0,5</math></i> .....                                                                                               | 44        |

| 3.3.      | DIMENSIONAMENTO E PROJETO DO CIRCUITO DE POTÊNCIA .....                                                                                         | 48        |

| 3.3.1.    | <i>Indutores Boost</i> .....                                                                                                                    | 48        |

| 3.3.2.    | <i>Capacitor</i> .....                                                                                                                          | 51        |

| 3.4.      | CONSIDERAÇÕES FINAIS.....                                                                                                                       | 53        |

| <b>4.</b> | <b>MODELAGEM E ESTRATÉGIA DE CONTROLE DO CONVERSOR OPERANDO EM MCC .....</b>                                                                    | <b>55</b> |

| 4.1.      | CONSIDERAÇÕES INICIAIS .....                                                                                                                    | 55        |

| 4.2.      | MODELO MÉDIO LINEARIZADO EM ESPAÇO DE ESTADOS.....                                                                                              | 55        |

| 4.2.1.    | <i>Circuitos equivalentes para o intervalo 1 (<math>S1</math> e <math>S2</math> fechados e <math>S3</math> e <math>S4</math> abertos)</i> ..... | 57        |

| 4.2.2.    | <i>Círculo equivalente para o intervalo 2 e 4 (<math>S1</math>, <math>S2</math>, <math>S3</math> e <math>S4</math> fechados)</i> .....          | 59        |

|                                                                                           |                                                                                                                      |            |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| 4.2.3.                                                                                    | <i>Círculo equivalente para o intervalo 3 (<b>S1</b> e <b>S2</b> abertos e <b>S3</b> e <b>S4</b> fechados) .....</i> | 60         |

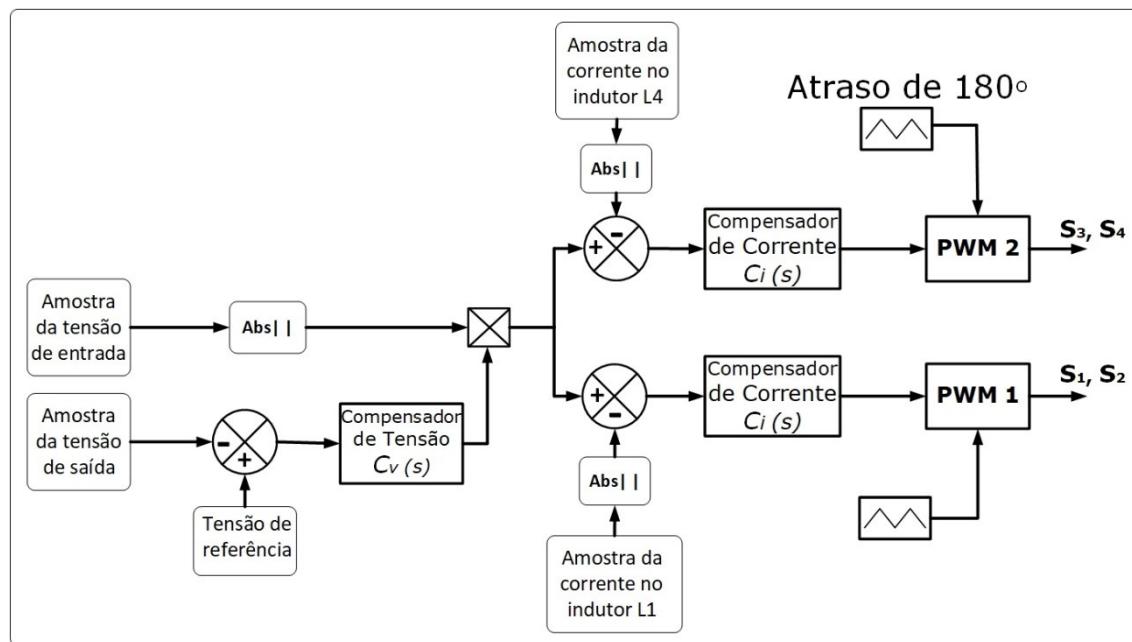

| 4.3.                                                                                      | ESTRATÉGIA DE CONTROLE .....                                                                                         | 70         |

| 4.4.                                                                                      | PROJETO DO ESTÁGIO DE CONTROLE .....                                                                                 | 71         |

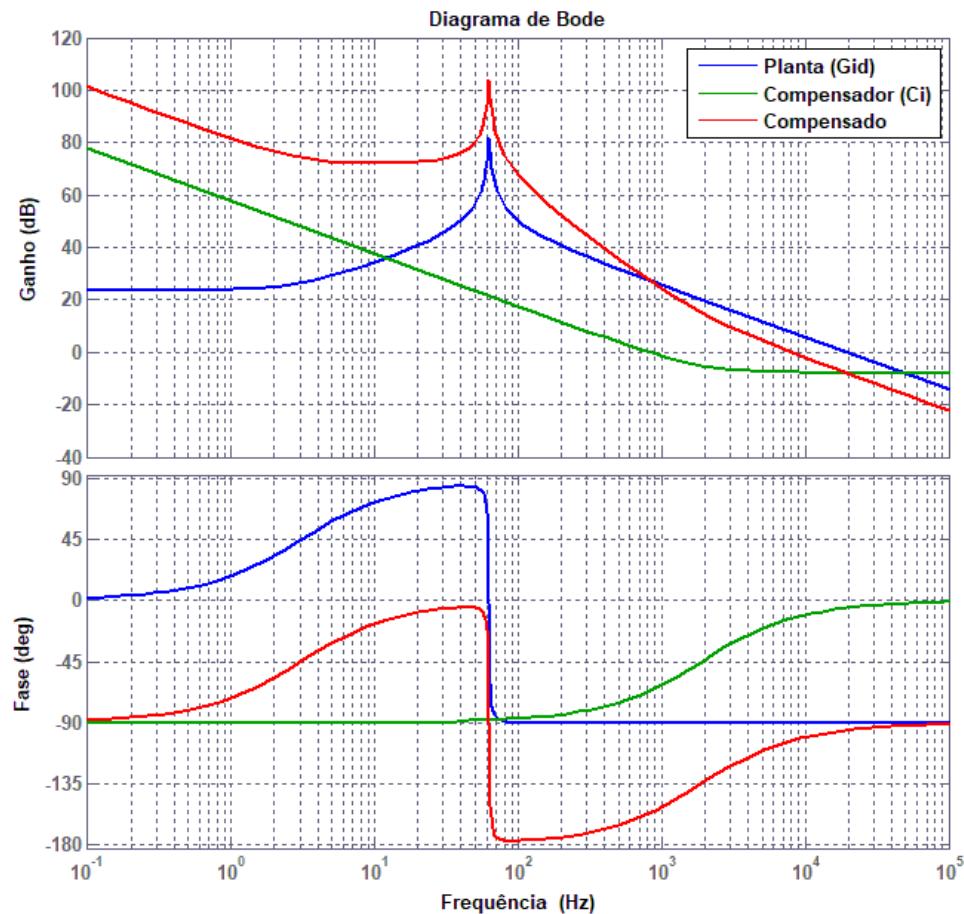

| 4.4.1.                                                                                    | <i>Projeto do controlador de corrente .....</i>                                                                      | 71         |

| 4.4.2.                                                                                    | <i>Projeto do controlador de tensão .....</i>                                                                        | 73         |

| 4.5.                                                                                      | CONSIDERAÇÕES FINAIS.....                                                                                            | 75         |

| <b>5.</b>                                                                                 | <b>RESULTADOS COMPUTACIONAIS .....</b>                                                                               | <b>76</b>  |

| 5.1.                                                                                      | CONSIDERAÇÕES INICIAIS .....                                                                                         | 76         |

| 5.2.                                                                                      | PARÂMETROS NOMINAIS DO PROJETO.....                                                                                  | 76         |

| 5.3.                                                                                      | RESULTADOS DE SIMULAÇÃO COMPUTACIONAL.....                                                                           | 77         |

| 5.3.1.                                                                                    | <i>Modulação por largura de pulso (PWM) .....</i>                                                                    | 78         |

| 5.3.2.                                                                                    | <i>Pré carga do capacitor e entrada de carga no sistema .....</i>                                                    | 80         |

| 5.3.3.                                                                                    | <i>Tensão de saída na carga .....</i>                                                                                | 82         |

| 5.3.4.                                                                                    | <i>Corrente de entrada .....</i>                                                                                     | 83         |

| 5.3.5.                                                                                    | <i>Corrente e tensão nos diodos e interruptores.....</i>                                                             | 85         |

| 5.3.6.                                                                                    | <i>Transitório de Carga e Distúrbio na Tensão de Alimentação .....</i>                                               | 86         |

| 5.3.7.                                                                                    | <i>Qualidade da corrente em diferentes condições de carregamento.....</i>                                            | 93         |

| 5.3.8.                                                                                    | <i>Perdas nos semicondutores .....</i>                                                                               | 94         |

| 5.4.                                                                                      | CONSIDERAÇÕES FINAIS.....                                                                                            | 97         |

| <b>6.</b>                                                                                 | <b>CONCLUSÕES GERAIS .....</b>                                                                                       | <b>98</b>  |

| <b>REFERÊNCIAS .....</b>                                                                  |                                                                                                                      | <b>101</b> |

| <b>APÊNDICE A – CÓDIGO DE CONTROLE DIGITAL UTILIZADO NA SIMULAÇÃO (LINGUAGEM C) .....</b> |                                                                                                                      | <b>105</b> |

| <b>APÊNDICE B – BIBLIOTECA “THERMAL MODULE” E FUNÇÃO “DEVICE DATABASE EDITOR” .....</b>   |                                                                                                                      | <b>110</b> |

| <b>APÊNDICE C – CÓDIGO DE CÁLCULO DA DISTORÇÃO HARMÔNICA DE CORRENTE .....</b>            |                                                                                                                      | <b>118</b> |

## 1. INTRODUÇÃO GERAL

### 1.1. Considerações Iniciais

Este trabalho tem como objetivo principal realizar a análise de um conversor CA-CC de elevado fator de potência, que utilize a técnica de entrelaçamento multicelular e que realize o estágio de retificação sem a necessidade de uma ponte retificadora de diodos. O referido conversor deve fornecer uma tensão de saída CC controlada e permitir a obtenção de uma corrente de entrada em fase com a tensão da rede e com baixo conteúdo harmônico.

O trabalho tem ainda o propósito de apresentar, detalhadamente, o processo de modelagem em espaço de estados do conversor operando em modo de condução contínua com modulação PWM.

Dentre os pontos de contribuição deste trabalho, pode-se destacar:

- Desenvolvimento detalhado da modelagem em espaço de estados de um conversor *bridgeless boost*, que emprega a técnica de entrelaçamento multicelular e opera em modo de condução contínua (MCC) com modulação PWM;

- Projeto de circuito de controle por corrente média capaz de regular a tensão de saída CC e ajustar a corrente de entrada, melhorando o fator de potência e diminuindo as componentes harmônicas, de modo a obedecer aos padrões impostos pela norma IEC 61000-3-2;

- Desenvolvimento de código de controle digital pronto a ser embarcado em uma estrutura DSP;

- Análise de perdas nos semicondutores para diferentes topologias de conversores *boost*.

### 1.2. Estrutura da Dissertação

Este documento está dividido em seis (6) capítulos incluindo este introdutório, que resume os objetivos gerais do trabalho e apresenta a estrutura da dissertação.

No capítulo 2 será apresentado o estado da arte do tema abordado, mostrando os principais conceitos envolvidos na pesquisa, os métodos de controle mais utilizados, e as topologias mais comumente empregadas como conversores CA-CC com correção ativa do fator de potência.

No capítulo 3 será apresentada a estrutura da topologia analisada no trabalho, bem como o princípio de funcionamento e a análise das etapas de operação do circuito. São desenvolvidas as equações de tensão e corrente nos elementos armazenadores de energia, as quais serão utilizadas no dimensionamento do circuito de potência.

O capítulo 4 abordará sobre a modelagem matemática do conversor utilizando o modelo médio linearizado em espaço de estados. É apresentado o desenvolvimento detalhado das etapas para obtenção das matrizes características do sistema, as quais são utilizadas para representação das funções de transferência e posterior projeto do circuito de controle. Além disso, é apresentada a estratégia de controle utilizada para correção da corrente de entrada e ajuste da tensão de saída CC.

O capítulo 5 trata-se do projeto do circuito de potência e do circuito de controle do sistema. Também são apresentadas as simulações e os resultados obtidos mediante diferentes condições de carga e distúrbios na rede. Além disso, é apresentado um estudo de perdas nos semicondutores do circuito analisado, bem como uma comparação das perdas nos semicondutores apresentadas por diferentes topologias *boost*, as quais foram obtidas através do *software* PSIM.

Já o capítulo 6 mostrará as conclusões gerais do trabalho, assim como propostas de continuação da pesquisa. Por fim, seguem-se as referências bibliográficas utilizadas ao longo do trabalho e os apêndices que complementam a leitura do texto.

## 2. ESTADO DA ARTE

### 2.1. Considerações Iniciais

A aplicação de conversores CA-CC modulados por largura de pulso (PWM) tem sido amplamente difundida na utilização de fontes de alimentação para uma variedade de sistemas eletrônicos, tais como sistemas de transmissão de corrente contínua, sistemas para utilização de energia solar, acionamento elétrico de motores de propulsão de veículos, sistemas de carga de baterias, dentre outros (SILVA, 2011).

O fato de existirem diversas normas e recomendações que impõem limites para a emissão de correntes harmônicas nos sistemas, tais como IEC, *International Electrotechnical Commission Standard 61000-3-2*, 61000-3-4 e IEEE/ANSI Standard 519, justifica as diversas pesquisas relacionadas a sistemas com correção ativa do fator de potência. Em geral, sistemas retificadores com correção do fator de potência têm como objetivo a redução das distorções harmônicas da corrente de entrada drenada do sistema CA e a regulação da tensão de saída no lado CC.

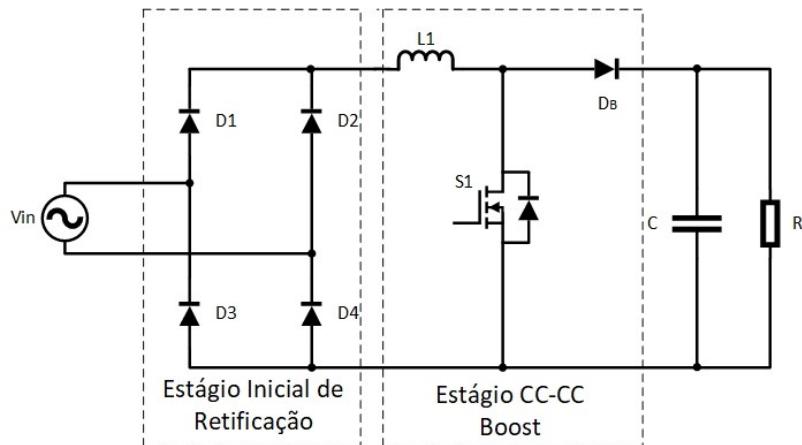

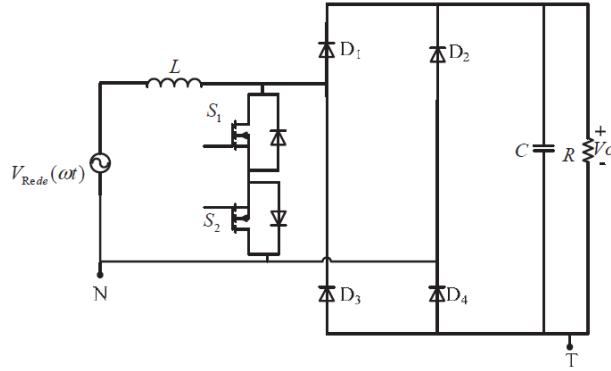

Uma das topologias mais empregadas na correção ativa do fator de potência é o conversor pré-regulador do fator de potência *boost* clássico, ilustrado na Figura 2.1. Contudo, existem outras topologias de retificadores *boost* que também são empregadas como pré-reguladores com correção ativa do fator de potência. Dentre as mais utilizadas encontram-se a topologia *boost* entrelaçado e a topologia *boost bridgeless*, que não utiliza a ponte de diodos no estágio retificador (BELTRAME; SARTORI; PINHEIRO, 2015). Vale ressaltar que a principal limitação dessas topologias *boost* é a necessidade de a tensão de saída CC ser maior que o valor de pico da tensão alternada de entrada, o que torna seu uso limitado para aplicações com características de elevação de tensão (CANESIN; GONCALVES, 2005) (IRVING; JANG; JOVANOVIC, 2000).

Figura 2.1 - Conversor PFP Boost Clássico.

A topologia do conversor PFP *boost* clássico apresenta dois estágios distintos: o estágio inicial de retificação, que é realizado pela ponte de diodos na entrada circuito, e o estágio de alta frequência composto pelo conversor *boost*, responsável pela regulação da tensão CC de saída e da correção da forma de onda da corrente drenada da rede através do chaveamento em alta frequência.

No estágio inicial de retificação, a ponte de diodos é responsável por converter a tensão alternada da rede em tensão contínua, conforme dada por (2.1). Assim, a tensão que irá alimentar o estágio conversor será uma senoide retificada, com valor de pico igual ao da tensão de entrada. Uma característica importante em estruturas com a ponte completa de diodos é que ela não permite um fluxo bidirecional de corrente, ou seja, não é possível realizar transferência de energia de qualquer parte do circuito em direção à fonte de alimentação de entrada.

$$v_g(t) = |v_{in}(t)| \quad (2.1)$$

Já o estágio conversor, composto pelo conversor *boost* CC-CC operando em alta frequência, é responsável por realizar o controle da tensão senoidal retificada, transformando-a em uma tensão contínua de valor preestabelecido e mantendo-a com o mínimo de variações possíveis. O conversor *boost* controlado por corrente com modulação PWM é capaz de moldar o formato da corrente drenada da rede, deixando-a com o mesmo formato e em fase com a tensão da rede, o que proporciona um elevado fator de potência ao sistema.

Conforme será abordado no decorrer do capítulo, o conversor *boost* poderá atuar em diferentes modos de operação em relação à corrente que passa pelo indutor, possuindo cada modo suas respectivas vantagens e desvantagens para diferentes tipos de aplicação. Além disso, o controle por corrente pode ser realizado por diversas técnicas. A escolha adequada da técnica e o correto projeto das malhas interna e externa de controle, permitem a obtenção tanto de uma tensão de saída constante, quanto uma corrente de entrada proporcional à tensão da rede.

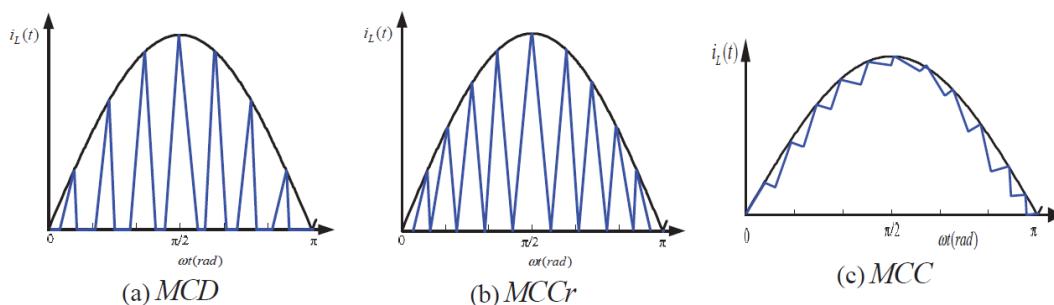

## 2.2.Modos de Condução de Corrente

Os retificadores *boost* podem operar de três formas distintas: modo de condução contínua (MCC), modo de condução descontínua (MCD) ou modo de condução crítica (MCCr), que ocorre na fronteira entre os modos MCC e MCD. Essa classificação quanto ao modo de condução ocorre de acordo com a continuidade da corrente no indutor do circuito, dentro do ciclo de chaveamento (BASU; UNDELAND, 2005). A Figura 2.2 mostra as formas de onda no indutor de um conversor *boost* para os diferentes modos de condução de corrente.

Figura 2.2 - Formas de onda dos modos de condução de corrente.

Fonte: Costa e Silva (2011).

Topologias *boost* operando em modo de condução descontínua (MCD) ou modo de condução crítica (MCCr) usualmente necessitam de estruturas de controle mais simples. Por outro lado, apresentam maior *ripple* de corrente, levando a maiores perdas magnéticas e por condução, maior ruído no chaveamento e, consequentemente, necessidade de filtros mais robustos. Assim, retificadores *boost* que utilizam esses modos

de condução ficam geralmente restritos a aplicações de baixa potência, enquanto os que operam em modo de condução contínua (MCC) são muito utilizados em aplicações de média e alta potência (MUSAVI; EBERLE; DUNFORD, 2011).

Como a topologia *boost* frequentemente trabalha com elevada tensão de saída, é necessário utilizar diodos que suportem altas tensões e proporcione uma rápida recuperação. Uma das desvantagens da operação em modo de condução contínua (MCC), é o aumento das perdas nos diodos com rápida recuperação reversa quando operando em altas frequências.

Visando mitigar o efeito dessas perdas na eficiência do sistema, é possível empregar as técnicas de comutação suave, como a ZVS (*Zero Voltage Switching*) e a ZCS (*Zero Current Switching*). Estas técnicas empregam circuitos ativos que auxiliam na comutação (*snubbers*) para controlar as derivadas de correntes e/ou tensões durante as comutações (IRVING; JANG; JOVANOVIC, 2000). Diversos estudos mostram as melhorias alcançadas através da utilização dessas técnicas, tal como o trabalho de JOVANOVIC e JANG (2000), que apresenta um *snubber* que emprega um número mínimo de componentes para elevar a eficiência de conversores *boost* através da mitigação das perdas por recuperação reversa.

### 2.3.Técnica de Entrelaçamento

A ideia de entrelaçamento (“*interleaving*”) de células para operação de conversores CC-CC surgiu há muitos anos. De acordo com BALOGH; REDL (1993) uma das primeiras referências à técnica teve origem em 1972. No início, o método foi utilizado com o propósito principal de superar as limitações comuns aos dispositivos e conversores de potência da época (MIWA; OTTEN; SCHLECHT, 1992).

Com o reconhecimento das vantagens da utilização do método de operação em paralelo de células conversoras, diversos estudos foram realizados em sequência, porém ainda não havia uma padronização quanto à terminologia dada à técnica. Dentre as diversas nomenclaturas empregadas, vários autores adotaram o termo “*multiphase conversion*” ou “*staggered phase conversion*”, ambos originários de (GARTH et al., 1971). Contudo, vários outros termos também foram utilizados para fazer referência à técnica, tais como “*interdigitating and polyphase chopping*”, “*interleaving, staggered*

*clock timing*”, “*ripple current cancelation*”, “*phase-shifted parallel*” e “*phaed synchronous conversion*” (MIWA; OTTEN; SCHLECHT, 1992).

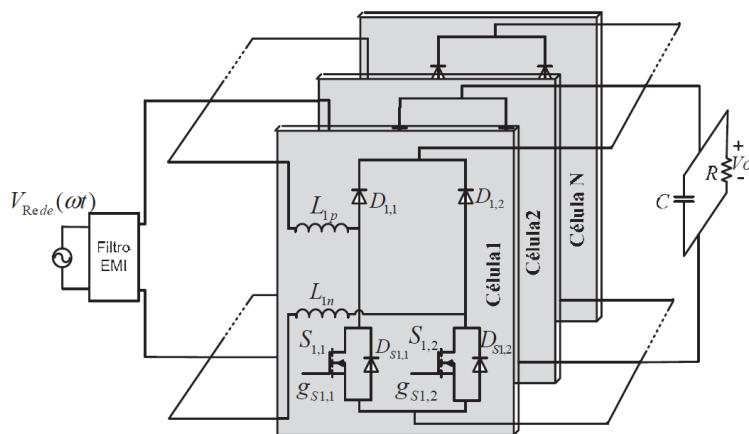

A técnica de entrelaçamento consiste na interconexão de duas ou mais células conversoras operando a uma mesma frequência de chaveamento, porém com pulsos de controle defasados entre si em frações iguais do período de chaveamento. Em uma estrutura com  $N$  células entrelaçadas, conforme ilustrado na Figura 2.3, os sinais de controle estarão defasados entre si de  $T_s/N$ , onde  $T_s$  representa o período de chaveamento.

Figura 2.3 - Técnica de entrelaçamento de células *bridgeless boost*.

Fonte: Costa e Silva (2011).

Esta técnica apresenta como principal objetivo a redução das perdas e melhoria da confiabilidade e estabilidade da estrutura (MELO, 2010). Dentre as diversas vantagens do método têm-se a redução dos esforços de tensão em cada interruptor devido à divisão da tensão de saída entre as estruturas, a redução da amplitude do *ripple* de alta frequência da corrente de entrada, uma vez que o *ripple* das correntes dos indutores estão defasados e tendem a se cancelarem (MUSAVI; EBERLE; DUNFORD, 2011), a redução nas exigências de filtragem e no tamanho dos indutores *boost* e a redução do *ripple* da corrente do capacitor de saída em função da razão cílica (ZHU; PRATT, 2009). Além disso, como apresentado em (WONG; LEE, 2000), a técnica de entrelaçamento também auxilia na redução das perdas por recuperação reversa nos diodos sem a necessidade de chaves auxiliares extras, as quais são usualmente utilizadas em circuitos *snubbers* com esse propósito.

Como pontos negativos desta técnica, pode-se citar uma maior complexidade no sistema de controle e nos circuitos utilizados na geração dos sinais de comando dos interruptores, uma vez que deve-se assegurar uma correta distribuição da corrente entre as células conversoras, além do custo mais elevado em relação às topologias convencionais, devido à necessidade componentes extras (ANDRADE; SCHUCH; PINHEIRO, 2004).

No que se refere ao projeto dos componentes de potência, é possível realizar o cálculo e dimensionamento dos elementos separadamente para cada célula conversora interconectada. A potência total do sistema será dada pela soma das potências nominais individuais de cada célula da estrutura.

## 2.4. Topologias de Conversores PFP *Bridgeless Boost*

As topologias com característica *bridgeless* apresentam como principal vantagem a redução das perdas por condução nos semicondutores de potência, uma vez que integram em um único estágio os processos de retificação e correção do fator de potência, aumentando assim o rendimento total do sistema. Por outro lado, a família *bridgeless* aumenta o tamanho do filtro necessário contra interferências eletromagnéticas (MELO, 2010). Algumas das topologias *bridgeless* são apresentadas a seguir.

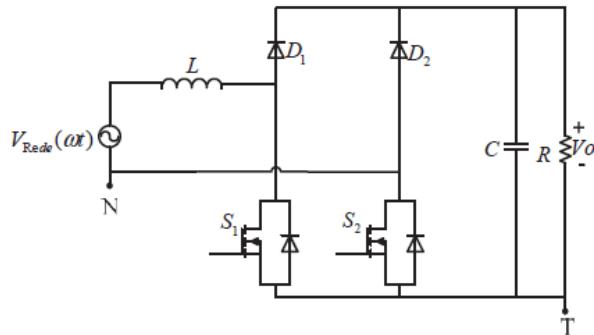

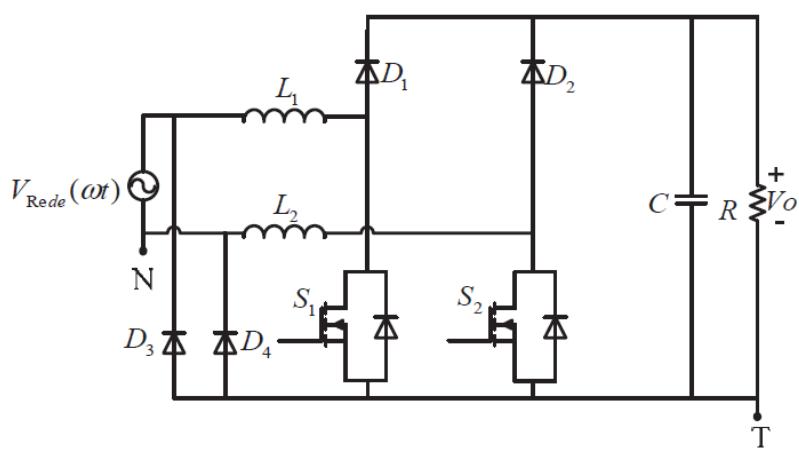

### 2.4.1. Conversor PFP Bridgeless Dual Boost

Esta topologia *bridgeless* proposta em (ENJETI; MARTINEZ, 1993) e ilustrada na Figura 2.4, emprega um duplo *boost* operando em alta frequência e apresenta diversas vantagens em relação à topologia convencional, a saber: a condução de no máximo dois semicondutores em qualquer instante, a redução da corrente eficaz dos interruptores e o referencial comum aos *gate drivers* dos interruptores

Figura 2.4 - Topologia *Bridgeless Dual Boost*.

Fonte: Enjeti (1993).

Por outro lado, a estrutura aumenta consideravelmente a interferência eletromagnética (IEM), especialmente o ruído de modo comum, quando comparada com a topologia tradicional. Nesta última, a ponte retificadora de diodos permite que a referência da carga esteja sempre ligada à referência da linha, enquanto no *dual boost* somente no semicírculo positivo da rede a referência de saída fica ligada à fonte alternada, através do diodo em antiparalelo do interruptor  $S_2$ . No semicírculo negativo da rede, a diferença de potencial entre a referência de saída e o ponto comum da fonte pulsa com a frequência de chaveamento (SILVA, 2011).

#### 2.4.2. Conversor PFP *Bridgeless Boost* com chaves bidirecionais

A topologia proposta em (KONG; WANG; LEE, 2008) e ilustrada na Figura 2.5, utiliza uma chave bidirecional em corrente, formada pela associação em série de dois MOSFETs. Durante cada semicírculo da rede quatro semicondutores conduzem, contudo apenas dois de maneira simultânea, reduzindo as perdas por condução quando comparado ao *boost* convencional. Um ponto negativo da topologia é que, devido à característica pulsante do potencial entre a referência da fonte e a referência da carga, a emissão do ruído de modo comum é elevada.

Durante o semicírculo positivo da rede, a corrente flui através do interruptor  $S_1$  e do diodo de corpo de  $S_2$ , ou então pelos diodos  $D_1$  e  $D_4$ , dependendo do sinal de controle. Já no semicírculo negativo, a corrente passa por  $S_2$  e pelo diodo de corpo de  $S_1$ , ou pelos diodos  $D_2$  e  $D_3$ .

Figura 2.5 - Topologia Bridgeless Boost com chaves bidirecionais.

Fonte: Kong (2008).

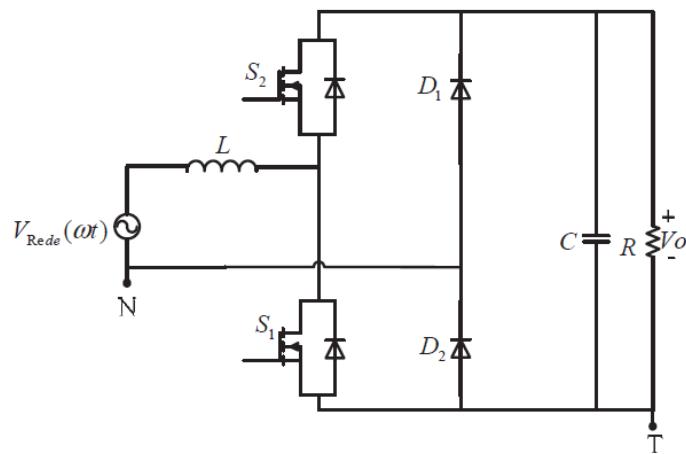

#### 2.4.3. Conversor PFP Bridgeless Two-Boost

No conversor PFP *Bridgeless Two-Boost*, ilustrado na Figura 2.6, dois diodos de baixa frequência são adicionados à topologia *bridgeless* visando criar um caminho para circulação da corrente entre a e entrada e a saída, auxiliando na estabilização do potencial de tensão no barramento de saída. Essa configuração reduz as interferências eletromagnéticas por ruído de modo comum e ainda mantém a baixa perda por condução, comum à família *bridgeless* (SILVA, 2011)

•

Figura 2.6 - Topologia Bridgeless Two-Boost.

Fonte: Souza (1999).

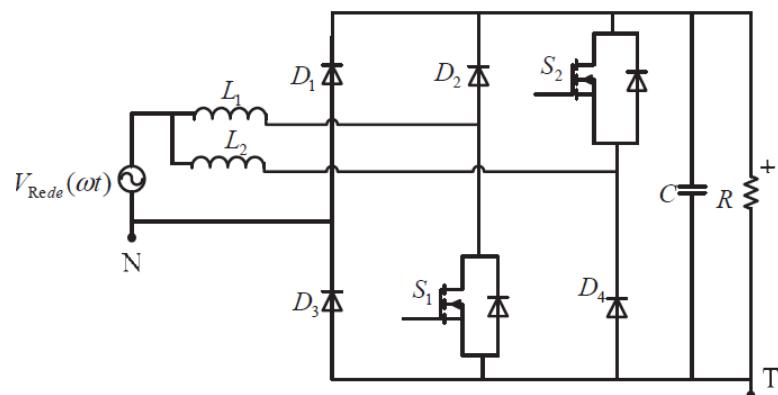

#### 2.4.4. Conversor FPF Bridgeless Totem-Pole e Pseudo Totem-Pole

A topologia *Totem-Pole*, ilustrado na Figura 2.7, possui os mesmos componentes presentes na topologia *Dual Boost* arranjados de maneira diferente. Essa configuração permite que a diferença de potencial entre a referência da fonte e a da carga seja nula no semiciclo positivo e se mantenha estabilizada no semiciclo negativo, com o mesmo valor da tensão de saída.

Já a Figura 2.8 apresenta a topologia *Pseudo Totem-Pole*, na qual são adicionados dois diodos lentos e um indutor. Assim como na configuração *Totem-Pole*, os interruptores precisam ser acionados isoladamente, uma vez que possuem referências distintas.

Figura 2.7 - Topologia Bridgeless Totem-Pole.

Fonte: Qingnan (2009).

Figura 2.8 - Topologia Bridgeless Pseudo Totem-Pole.

Fonte: Qingnan (2009).

#### 2.4.5. Análise de perdas por condução entre as topologias *Bridgeless*

O trabalho de LI; ANDERSEN e THOMSEN (2009) apresenta um estudo comparativo de perdas por condução e interferência eletromagnética de modo comum entre a topologia *boost* convencional e as topologias *bridgeless boost* citadas anteriormente. Neste estudo, para efeito de comparação, nenhuma das topologias opera com comutação suave.

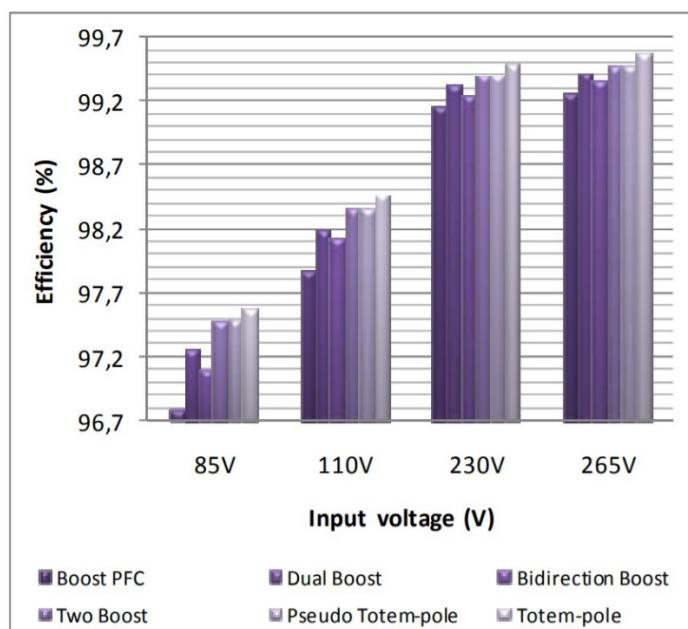

Como pode ser observado na Figura 2.9, as topologias *Totem-Pole*, *Two-Boost* e *Pseudo Totem-Pole*, foram as que apresentaram maior eficiência em relação às perdas por condução.

Figura 2.9 - Comparação de perdas por condução entre topologias *boost*.

Fonte: (LI; ANDERSEN; THOMSEN, 2009).

### 2.5.Métodos de Controle Por Corrente

Retificadores *boost* operando em modo de condução contínua (MCC) são largamente aplicados para sistemas de média e alta potência. Estudos sobre diferentes métodos de controle de corrente foram desenvolvidos para essa topologia, tais como o controle por corrente média (DIXON, 1997), controle por corrente de pico (NAJAFI et al., 2008), controle da corrente por histerese (ZHOU; RIDLEY; LEE, 1990), entre outros.

Os métodos de controle de corrente são projetados em malha fechada e visam moldar a corrente drenada de acordo com a tensão de entrada da rede, proporcionando baixa distorção harmônica de corrente e elevada eficiência ao sistema. Além disso, comparadas aos esquemas em malha aberta, estas técnicas de controle em malha fechada apresentam uma melhoria significativa no índice de distorção harmônica de corrente (DHI) e no fator de potência do sistema (PINHEIRO et al., 1999). Outra característica da técnica de controle de corrente é que ela introduz uma malha interna adicional ao sistema de controle, quando comparada à técnica de controle de tensão.

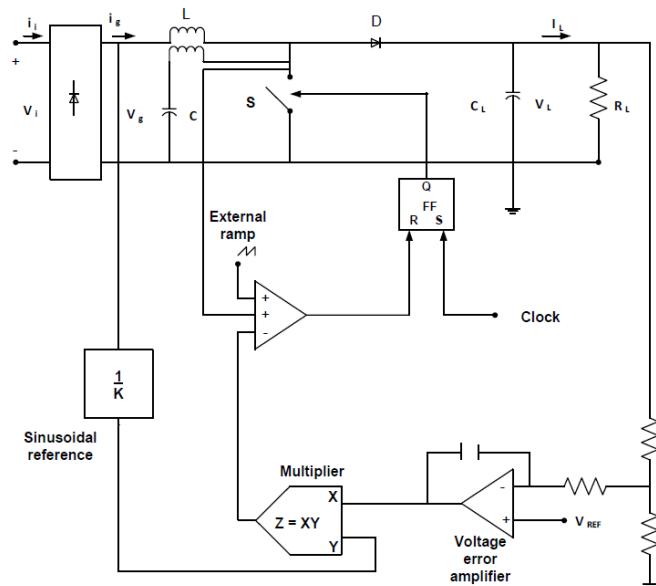

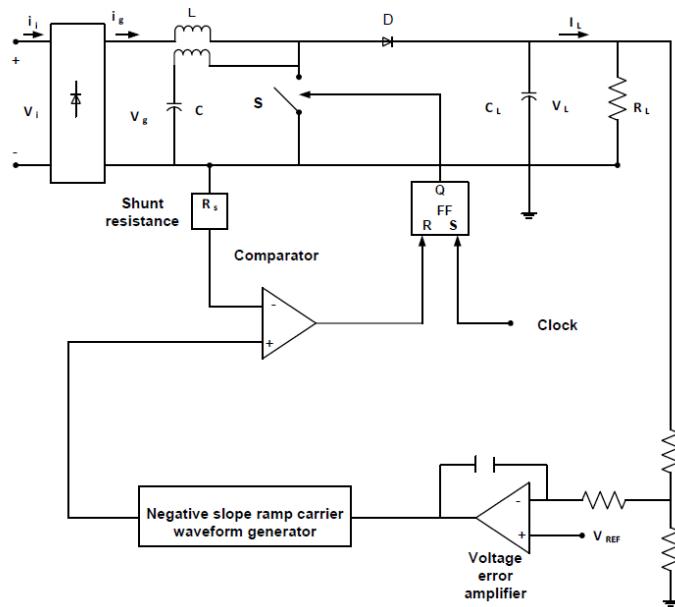

### 2.5.1. Controle por Corrente de Pico

O método de controle por corrente de pico, mostrado na Figura 2.10, se dá por meio da comparação da corrente instantânea do indutor com uma corrente de referência, a qual é geralmente obtida pela multiplicação do sinal de erro da tensão de saída e a senoide obtida pela tensão de entrada. Os interruptores permanecem ligados até que a soma entre a corrente no indutor e a rampa de compensação alcance a corrente senoidal de referência.

Em retificadores com correção do fator de potência é usual a utilização do controle por corrente média, contudo, o controle por corrente de pico costuma ser mais simples e/ou mais eficiente de se implementar (REDL; ERISMAN, 1994).

Figura 2.10 - Circuito de controle para o método de controle por corrente de pico.

Fonte: (REXY; SEYEZHAI, 2016).

Como características do método de controle por corrente de pico aplicado a retificadores *boost*, tem-se: Corrente de entrada em fase com a tensão, modulação realizada por razão cíclica e não necessidade de controlador de corrente, uma vez que o controle é feito de forma direta.

Uma das desvantagens do método é a presença de distorções na corrente drenada da rede devido ao *ripple* de corrente dos indutores e à rampa de compensação necessária para evitar instabilidade quando a razão cíclica fica acima de 50% (REDL; ERISMAN, 1994). Além disso, a distorção harmônica de corrente é maior que do método de controle por corrente média (CANESIN; BARBI, 1996).

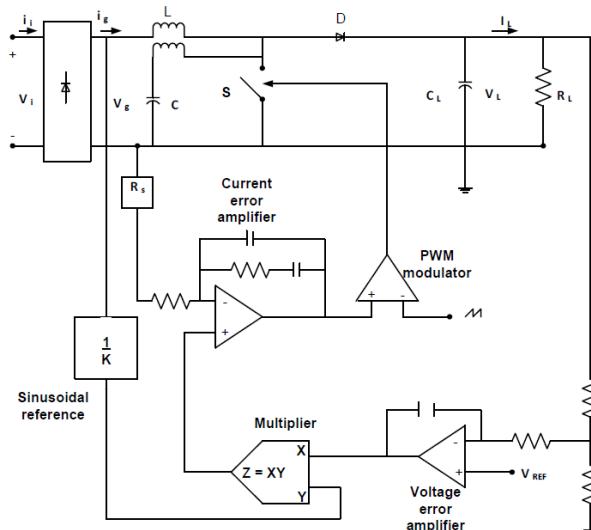

### 2.5.2. Controle por Corrente Média

A técnica de controle por corrente média é uma das mais populares, sendo utilizada em diversas aplicações devido à sua robustez (LARICO, 2007). O método consiste em uma malha externa de tensão e uma malha interna de corrente. O circuito de controle é apresentado na Figura 2.11. Inicialmente, a tensão de saída é comparada com o valor de referência e o erro gerado é amplificado. O sinal de erro é então multiplicado pela amostra da tensão senoidal de entrada retificada, gerando assim o sinal de referência

para a corrente, o qual é comparado com a corrente do indutor e, após passar por um filtro, é utilizado como sinal modulador do PWM.

Figura 2.11 - Circuito de controle para o método de controle por corrente média.

Fonte: (REXY; SEYEZHAI, 2016).

Este método é indicado para sistemas entrelaçados devido ao potencial problema de assimetria de correntes nas células conversoras (BALOGH; REDL, 1993). Assim, o controle por corrente média apresenta como principais características: corrente de entrada em fase com a tensão, corrente no retificador controlada diretamente através da malha de corrente, controle do fluxo de potência realizado por meio da amplitude da corrente de referência e modulação realizada por razão cíclica.

Dentre as desvantagens desse método de controle estão a necessidade de sensoriamento da corrente no indutor, da tensão de entrada e da tensão de saída, além da maior complexidade devido à presença da malha interna e externa de controle.

### 2.5.3. Controle da corrente por histerese

A técnica de controle por histerese baseia-se na limitação da corrente do indutor dentro de uma região, composta pela referência de corrente superior e pela referência de corrente inferior. Quando a corrente do indutor se torna menor que a referência inferior, o interruptor é ligado, e quando a corrente no indutor fica acima da referência superior, o

interruptor é desligado, forçando a corrente a retornar a valores abaixo da referência. A Figura 2.12 representa o circuito responsável pelo controle por histerese.

Figura 2.12 - Circuito de controle para o método de controle da corrente por histerese.

Fonte: (REXY; SEYEZHAI, 2016).

Este método, conforme apresentado em (ZHOU; RIDLEY; LEE, 1990), é muito utilizado devido a sua simplicidade de implementação, rápida resposta, baixa distorção na corrente de entrada e regulação da tensão de saída.

Por outro lado, esse método apresenta uma elevada distorção da corrente na passagem por zero. Além disso, esse circuito é mais sensível a ruídos e a modulação é realizada por frequência, sendo a comutação realizada com frequência variável.

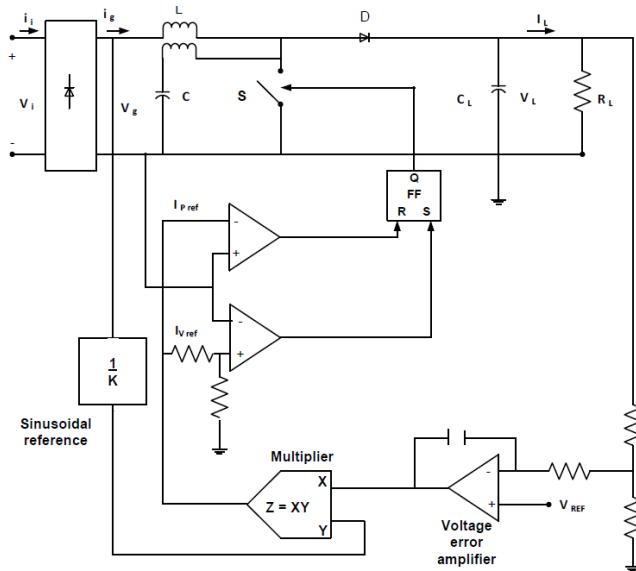

#### 2.5.4. Controle por portadora programada

O controle por portadora programada tem como principal característica o fato de se conseguir um elevado fator de potência sem a necessidade de sensoriamento da tensão de entrada. Nesse método, proposto em (MAKSIMOVIC; JANG; ERICKSON, 1995), a razão cíclica é determinada através da comparação de um sinal derivado da corrente do interruptor com um sinal não linear periódico. Dessa forma, a corrente média de entrada tende a seguir a tensão senoidal de entrada. A Figura 2.13 representa o circuito responsável por realizar esta técnica de controle.

Figura 2.13 - Circuito de controle para o método de controle por portadora programada.

Fonte: (REXY; SEYEZHAI, 2016).

No controle por portadora programada não se faz necessário a geração de uma corrente de referência nem o controlador de corrente. A operação se dá por modulação PWM e o circuito de controle é simples e permite um controle instantâneo da corrente.

Uma desvantagem desse método é que a corrente de entrada fica defasada em relação à tensão de entrada. Além disso, apresenta distorção da corrente na passagem por zero e não proporciona uma boa regulação da potência entregue à carga (LARICO, 2007).

## 2.6. Considerações Finais

Neste capítulo foi realizada uma revisão sobre as diversas características envolvidas no funcionamento dos conversores CA-CC da família *boost* para aplicações em que se busca um elevador fator de potência e baixa distorção harmônica na corrente drenada da rede. Além disso, é importante que o sistema seja capaz de regular a tensão CC de saída, mantendo-a constante em um nível preestabelecido e com uma rápida resposta.

Dentre os modos de operação quanto a corrente no indutor *boost*, o modo de condução contínua, na qual a corrente no indutor acompanha a corrente senoidal de referência com baixo *ripple*, se mostra adequado a aplicações de média e alta potência.

Apesar de requerer um circuito de controle mais complexo, esse modo de condução reduz as perdas magnéticas e a robustez do filtro EMI necessário.

A técnica de entrelaçamento, já amplamente analisada em diversos trabalhos, permite tornar o sistema mais eficiente, estável e robusto, uma vez que permite a divisão de esforços nos semicondutores de potência, reduzindo assim as perdas por recuperação reversa. Esta técnica também é responsável pela redução do *ripple* de alta frequência da corrente de entrada. Como a potência total do sistema é dividida entre as células entrelaçadas, o tamanho dos indutores *boost* também é reduzido, facilitando o seu projeto.

Estudos como o de (MUSAVID; EBERLE; DUNFORD, 2011) mostram que a maior parcela das perdas dos semicondutores presentes em retificadores *boost*, se concentra nos diodos da ponte retificadora de entrada. Assim, estruturas *bridgeless*, que não utilizam a ponte de diodos para realizar a etapa de retificação, contribuem ainda mais para o aumento da eficiência do sistema.

Dentre os diversos métodos de controle de corrente, o método convencional por corrente média é o que apresenta características mais vantajosas para o sistema objeto de estudo do presente trabalho, pois permite um controle preciso da tensão de saída, através da malha externa de tensão, e um controle direto da corrente de entrada, através da malha interna de corrente. Isso permite que a corrente drenada da rede esteja em fase com a tensão de entrada, aumentando o fator de potência do sistema, e que apresente reduzido índice de distorção harmônica de corrente.

Portanto, a estrutura analisada no presente trabalho engloba a técnica de entrelaçamento de células juntamente com um conversor da família *bridgeless*, estando cada célula conversora operando em modo de condução contínua e sendo controlada pelo método de controle por corrente média. A análise do princípio de funcionamento e as etapas de operação da estrutura, bem como o dimensionamento dos elementos de potência, são apresentados no capítulo seguinte.

### 3. CONVERSOR CA-CC BOOST ENTRELAÇADO SEM PONTE DE DIODOS OPERANDO EM MCC

#### 3.1. Considerações Iniciais

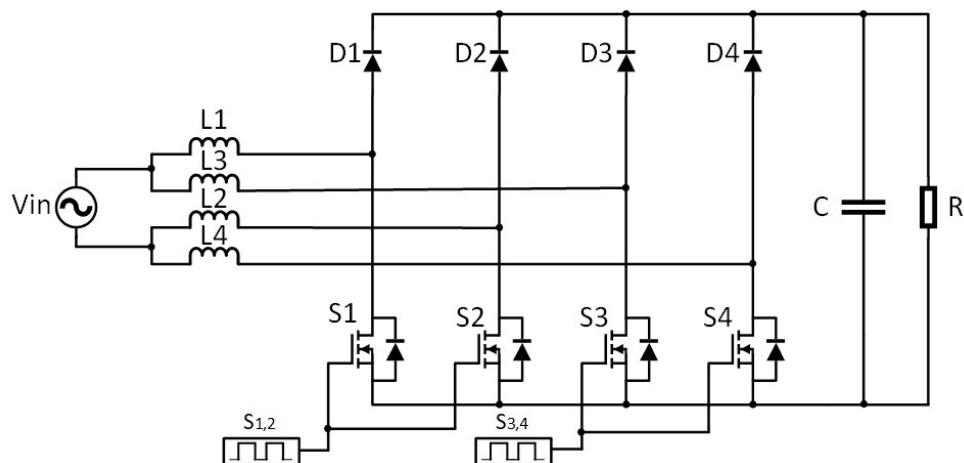

A topologia do Conversor CA-CC *Boost* Entrelaçado Sem Ponte de Diodos, proposta em (MUSAVI; EBERLE; DUNFORD, 2010) e analisada neste trabalho é apresentada na Figura 3.1. A estrutura utiliza quatro diodos de rápida recuperação reversa, quatro MOSFETs e quatro indutores na entrada da rede, além de um capacitor acoplado à saída.

A presença de um diodo em antiparalelo com cada semicondutor fornece um caminho para passagem da corrente elétrica, uma vez que os indutores não permitem variações instantâneas desta grandeza.

Figura 3.1 - Conversor CA-CC *Boost* Entrelaçado Sem Ponte de Diodos.

Fonte: Adaptado de (MUSAVI; EBERLE; DUNFORD, 2010).

A descrição do comportamento da topologia pode ser dividida em duas etapas, semiciclo positivo da rede e semiciclo negativo da rede.

Durante o semiciclo positivo da rede ( $V_{in} > 0$ ), quando os semicondutores  $S_1$  e  $S_2$  estão conduzindo, a corrente percorre o caminho passando por  $L_1$ , pelo semicondutor  $S_1$ , pelo semicondutor  $S_2$  e seu diodo em antiparalelo, e então por  $L_2$ , voltando à rede e armazenando energia nos indutores  $L_1$  e  $L_2$ . Já quando os semicondutores  $S_1$  e  $S_2$  deixam

de conduzir, passando para a condição de bloqueio, a energia armazenada nos indutores  $L_1$  e  $L_2$  é entregue à carga, passando a corrente pelo diodo  $D_1$ , pela carga, e então retornando pelo diodo em antiparalelo de  $S_2$ .

Ainda no semiciclo positivo da rede, devido ao entrelaçamento de células, o mesmo processo acontece para a célula *boost* formada por  $L_3$ ,  $L_4$ ,  $S_3$ ,  $S_4$ ,  $D_3$  e  $D_4$ , porém com um desfasamento de  $180^\circ$ , ou seja,  $T_S/2$ .

Durante o semiciclo negativo da rede ( $V_{in} < 0$ ), estando os semicondutores  $S_1$  e  $S_2$  conduzindo, a corrente percorre o caminho passando por  $L_2$ , pelo semicondutor  $S_2$ , pelo semicondutor  $S_1$  e seu diodo em antiparalelo, e então por  $L_1$ , voltando à rede e armazenando energia nos indutores  $L_2$  e  $L_1$ . Já quando os semicondutores  $S_1$  e  $S_2$  deixam de conduzir, passando para a condição de bloqueio, a energia armazenada nos indutores  $L_2$  e  $L_1$  é fornecida à carga, passando a corrente pelo diodo  $D_2$ , pela carga, e então retornando pelo diodo em antiparalelo de  $S_1$ .

Novamente, devido ao entrelaçamento, o mesmo processo acontece durante o semiciclo negativo para a segunda célula *boost* formada por  $L_3$ ,  $L_4$ ,  $S_3$ ,  $S_4$ ,  $D_3$  e  $D_4$ , porém com um desfasamento de  $180^\circ$ .

### 3.2. Etapas de Operação do Conversor

Durante um período de chaveamento, o conversor da Figura 3.1 apresenta quatro intervalos de funcionamento, definidos pela condição de condução e bloqueio dos pares de semicondutores  $S_1$  e  $S_2$ ,  $S_3$  e  $S_4$ . Além disso, os intervalos de operação para o conversor operando com  $D < 0,5$  são diferentes dos intervalos observados para  $D > 0,5$ . Contudo, o funcionamento geral do sistema não se altera, sendo a análise para um dos casos suficiente para a obtenção das equações que regem o circuito.

Em qualquer dos semiciclos da rede, a razão cíclica poderá ser maior que 0,5, quando a tensão de saída for maior que o dobro da tensão de entrada, ou menor que 0,5, quando a tensão de saída for menor que o dobro da tensão de entrada.

Na análise do funcionamento do circuito apresentada a seguir, tanto para  $D < 0,5$  quanto para  $D > 0,5$ , assume-se que:

- 1) A tensão de entrada  $V_{in}$  é considerada constante durante um período de chaveamento, uma vez que a frequência de chaveamento é muito maior que a frequência da rede;

- 2) Todos elementos do circuito são considerados ideais;

- 3) O *ripple* da tensão no capacitor e corrente nos indutores é desconsiderado;

- 4) Considera-se uma carga puramente resistiva.

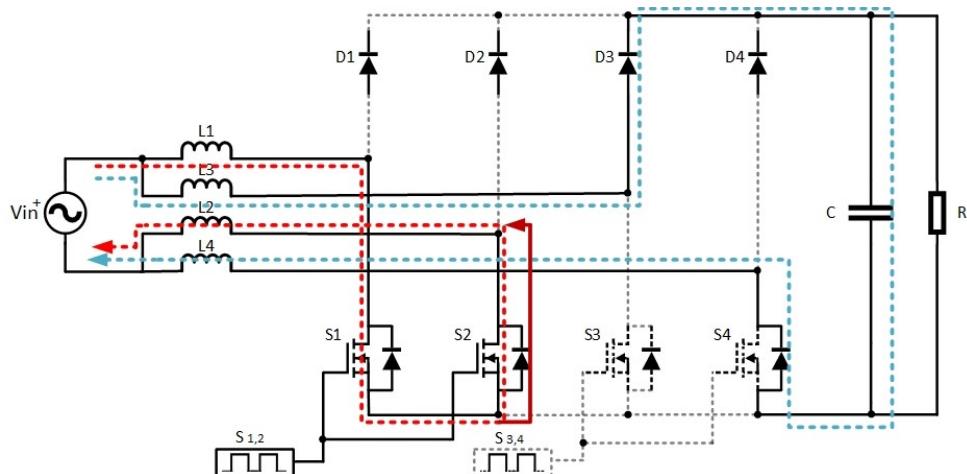

### 3.2.1. Análise para $D > 0,5$

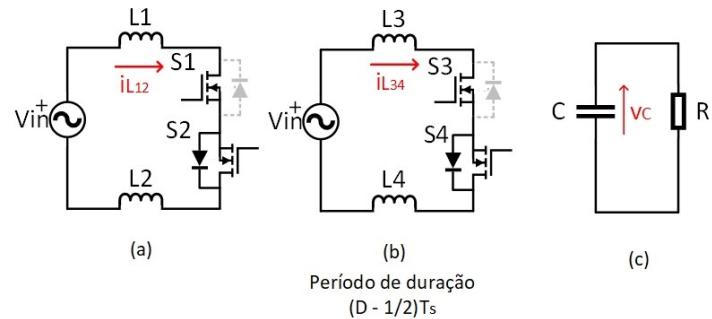

Considerando o semiciclo positivo da rede e razão cíclica maior que 0,5, os intervalos de operação do circuito são apresentados pela Figura 3.2, Figura 3.3 e pela Figura 3.4. As principais formas de onda da corrente nos elementos do circuito são apresentadas na Figura 3.5.

Figura 3.2 - - Intervalo 1: Semicondutores  $S_1$ ,  $S_2$  e diodo em antiparalelo de  $S_4$  conduzindo

Figura 3.3 - Intervalo 2 e 4: Semicondutores  $S_1$ ,  $S_2$ ,  $S_3$  e  $S_4$  conduzindo.Figura 3.4 - Intervalo 3: Semicondutores  $S_3$ ,  $S_4$  e diodo em antiparalelo de  $S_2$  conduzindo.

Figura 3.5 - Formas de onda para razão cíclica maior que 0,5.

Fonte: Adaptado de (MUSAVI; EBERLE; DUNFORD, 2010).

### Intervalo 1 [ $t_0 - t_1$ ]

No instante  $t_0$ , os semicondutores  $S_1$  e  $S_2$  estão conduzindo e os semicondutores  $S_3$  e  $S_4$  passam para a condição de bloqueio, como mostra a Figura 3.2.

Nesta etapa do funcionamento do circuito a corrente que percorre  $L_1$  e  $L_2$  aumenta linearmente com o tempo e armazena energia nesses indutores. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $S_1$ ,  $S_2$  e seu diodo em antiparalelo e por  $L_2$ .

Já para a segunda célula *boost*, a corrente que passa pelos indutores  $L_3$  e  $L_4$  diminui linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $D_3$ ,  $C$ , pelo diodo em antiparalelo de  $S_4$  e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = v_{in} \quad (3.1)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = -v_C + v_{in} \quad (3.2)$$

$$i_C = C \frac{dv_C}{dt} = i_{L34} - \frac{1}{R} v_C \quad (3.3)$$

#### Intervalo 2 [ $t_1 - t_2$ ]

No instante  $t_1$ , os semicondutores  $S_1$  e  $S_2$  continuam conduzindo e os semicondutores  $S_3$  e  $S_4$  passam à condição de condução, como mostra a Figura 3.3.

Nesta etapa do funcionamento do circuito a corrente que percorre  $L_1$  e  $L_2$  e a corrente que percorre  $L_3$  e  $L_4$  aumentam linearmente com o tempo e armazenam energia nos quatro indutores. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $S_1$ ,  $S_2$  e seu diodo em antiparalelo e por  $L_2$ .

Já para a segunda célula *boost*, a corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $S_3$ ,  $S_4$  e seu diodo em antiparalelo e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = v_{in} \quad (3.4)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = v_{in} \quad (3.5)$$

$$i_C = C \frac{dv_C}{dt} = -\frac{1}{R} v_C \quad (3.6)$$

#### Intervalo 3 [ $t_2 - t_3$ ]

No instante  $t_2$ , os semicondutores  $S_1$  e  $S_2$  passam para a condição de bloqueio e os semicondutores  $S_3$  e  $S_4$  continuam conduzindo, como mostra a Figura 3.4.

Nesta etapa do funcionamento do circuito a corrente que percorre os indutores  $L_1$  e  $L_2$  diminui linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L12}$ ,

da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $D_1$ ,  $C$ , pelo diodo em antiparalelo de  $S_2$  e por  $L_2$ .

Já para a segunda célula *boost*, a corrente que passa por  $L_3$  e  $L_4$  aumenta linearmente com o tempo e armazena energia nesses indutores. A corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $S_3$ ,  $S_4$  e seu diodo em antiparalelo e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = -v_C + v_{in} \quad (3.7)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = v_{in} \quad (3.8)$$

$$i_C = C \frac{dv_C}{dt} = i_{L12} - \frac{1}{R} v_C \quad (3.9)$$

#### Intervalo 4 [ $t_3 - t_4$ ]

No instante  $t_3$ , os semicondutores  $S_1$  e  $S_2$  voltam à condição de condução e os semicondutores  $S_3$  e  $S_4$  continuam conduzindo, como mostra a Figura 3.3.

Nesta etapa do funcionamento do circuito a corrente que percorre  $L_1$  e  $L_2$  e a corrente que percorre  $L_3$  e  $L_4$  aumentam linearmente com o tempo e armazenam energia nos quatro indutores. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $S_1$ ,  $S_2$  e seu diodo em antiparalelo e por  $L_2$ .

Já para a segunda célula *boost*, a corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $S_3$ ,  $S_4$  e seu diodo em antiparalelo e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = v_{in} \quad (3.10)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = v_{in} \quad (3.11)$$

$$i_C = C \frac{dv_C}{dt} = -\frac{1}{R} v_C \quad (3.12)$$

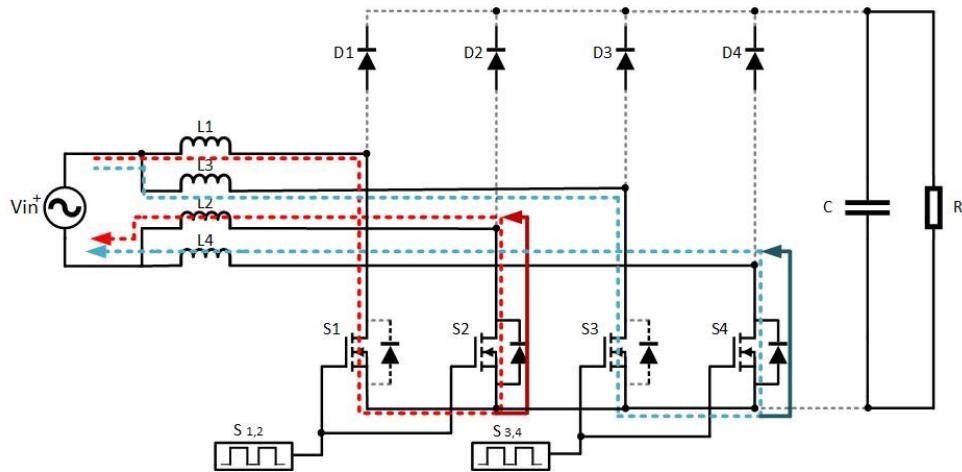

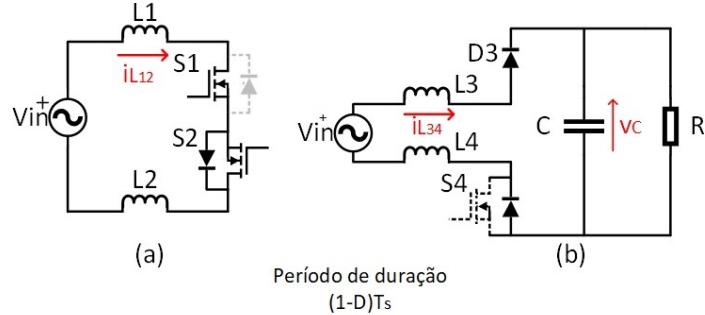

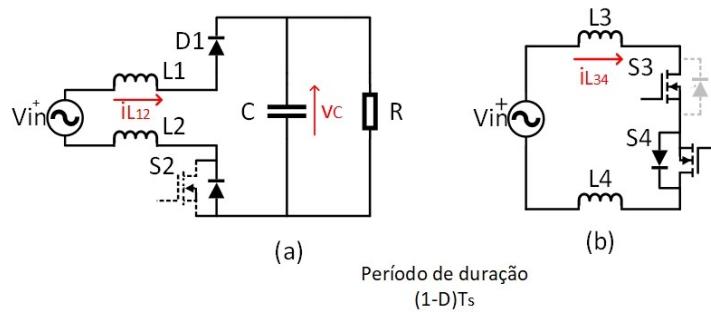

### 3.2.2. Análise para $D < 0,5$

Considerando agora que a razão cíclica do sistema seja menor que 0,5 e que a rede esteja em seu semicírculo positivo, a Figura 3.6, a Figura 3.7 e a Figura 3.8 mostram os intervalos de operação do circuito e a Figura 3.9 as principais formas de onda da corrente nos elementos do circuito.

Figura 3.6 - Intervalo 1 e 3: Diodos em antiparalelo de  $S_2$  e  $S_4$  conduzindo.

Figura 3.7 - Intervalo 2: Semicondutores  $S_1$ ,  $S_2$  e diodo em antiparalelo de  $S_4$  conduzindo.

Figura 3.8 - Intervalo 4: Semicondutores  $S_3$ ,  $S_4$  e diodo em antiparalelo de  $S_2$  conduzindo.

Figura 3.9 - Formas de onda para razão cílica menor que 0,5.

Fonte: Adaptado de (MUSAVI; EBERLE; DUNFORD, 2010).

### Intervalo 1 $[t_0 - t_1]$

No instante  $t_0$ , os semicondutores  $S_1$  e  $S_2$  estão na condição de bloqueio e os semicondutores  $S_3$  e  $S_4$  passam para a condição de condução, como mostra a Figura 3.6.

Nesta etapa do funcionamento do circuito a corrente que percorre os indutores  $L_1$  e  $L_2$  e a corrente que percorre os indutores  $L_3$  e  $L_4$  diminuem linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $D_1$ ,  $C$ , pelo diodo em antiparalelo de  $S_2$  e por  $L_2$ .

Já para a segunda célula *boost*, a corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $D_3$ ,  $C$ , pelo diodo em antiparalelo de  $S_4$  e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = -v_C + v_{in} \quad (3.13)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = -v_C + v_{in} \quad (3.14)$$

$$i_C = C \frac{dv_C}{dt} = i_{L12} + i_{L34} - \frac{1}{R} v_C \quad (3.15)$$

### Intervalo 2 $[t_1 - t_2]$

No instante  $t_1$ , os semicondutores  $S_1$  e  $S_2$  passam à condição de condução e os semicondutores  $S_3$  e  $S_4$  permanecem na condição de bloqueio, como mostra a Figura 3.7.

Nesta etapa do funcionamento do circuito a corrente que percorre  $L_1$  e  $L_2$  aumenta linearmente com o tempo, armazenando energia nesses indutores. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $S_1$ ,  $S_2$  e seu diodo em antiparalelo e por  $L_2$ .

Já para a segunda célula *boost*, a corrente que percorre os indutores  $L_3$  e  $L_4$  diminui linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $D_3$ ,  $C$ , pelo diodo em antiparalelo de  $S_4$  e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = v_{in} \quad (3.16)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = -v_C + v_{in} \quad (3.17)$$

$$i_C = C \frac{dv_C}{dt} = i_{L34} - \frac{1}{R} v_C \quad (3.18)$$

#### Intervalo 3 $[t_2 - t_3]$

No instante  $t_2$ , os semicondutores  $S_1$  e  $S_2$  retornam à condição de bloqueio e os semicondutores  $S_3$  e  $S_4$  continuam bloqueados, como mostra a Figura 3.6.

Nesta etapa do funcionamento do circuito a corrente que percorre os indutores  $L_1$  e  $L_2$  e a corrente que percorre os indutores  $L_3$  e  $L_4$  diminuem linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $D_1$ ,  $C$ , pelo diodo em antiparalelo de  $S_2$  e por  $L_2$ .

Já para a segunda célula *boost*, a corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $D_3$ ,  $C$ , pelo diodo em antiparalelo de  $S_4$  e por  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = -v_C + v_{in} \quad (3.19)$$

$$v_{L3} + v_{L4} = (L_3 + L_4) \frac{di_{L34}}{dt} = -v_C + v_{in} \quad (3.20)$$

$$i_C = C \frac{dv_C}{dt} = i_{L12} + i_{L34} - \frac{1}{R} v_C \quad (3.21)$$

#### Intervalo 4 $[t_3 - t_4]$

No instante  $t_3$ , os semicondutores  $S_1$  e  $S_2$  permanecem na condição de bloqueio e os semicondutores  $S_3$  e  $S_4$  passam à condição de condução, como mostra a Figura 3.8.

Nesta etapa do funcionamento do circuito a corrente que percorre os indutores  $L_1$  e  $L_2$  diminui linearmente com o tempo, transferindo energia para a carga. A corrente  $i_{L12}$ , da primeira célula *boost*, percorre o circuito passando por  $L_1$ ,  $D_1$ ,  $C$ , pelo diodo em antiparalelo de  $S_2$  e por  $L_2$ .

Já para a segunda célula *boost*, a corrente que percorre  $L_3$  e  $L_4$  aumenta linearmente com o tempo, armazenando energia nesses indutores. A corrente  $i_{L34}$  percorre o circuito passando por  $L_3$ ,  $S_3$ ,  $S_4$  e seu diodo em antiparalelo e  $L_4$ .

Nesta etapa, a tensão sobre os indutores em série  $L_1$  e  $L_2$ , a tensão sobre os indutores em série  $L_3$  e  $L_4$  e a corrente que passa pelo capacitor  $C$ , são dadas por:

$$v_{L1} + v_{L2} = (L_1 + L_2) \frac{di_{L12}}{dt} = -v_C + v_{in} \quad (3.22)$$