UNIVERSIDADE FEDERAL DE UBERLÂNDIA

FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

NUPEP - NÚCLEO DE PESQUISA EM ELETRÔNICA DE

POTÊNCIA

PAULO RICARDO DA SILVA

ANÁLISE DE TRÊS TÉCNICAS DE CONTROLE PARA

EMPREGO DE UM CONVERSOR BOOST TRIFÁSICO EM

UMA ESTRUTURA RETIFICADORA HÍBRIDA COM

SUPORTABILIDADE A AFUNDAMENTOS DE TENSÃO

UFU

2018

**PAULO RICARDO DA SILVA<sup>1</sup>**

**ANÁLISE DE TRÊS TÉCNICAS DE CONTROLE PARA

EMPREGO DE UM CONVERSOR BOOST TRIFÁSICO EM

UMA ESTRUTURA RETIFICADORA HÍBRIDA COM

SUPORTABILIDADE A AFUNDAMENTOS DE TENSÃO**

Dissertação de mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), perante a banca de examinadores abaixo, como parte dos requisitos necessários para obtenção do grau de Mestre em Ciências.

Área de Concentração: Sistema de Energia Elétrica.

Orientador: Dr. Luiz Carlos Gomes de Freitas.

Coorientador: Dr. Danillo Borges Rodrigues

Banca Examinadora:

Dr. Luiz Carlos Gomes de Freitas (UFU)

Dr. Danillo Borges Rodrigues (UFTM)

Dr. Gustavo Brito de Lima (UFU)

Dr. Antônio de Pádua Finazzi (UFMT)

Uberlândia

2018

---

<sup>1</sup> A Bolsa de Estudos, para esta pesquisa, foi concedida pela CAPES, Brasil.

Dados Internacionais de Catalogação na Publicação (CIP)

Sistema de Bibliotecas da UFU, MG, Brasil.

---

S586a Silva, Paulo Ricardo da, 1991-

2018 Análise de três técnicas de controle para emprego de um conversor boost trifásico em uma estrutura retificadora híbrida com suportabilidade a afundamentos de tensão / Paulo Ricardo da Silva. - 2018.

118 f. : il.

Orientador: Luiz Carlos Gomes de Freitas.

Coorientador: Danillo Borges Rodrigues.

Dissertação (mestrado) - Universidade Federal de Uberlândia, Programa de Pós-Graduação em Engenharia Elétrica.

Disponível em: <http://dx.doi.org/10.14393/ufu.di.2018.1167>

Inclui bibliografia.

1. Engenharia elétrica - Teses. 2. Conversores de corrente elétrica - Teses. 3. Retificadores de corrente elétrica - Teses. I. Freitas, Luiz Carlos Gomes de, 1976- II. Rodrigues, Danillo Borges, 1986- III. Universidade Federal de Uberlândia. Programa de Pós-Graduação em Engenharia Elétrica. IV. Título.

---

CDU: 621.3

Maria Salete de Freitas Pinheiro – CRB6/1262

**ANÁLISE DE TRÊS TÉCNICAS DE CONTROLE PARA

EMPREGO DE UM CONVERSOR BOOST TRIFÁSICO EM

UMA ESTRUTURA RETIFICADORA HÍBRIDA COM

SUPORTABILIDADE A AFUNDAMENTOS DE TENSÃO**

**PAULO RICARDO DA SILVA**

Dissertação de mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), como parte dos requisitos necessários para obtenção do grau de Mestre em Ciências.

Área de Concentração: Sistema de Energia Elétrica.

---

Prof. Luiz Carlos Gomes de Freitas, Dr.

Orientador

---

Prof. Danillo Borges Rodrigues, Dr.

Coorientador

---

Prof. Alexandre Cardoso, Dr.

Coordenador da Pós-Graduação em Engenharia Elétrica da UFU

Dedico a realização desta dissertação a meus pais, Edvaldo Nascimento e Elenilda Adelaide, à minha mulher Najara Zago e ao meu filho Brian Ricardo por me darem condições de realizar esta pós-graduação, assim como seu apoio e compreensão durante esses últimos dois anos. Dedico também ao Prof. Dr. Luiz Carlos Gomes de Freitas e ao Prof. Dr. Danillo Borges Rodrigues não só pelos ensinamentos durante todo o mestrado, mas também por acreditarem neste projeto desde o início.

# **AGRADECIMENTOS**

Aos meus pais, Edvaldo e Elenilda, que sempre me apoiaram incondicionalmente nas minhas decisões e sempre foram meus exemplos de determinação e integridade pessoal.

À minha mulher, Najara, que vivenciou com plenitude o desenvolvimento do mestrado, sempre demonstrando companheirismo, dedicação, paciência e carinho. Você é fundamental em tudo que faço, essa conquista é nossa.

Ao meu filho Brian Ricardo, do qual me orgulho tanto e sou profundamente grato.

Minha profunda gratidão ao meu orientador, prof. Luiz Carlos, pela paciência e por ter permitido a continuidade dos meus estudos e pela confiança depositada no meu trabalho. Obrigado por acreditar no meu potencial, e principalmente obrigado por todos os ensinamentos profissionais e pessoais que nossa convivência me proporcionou. Tenho grande admiração por você!

Agradeço a todos os professores que me ajudaram nessa jornada, em especial ao prof. Danillo Rodrigues que me acompanhou durante todo o desenvolvimento desta pesquisa e pela contribuição neste trabalho, nada disso seria possível sem sua ajuda.

Enfim, agradeço a todos aqueles que de forma direta ou indireta contribuíram para o desenvolvimento deste trabalho.

*“Seja você a mudança que quer ver no mundo”*

*Mahatma Gandhi*

## RESUMO

Esta dissertação apresenta a análise, o desenvolvimento teórico e a comparação dos métodos de controle por: (i) PWM; (ii) Histerese; e (iii) dq0, de um conversor Boost trifásico quando aplicado a uma estrutura retificadora híbrida trifásica que realiza a imposição de correntes de linha de entrada senoidais e a regulação de tensão no barramento CC, tanto para condições normais de suprimento da rede elétrica como para condições de afundamentos temporários de tensão na rede CA.

Com o intuito de comparar os três métodos de controle foram analisados os índices de distorção harmônica total de corrente, fator de potência e nível da tensão no barramento CC. Para simulações computacionais e análises matemáticas utilizaram-se os softwares *PSim®* e *Matlab®*, respectivamente.

Para corroborar com a teoria exposta e com as análises de simulação computacional, um protótipo de 5 kW baseado em DSP foi construído e ensaios experimentais realizados em laboratório permitiram demonstrar que os três métodos de controle, assim como demonstrado na análise computacional, asseguram correntes senoidais na entrada da rede e são capazes de regular e manter a tensão no barramento CC constante.

**Palavras-Chave:** Conversor; Controle; Histerese; PWM; dq0; Retificadores Híbridos.

# Abstract

This dissertation presents the analysis, the theoretical development and the comparison of the control methods by: (i) PWM; (ii) Hysteresis; and (iii) dq0, of a three-phase Boost converter when applied to a three-phase hybrid rectifier structure that performs the imposition of sinusoidal input line currents and voltage regulation on the DC bus, both for normal power supply conditions and for conditions Voltages in the AC network.

In order to compare the three control methods, the total harmonic distortion indexes of current, power factor and voltage level in the DC bus were analyzed. For computational simulations and mathematical analysis, the software PSim® and Matlab®, respectively, were used.

In order to corroborate with the exposed theory and computational simulation analyzes, a prototype of 5 kW based on DSP was constructed and experimental tests carried out in the laboratory allowed to demonstrate that the three control methods, as demonstrated in the computational analysis, ensure sinusoidal currents in line and are able to regulate and maintain the voltage on the constant DC bus.

**Keywords:** *Converter; Control; Hysteresis; PWM; Dq0; Hybrid Rectifiers.*

## LISTA DE FIGURAS

|                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURA 1 DIAGRAMA ESQUEMÁTICO DE UMA MICRORREDE CC.....                                                                                                                   | 21 |

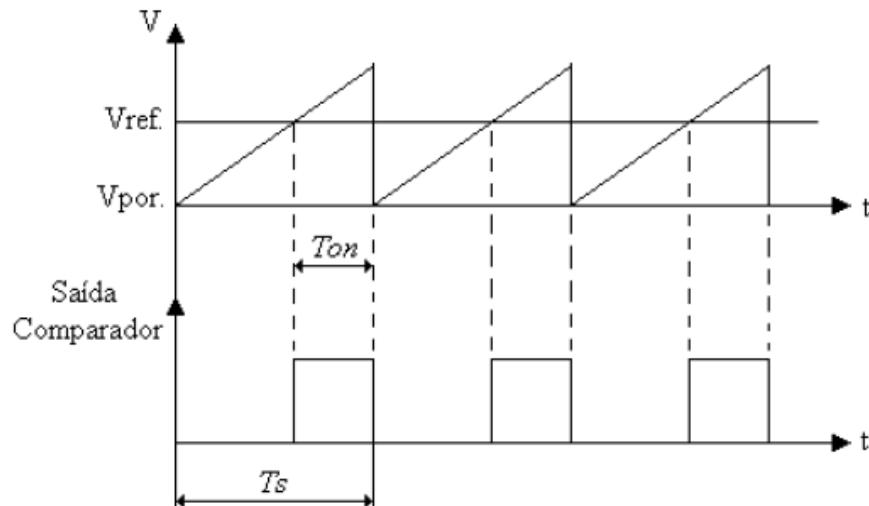

| FIGURA 2 DEMONSTRATIVO DE SINAL GERADO NA SAÍDA DA MODULAÇÃO POR PWM.....                                                                                                 | 23 |

| FIGURA 3 RELAÇÃO ENTRE OS SISTEMAS DE COORDENADAS ‘ABC’, ‘AB0’ E ‘DQ0’.....                                                                                               | 23 |

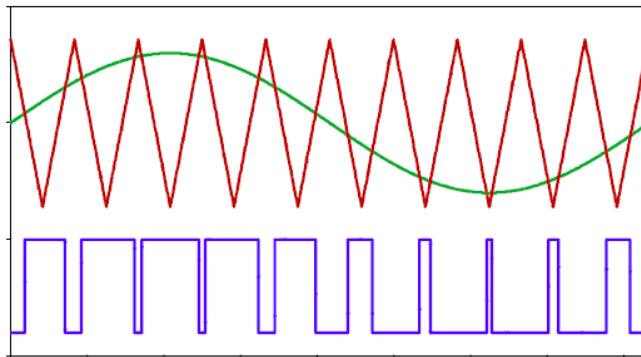

| FIGURA 4 MODELO DE MONITORAÇÃO DA CORRENTE ATRAVÉS DA FAIXA DE HISTERESE.....                                                                                             | 24 |

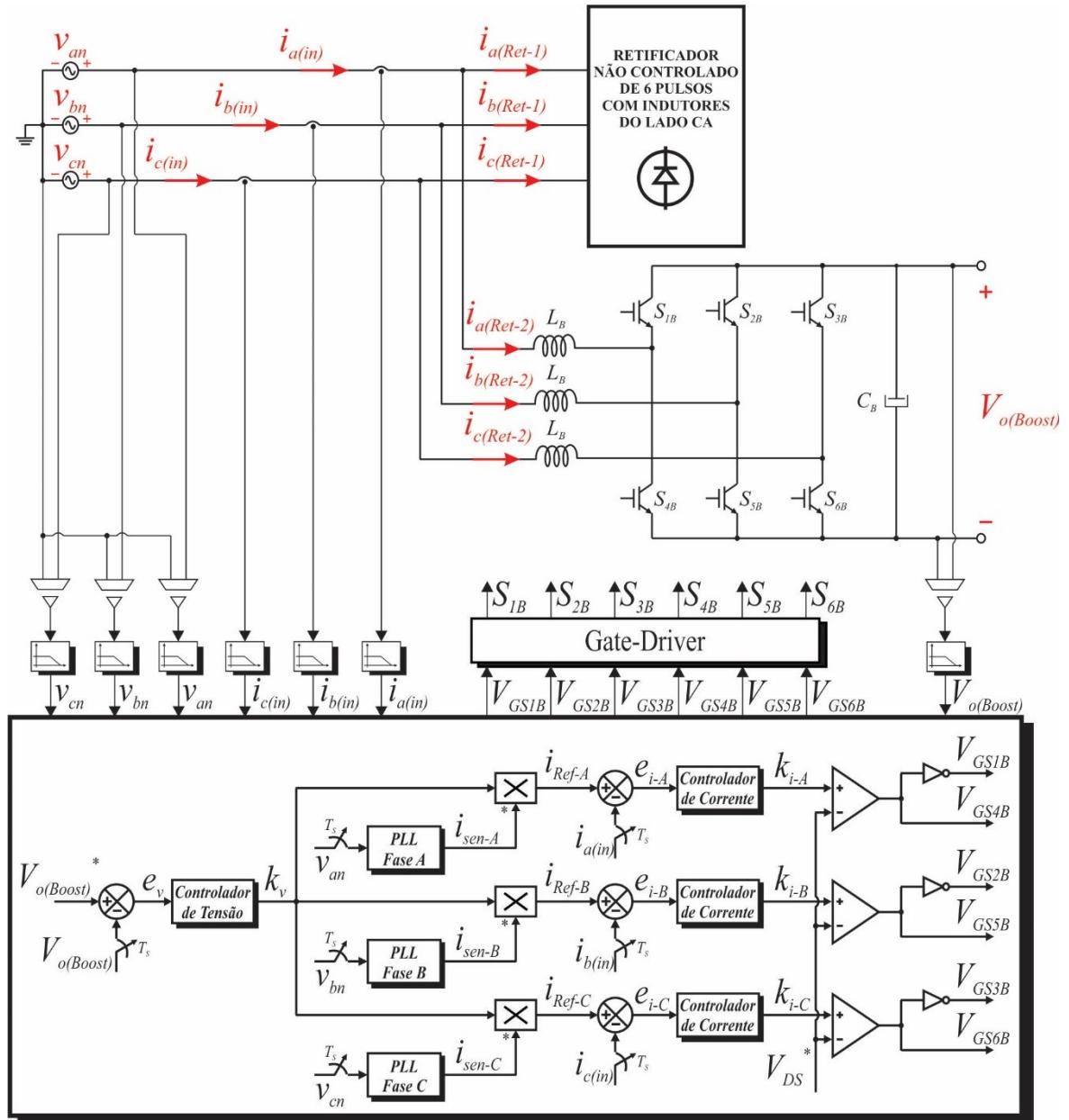

| FIGURA 5 ESTRUTURA RETIFICADORA HÍBRIDA TRIFÁSICA (RHT) PROPOSTA EM [27].....                                                                                             | 26 |

| FIGURA 6 DIAGRAMA ESQUEMÁTICO DO CIRCUITO DE CONTROLE DO CONVERSOR FULL-BRIDGE.....                                                                                       | 29 |

| FIGURA 7 CIRCUITO DO CONVERSOR BOOST TRIFÁSICO SIMPLIFICADO PARA ANÁLISE.....                                                                                             | 30 |

| FIGURA 8 REPRESENTAÇÃO VETORIAL DAS TENSÕES DE FASE E DE LINHA.....                                                                                                       | 31 |

| FIGURA 9 REPRESENTAÇÃO VETORIAL DAS TENSÕES DE FASE E DE LINHA, COM A REFERÊNCIA CONVENIENTEMENTE DESLOCADA (ATRASADA 60° EM RELAÇÃO À REFERÊNCIA DA FIGURA 8).....       | 31 |

| FIGURA 10 CIRCUITOS EQUIVALENTES DAS SEQUÊNCIAS A; 0; B; D; C; Q.....                                                                                                     | 32 |

| FIGURA 11 CIRCUITO EQUIVALENTE VISTO PELA SAÍDA (CC) DO CONVERSOR BOOST.....                                                                                              | 33 |

| FIGURA 12 CIRCUITO EQUIVALENTE PARA O CONVERSOR BOOST, VISTO PELA ENTRADA OU PELA SAÍDA, QUANDO APLICADA A TRANSFORMAÇÃO DE PARK.....                                     | 34 |

| FIGURA 13 LÓGICA DE VARIAÇÃO DOS SINAIS DE GATILHO DOS INTERRUPTORES S1B E S4B DO CONVERSOR BOOST POR DQ0.....                                                            | 36 |

| FIGURA 14 DIAGRAMA ESQUEMÁTICO DO CIRCUITO DE CONTROLE DO CONVERSOR BOOST POR DQ0.....                                                                                    | 37 |

| FIGURA 15 CIRCUITO EQUIVALENTE VISTO PELA CORRENTE I_12 (t).....                                                                                                          | 38 |

| FIGURA 16 REPRESENTAÇÃO POR DIAGRAMA DE BLOCOS PARA O SISTEMA DE CONTROLE POR DQ0.....                                                                                    | 38 |

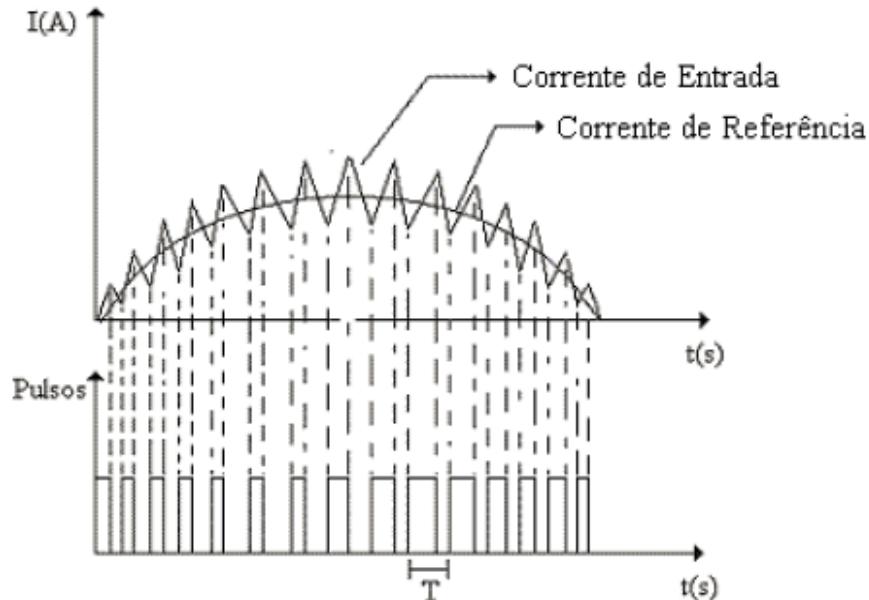

| FIGURA 17 COMPORTAMENTO DA CORRETE NO INDUTOR DO FILTRO NO CONTROLE POR HISTERESE PELA CORRENTE MÉDIA.....                                                                | 42 |

| FIGURA 18 DIAGRAMA DE BLOCOS REPRESENTANDO O CONTROLE POR HISTERESE PELA CORRENTE MÉDIA.....                                                                              | 42 |

| FIGURA 19 DIAGRAMA ESQUEMÁTICO DO CIRCUITO DE CONTROLE DO CONVERSOR BOOST POR HISTERESE.....                                                                              | 44 |

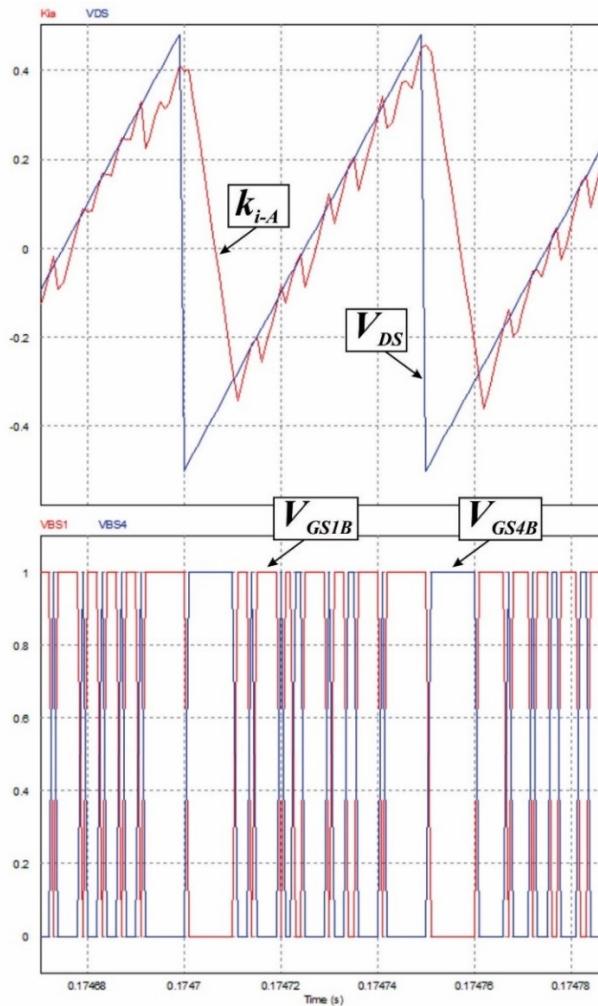

| FIGURA 20 LÓGICA DE VARIAÇÃO DOS SINAIS DE GATILHO DOS INTERRUPTORES S1B E S4B DO CONVERSOR BOOST POR HISTERESE.....                                                      | 45 |

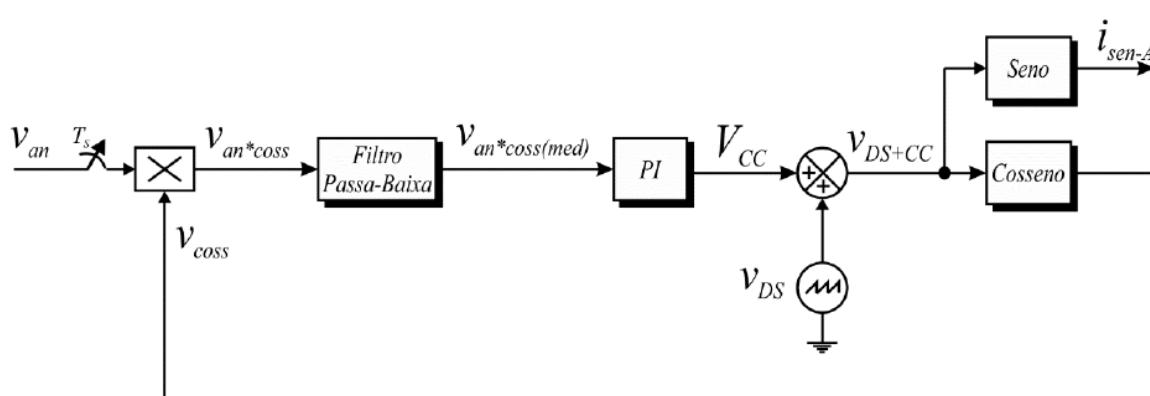

| FIGURA 21 DIAGRAMA ESQUEMÁTICO DO PLL IMPLEMENTADO PARA A FASE A.....                                                                                                     | 46 |

| FIGURA 22 RELAÇÃO ENTRE O NÍVEL CC DA ONDA DENTE-DE-SERRA E A FASE DA SENÓIDE DE SAÍDA DO PLL ...                                                                         | 46 |

| FIGURA 23 REPRESENTAÇÃO DOS SINAIS INTERNOS GERADOS NA IMPLEMENTAÇÃO DO PLL.....                                                                                          | 47 |

| FIGURA 24 DIAGRAMA DE BLOCOS DO SISTEMA EQUIVALENTE DO CONVERSOR BOOST COM CONTROLE POR HISTERESE: (A) EM MALHA FECHADA E (B) EM MALHA ABERTA.....                        | 48 |

| FIGURA 25 EXECUÇÃO DA SOLUÇÃO DO MODELO MATEMÁTICO DO CONVERSOR BOOST POR HISTERESE PARA O DEGRAU NAS AMPLITUDES DAS REFERÊNCIAS DE CORRENTE.....                         | 49 |

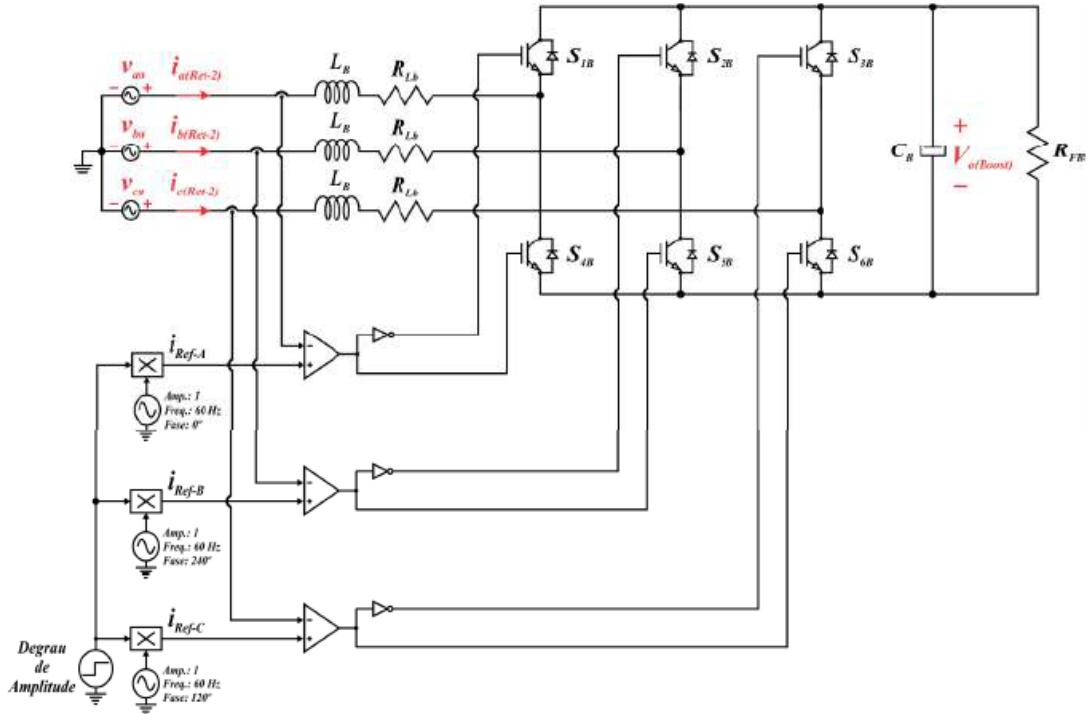

| FIGURA 26 FORMAS DE ONDA (A) DAS RESPOSTAS DAS CORRENTES DRENADAS POR RET-2 E (B) DA RESPOSTA DE Vo(BOOST) AO DEGRAU DE AMPLITUDE DAS REFERÊNCIAS DE CORRENTE.....        | 51 |

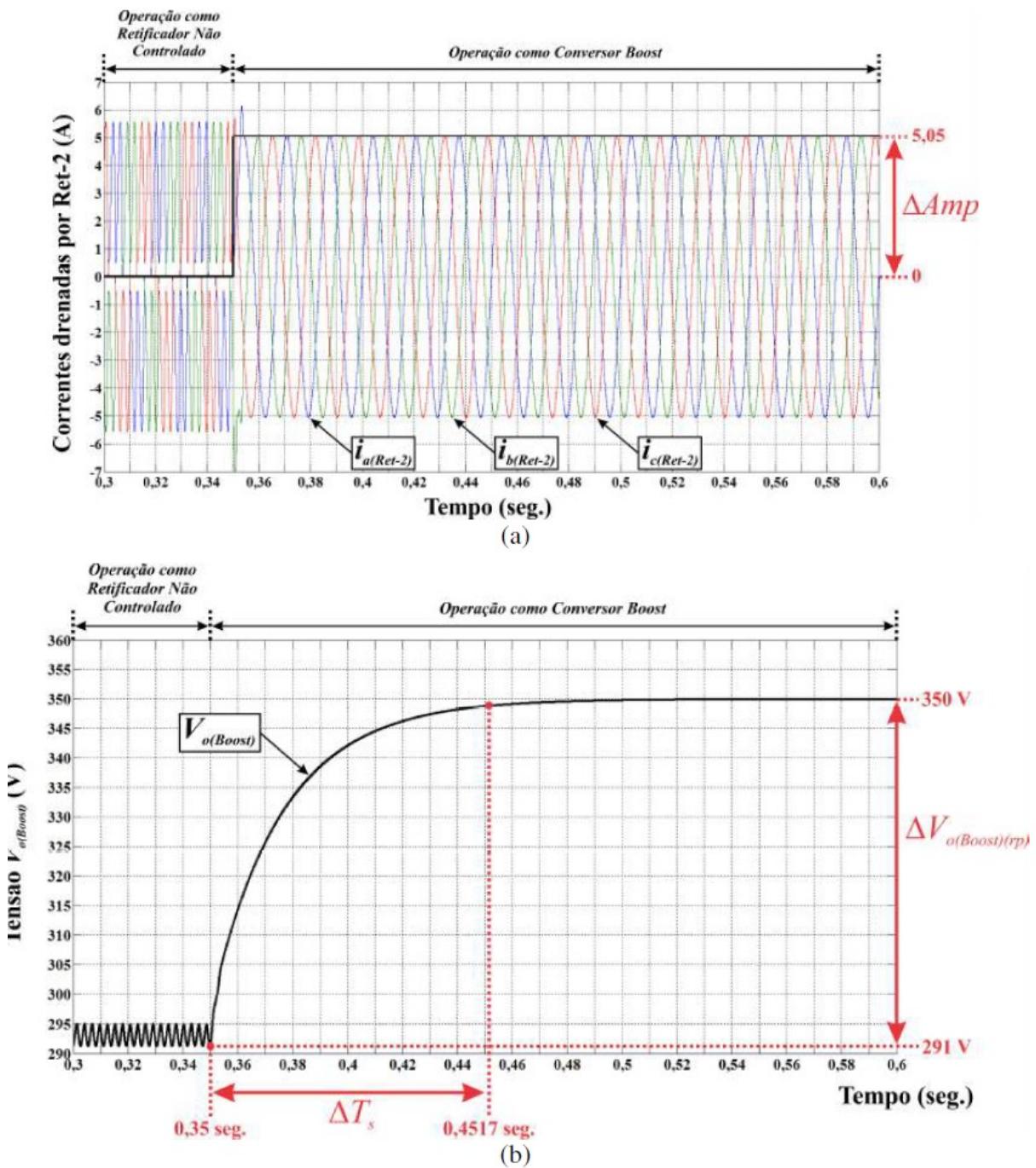

| FIGURA 27 SISTEMA DO CONVERSOR BOOST POR HISTERESE EM MALHA FECHADA SEM COMPENSAÇÃO: (A) LUGAR GEOMÉTRICO DAS RAÍZES, (B) DIAGRAMAS DE BODE E (C) RESPOSTA AO DEGRAU..... | 52 |

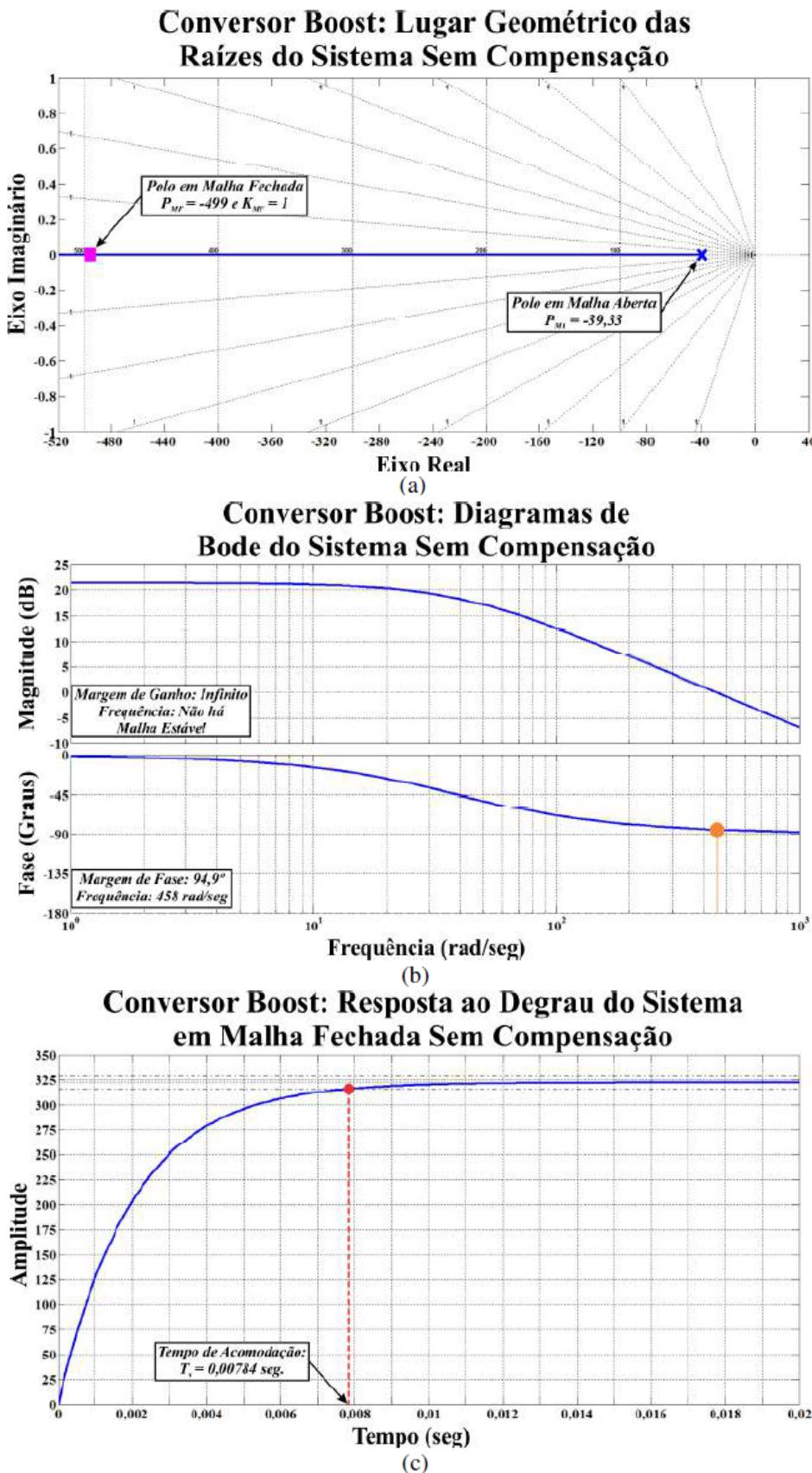

| FIGURA 28 SISTEMA DO CONVERSOR BOOST POR HISTERESE EM MALHA FECHADA COMPENSADO: (A) LUGAR GEOMÉTRICO DAS RAÍZES, (B) DIAGRAMAS DE BODE E (C) RESPOSTA AO DEGRAU.....      | 53 |

| FIGURA 29 SINAL DE REFERÊNCIA PARA UM CONVERSOR CC-CC.....                                                                                                                | 54 |

| FIGURA 30 SINAL DE REFERÊNCIA PARA UM CONVERSOR CC-CA.....                                                                                                                | 55 |

| FIGURA 31 SINAIS DE REFERÊNCIA PARA UM CONVERSOR CC-CA TRIFÁSICO.....                                                                                                     | 55 |

|                                                                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURA 32 GERAÇÃO DE SINAL MODULADO.....                                                                                                                                                                                                                                    | 56 |

| FIGURA 33 SINAL DE SAÍDA DO MODULADOR: CONVERSOR CC-CC.....                                                                                                                                                                                                                 | 56 |

| FIGURA 34 SINAL DE SAÍDA DO MODULADOR: CONVERSOR CC-CA.....                                                                                                                                                                                                                 | 57 |

| FIGURA 35 LÓGICA DE VARIAÇÃO DOS SINAIS DE GATILHO DOS INTERRUPTORES S1B E S4B DO CONVERSOR BOOST POR PWM.....                                                                                                                                                              | 58 |

| FIGURA 36 DIAGRAMA ESQUEMÁTICO DO CIRCUITO DE CONTROLE DO CONVERSOR BOOST POR PWM.....                                                                                                                                                                                      | 59 |

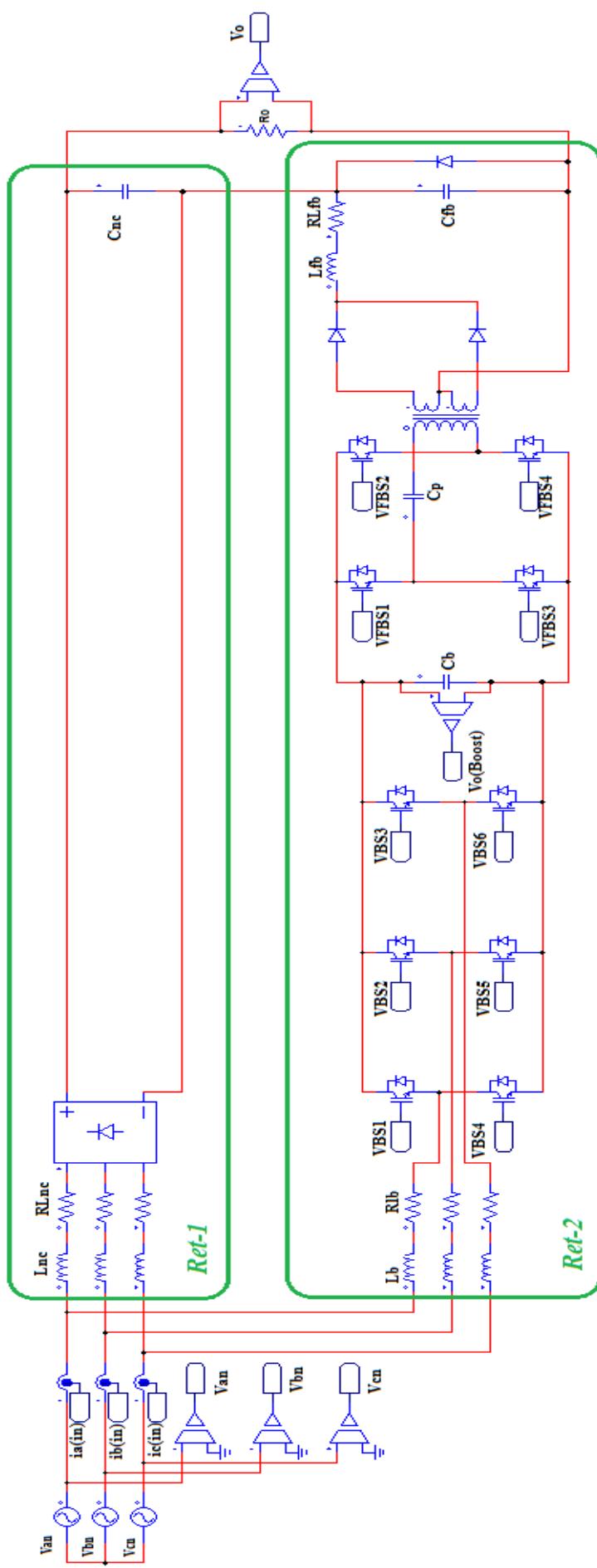

| FIGURA 37 DIAGRAMA ESQUEMÁTICO DE SIMULAÇÃO DO CIRCUITO DE POTÊNCIA DO RHT NO SOFTWARE PSIM®.....                                                                                                                                                                           | 62 |

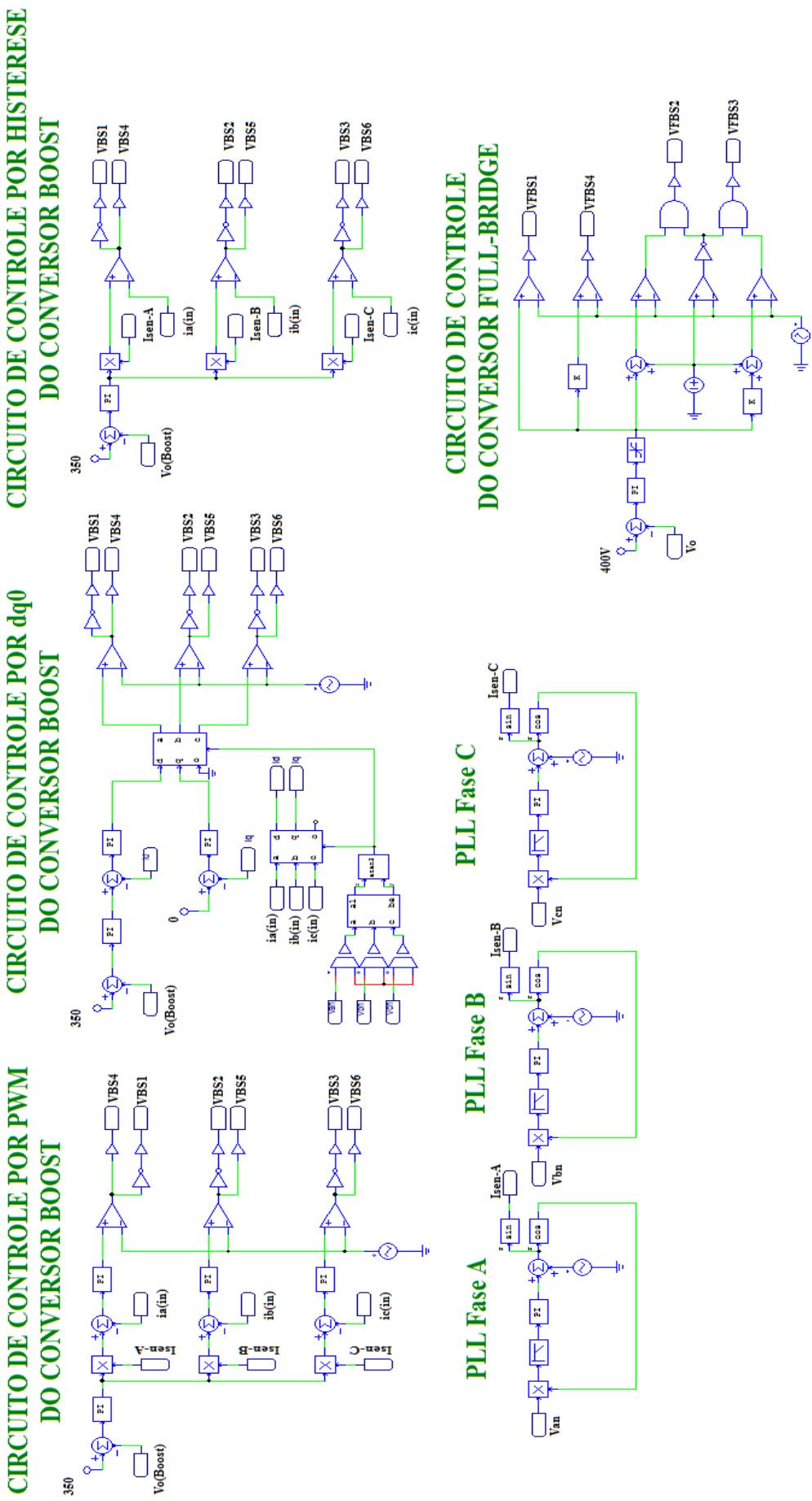

| FIGURA 38 - DIAGRAMA ESQUEMÁTICO DE SIMULAÇÃO NO SOFTWARE PSIM® DO CIRCUITO DE CONTROLE DO (A) CONVERSOR BOOST POR PWM, DQ0 E HISTERESE; (B) DO CONVERSOR FULL-BRIDGE; E (C) DOS PLLs.....                                                                                  | 63 |

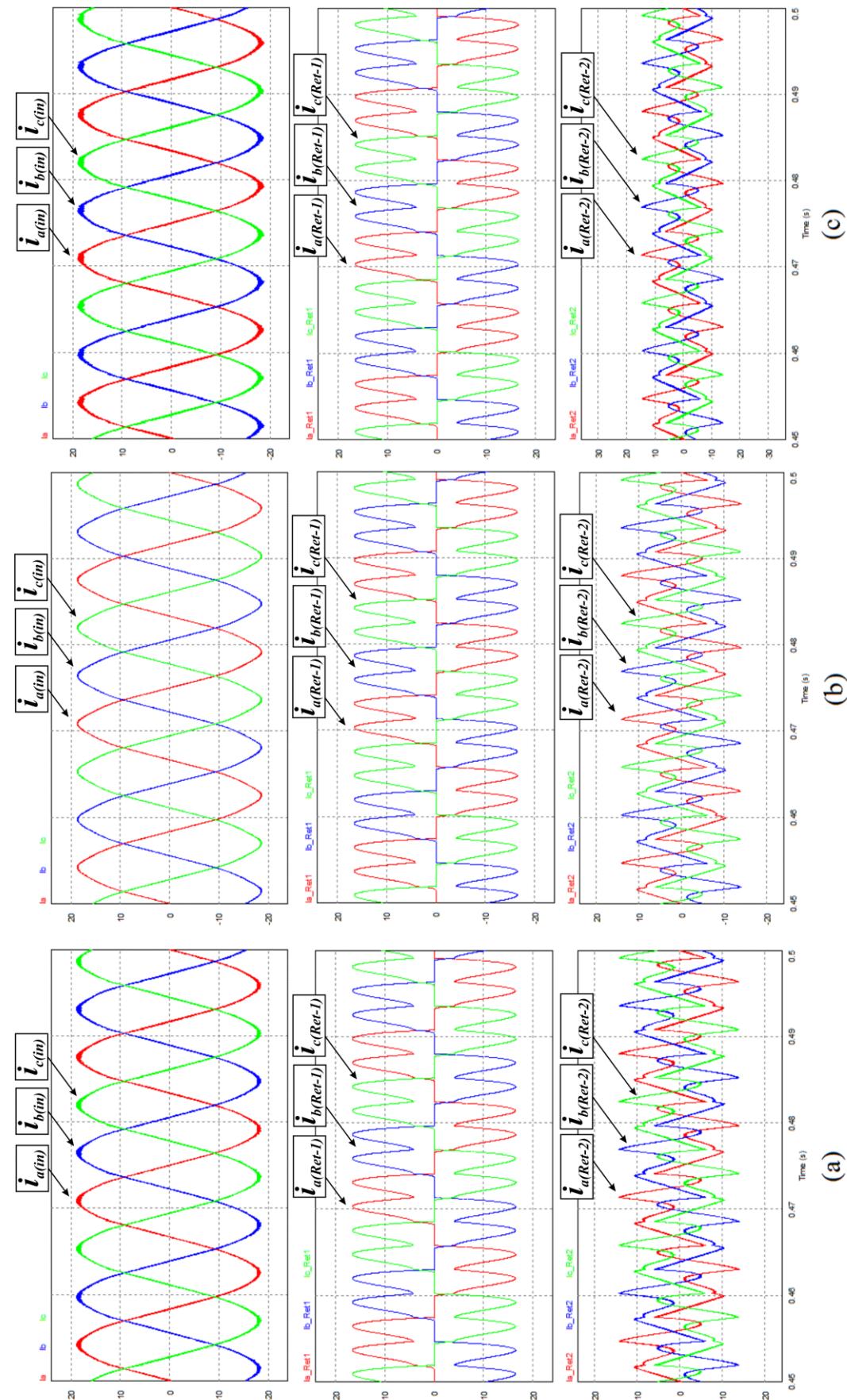

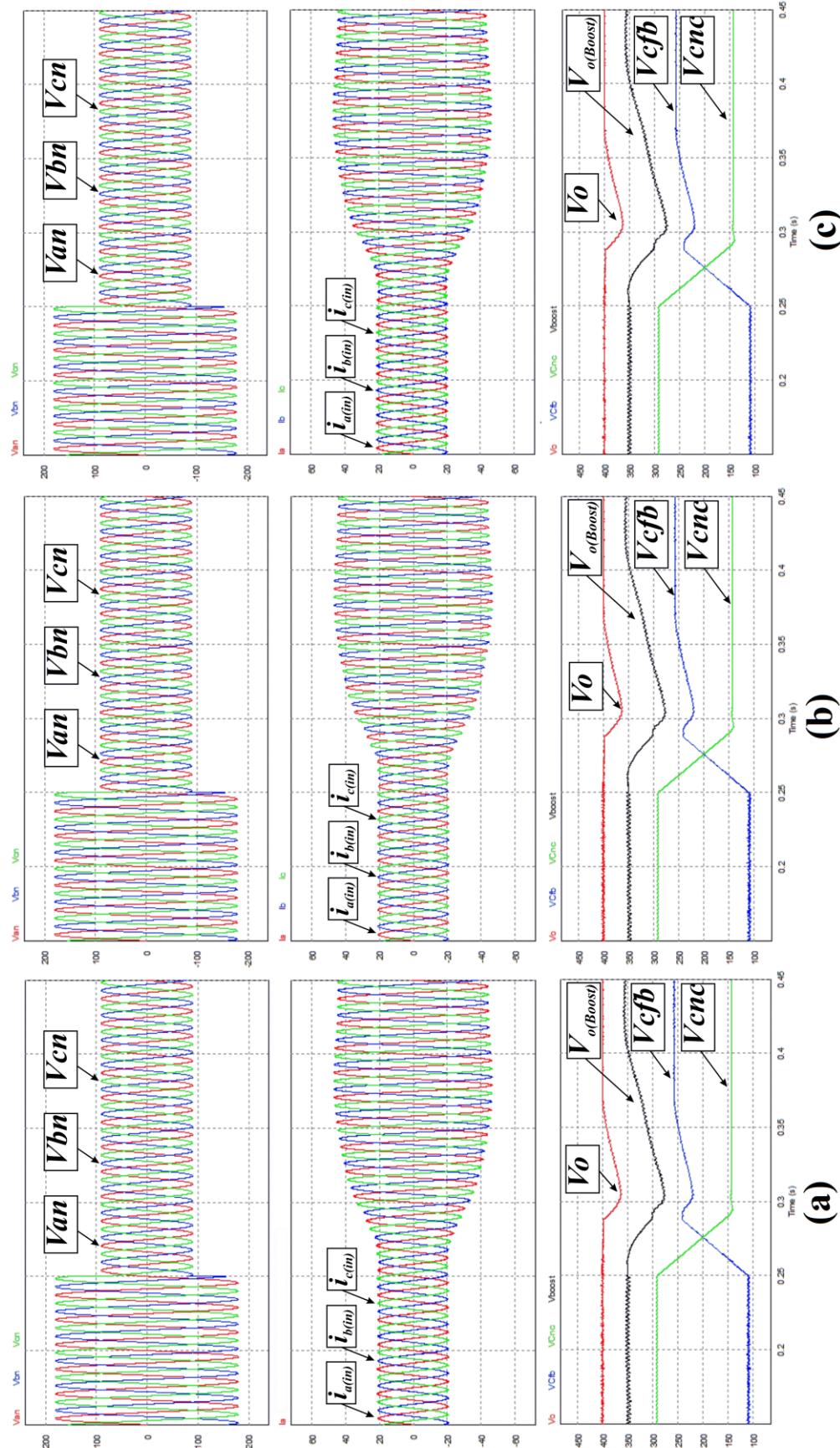

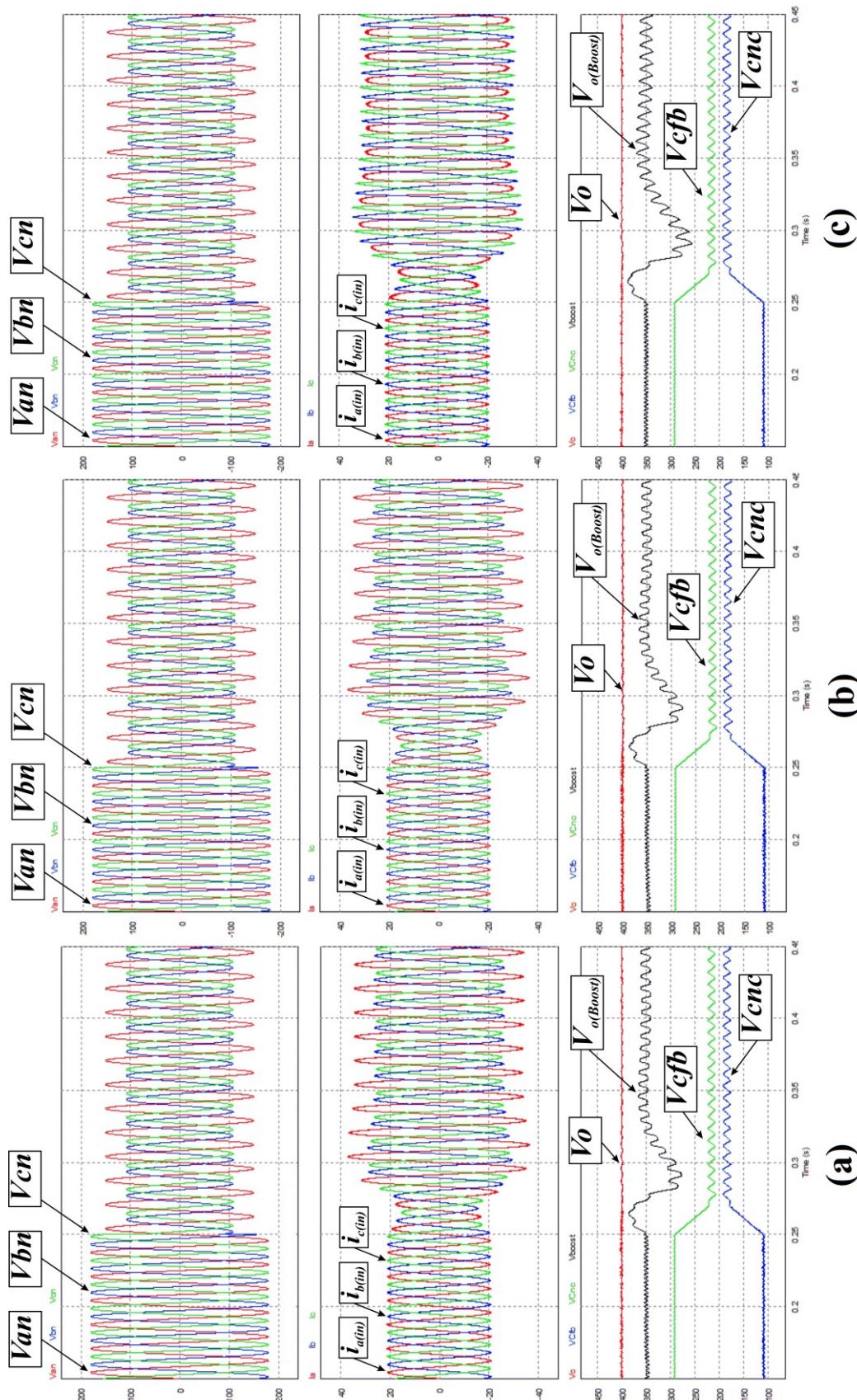

| FIGURA 39 - CORRENTES $I_{(IN)}$ , $I_{(RET-1)}$ E $I_{(RET-2)}$ PARA AS FASES A,B E C PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0.....                                                                                             | 65 |

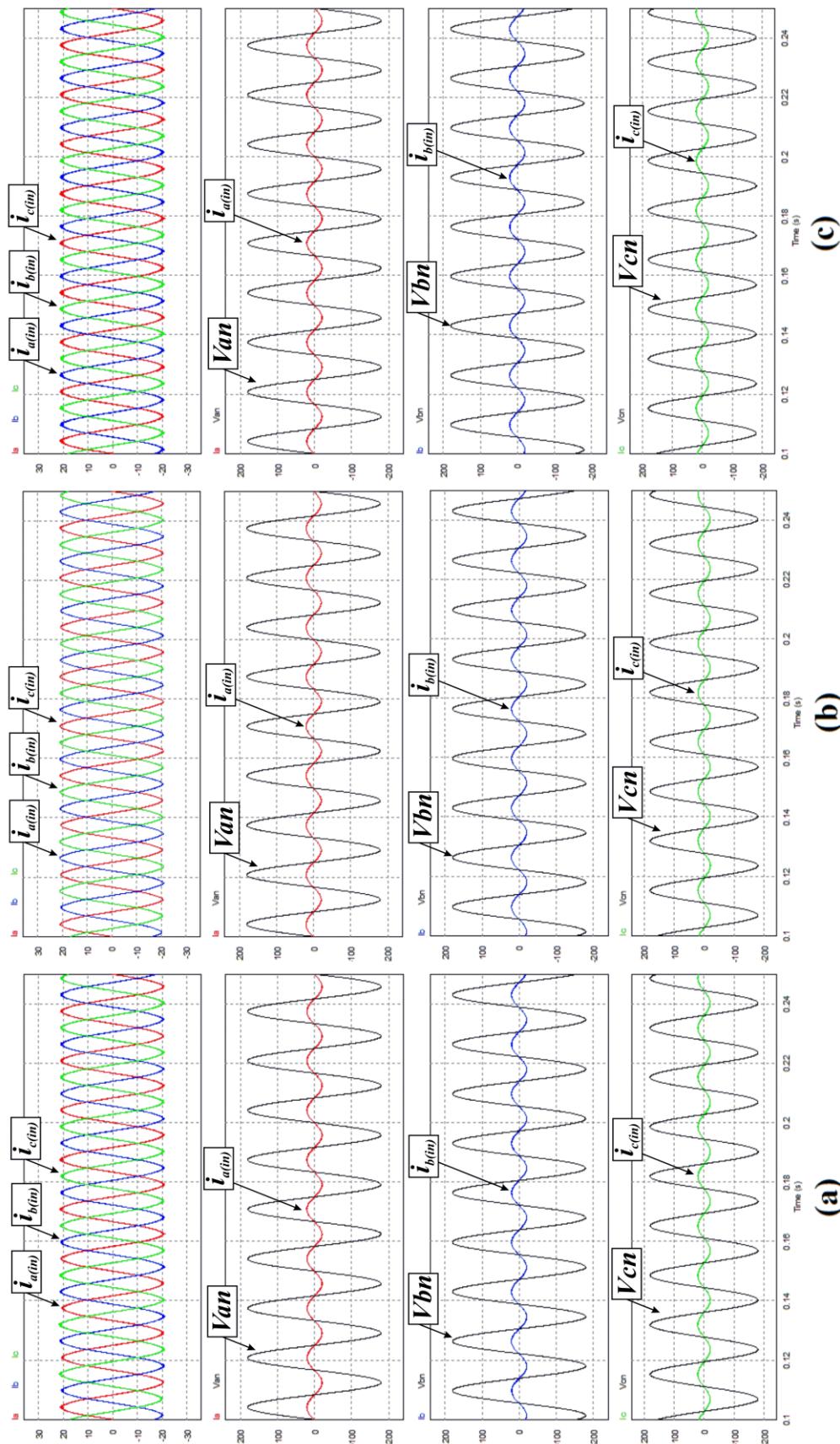

| FIGURA 40 - CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C E DEMONSTRAÇÃO DAS CORRENTES DE LINHA EM FASE COM AS TENSÕES F-N PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0.....                                                  | 66 |

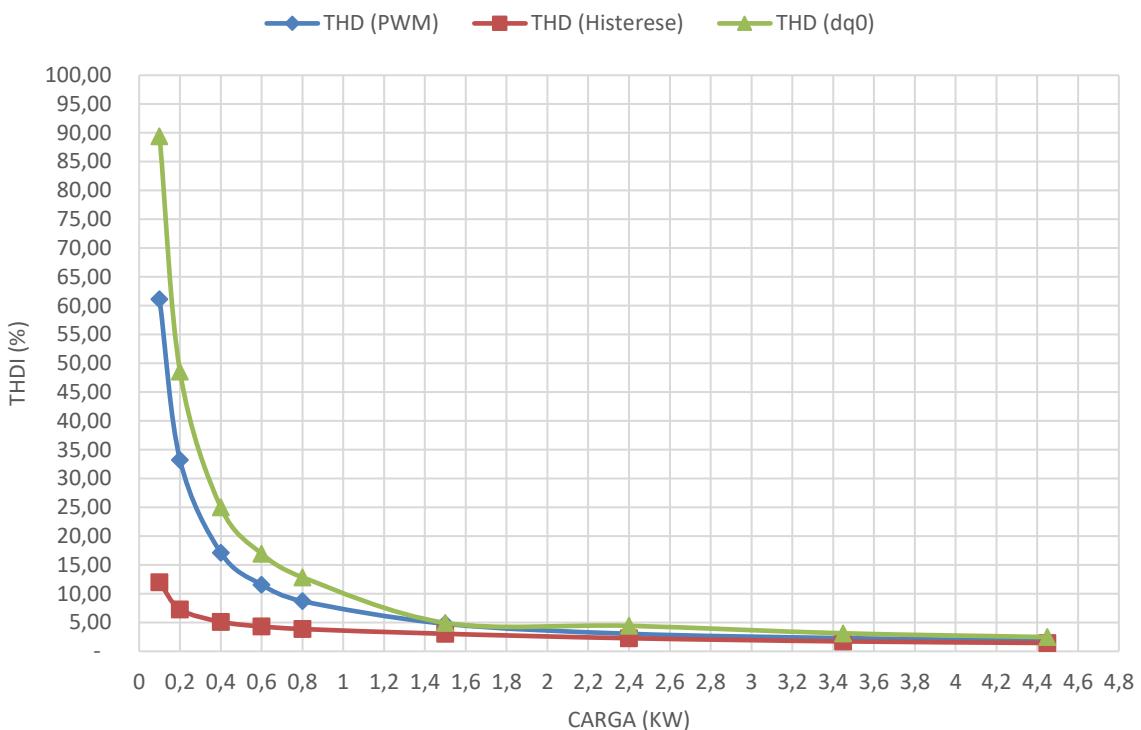

| FIGURA 41 GRÁFICO DE COMPARAÇÃO DA THD PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR PWM, HISTERESE E DQ0 QUANDO SUBMETIDOS A VÁRIOS VALORES DE CARGAS NO LINK CC.....                                                                                                 | 67 |

| FIGURA 42 GRÁFICO DE COMPARAÇÃO DO FP PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR PWM, HISTERESE E DQ0 QUANDO SUBMETIDOS A VÁRIOS VALORES DE CARGAS NO LINK CC.....                                                                                                  | 67 |

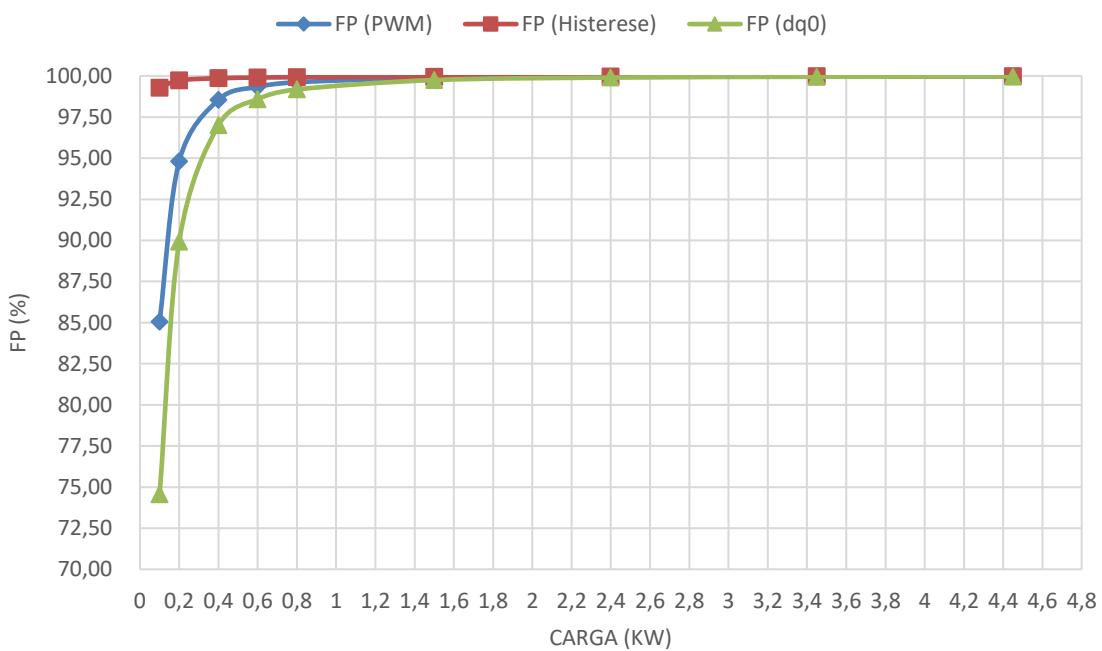

| FIGURA 43 TENSÃO NO BARRAMENTO CC ( $V_o$ ), TENSÃO DE SAÍDA DO CONVERSOR BOOST ( $V_o(BOOST)$ ), TENSÃO DE SAÍDA DE RET-1 ( $V_{CNC}$ ), E TENSÃO DE SAÍDA DE RET-2 ( $V_{CFB}$ ) PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0..... | 68 |

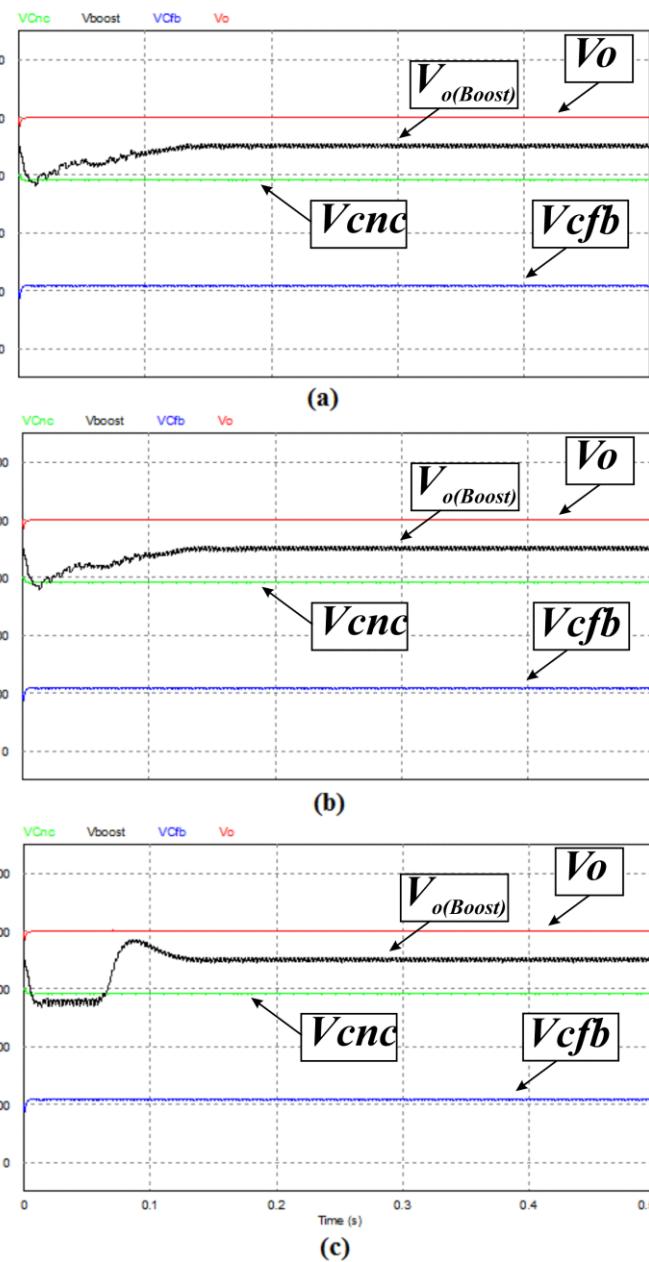

| FIGURA 44 RESPOSTA DINÂMICA DURANTE UM DEGRAU DE CARGA DE 2,5 kW PARA 5 kW PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0.....                                                                                                         | 69 |

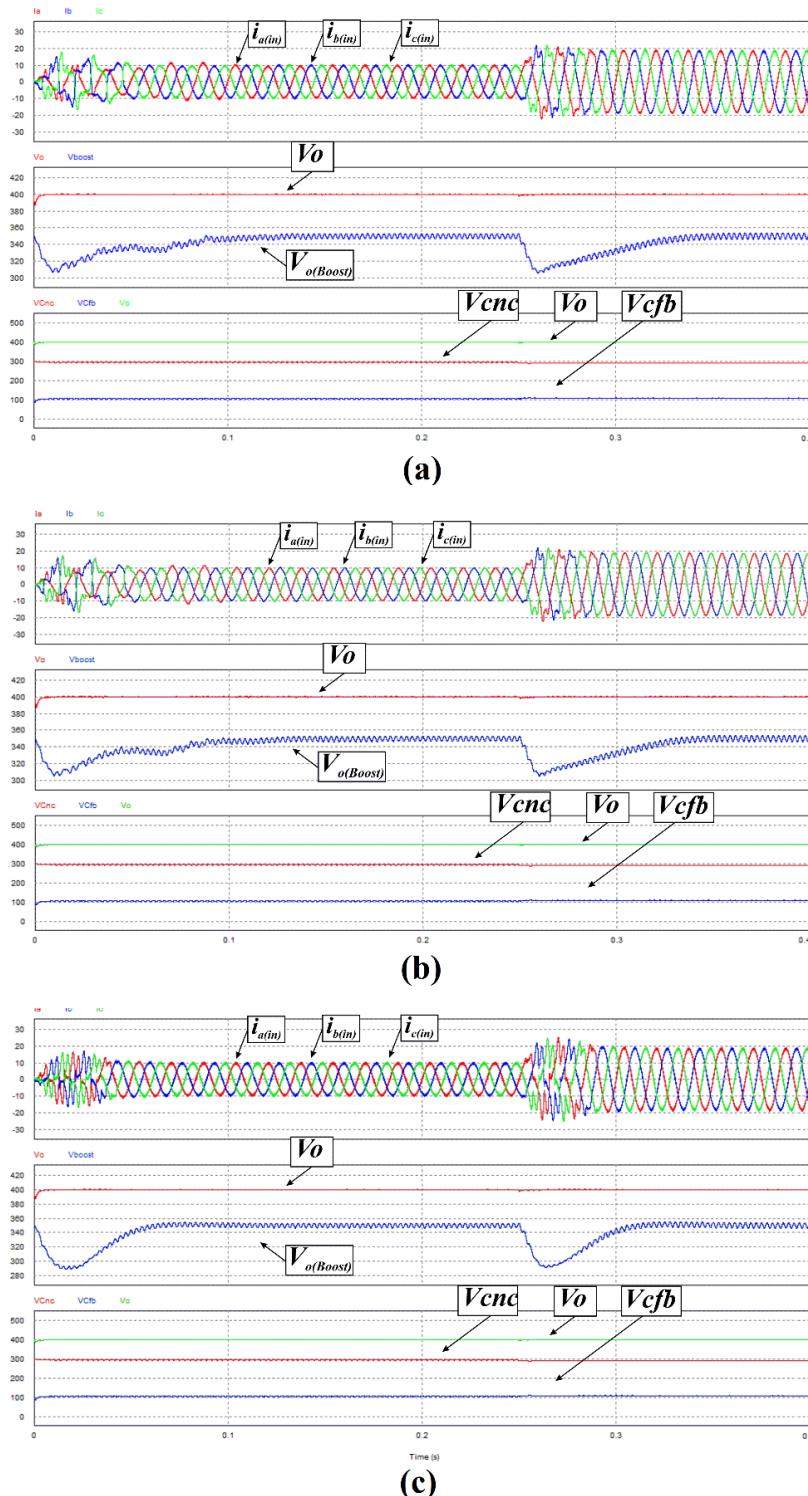

| FIGURA 45 - AFUNDAMENTO DO TIPO A: TENSÕES DE FASE; CORRENTES $I_A(IN)$ , $I_B(IN)$ E $I_C(IN)$ ; TENSÕES $V_o$ , $V_o(BOOST)$ , $V_{CNC}$ E $V_{CFB}$ DOS PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0.....                         | 72 |

| FIGURA 46 - AFUNDAMENTO DO TIPO G: TENSÕES DE FASE; CORRENTES $I_A(IN)$ , $I_B(IN)$ E $I_C(IN)$ ; TENSÕES $V_o$ , $V_o(BOOST)$ , $V_{CNC}$ E $V_{CFB}$ DOS PARA OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST POR (A) PWM, (B) HISTERESE E (C) DQ0.....                         | 73 |

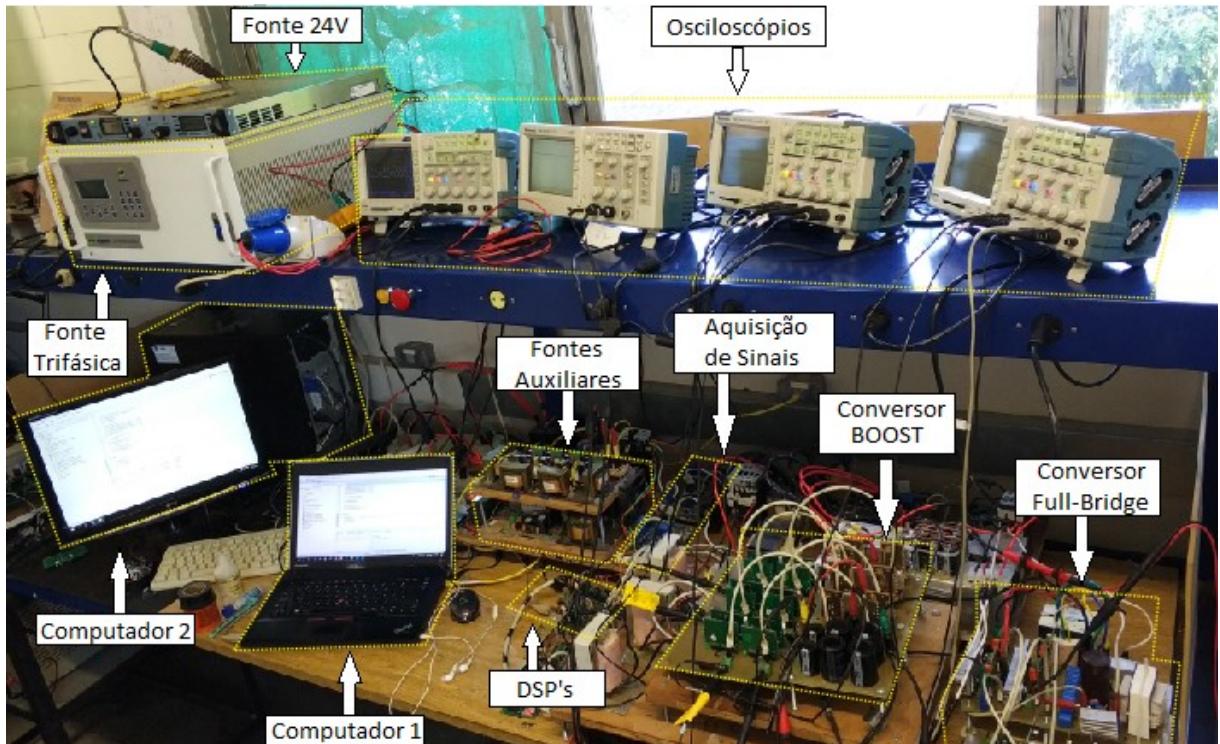

| FIGURA 47 PROTÓTIPO DO RETIFICADOR HÍBRIDO TRIFÁSICO DESENVOLVIDO EM LABORATÓRIO.....                                                                                                                                                                                       | 76 |

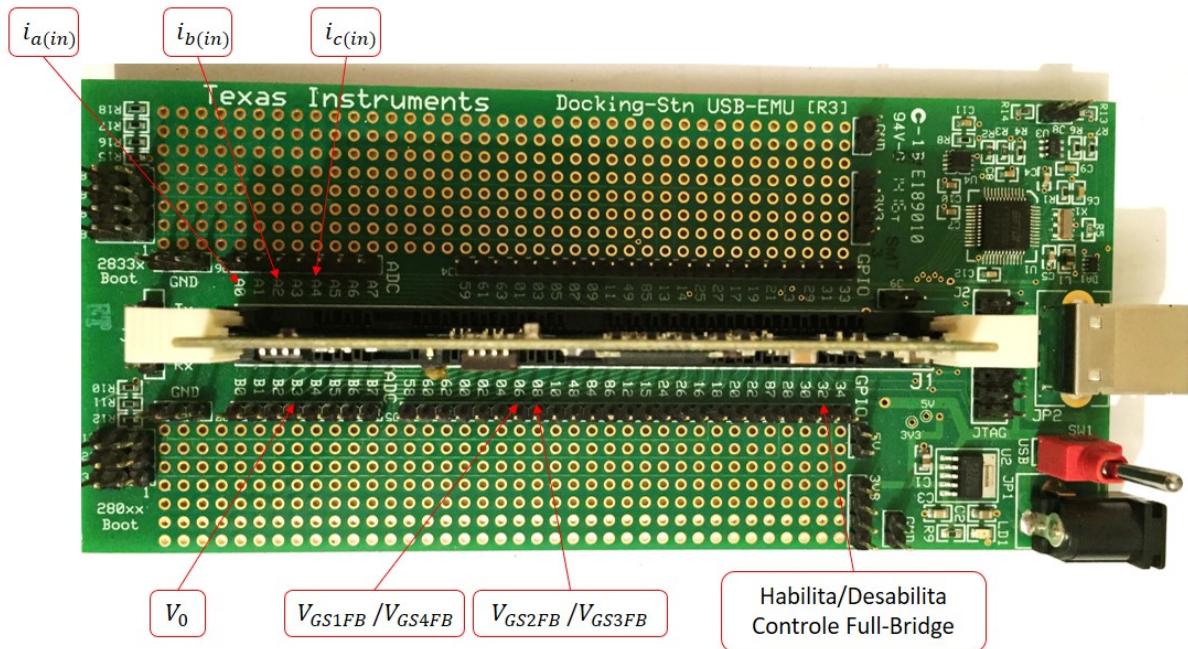

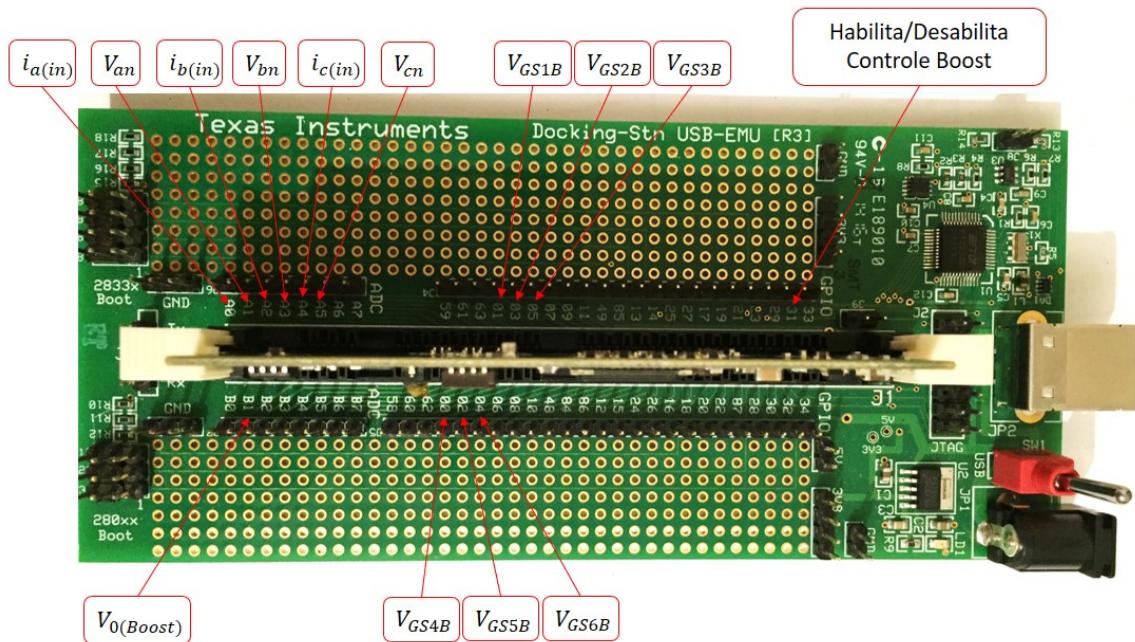

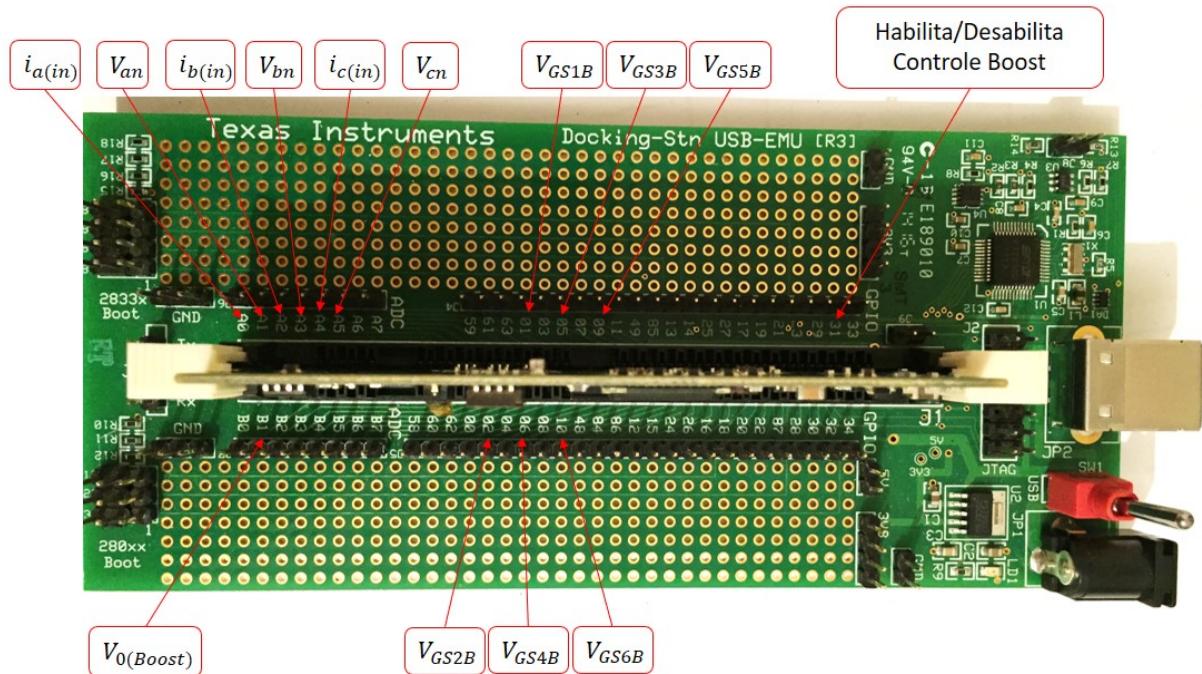

| FIGURA 48 ATRIBUIÇÕES DOS PINOS DE GPIO CONFIGURADOS NO ALGORITMO DE CONTROLE DO CONVERSOR FULL-BRIDGE EMBARCADO NO DSP.....                                                                                                                                                | 81 |

| FIGURA 49 ATRIBUIÇÕES DOS PINOS DE GPIO CONFIGURADOS NO ALGORITMO DE CONTROLE DO CONVERSOR BOOST CONTROLADO POR HISTERESE EMBARCADO NO DSP.....                                                                                                                             | 82 |

| FIGURA 50 ATRIBUIÇÕES DOS PINOS DE GPIO CONFIGURADOS NO ALGORITMO DE CONTROLE DO CONVERSOR BOOST CONTROLADO POR PWM E DQ0 EMBARCADO NO DSP.....                                                                                                                             | 83 |

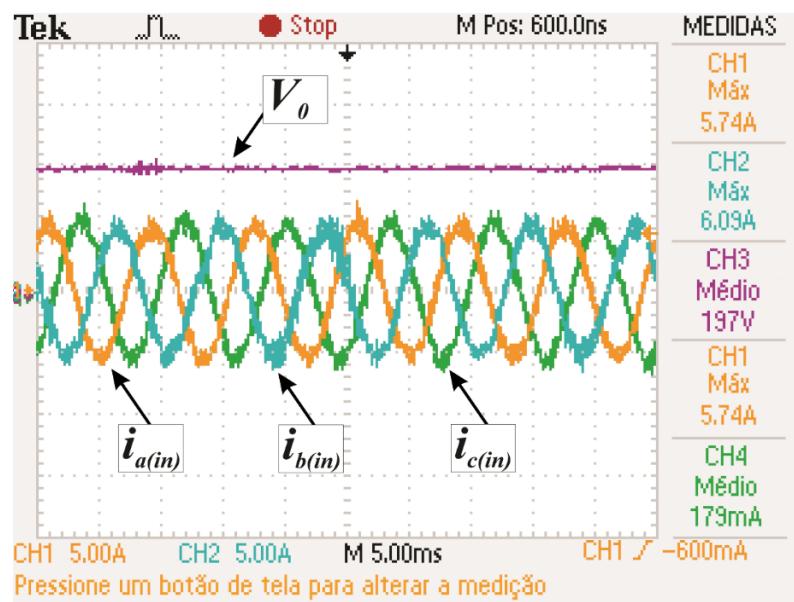

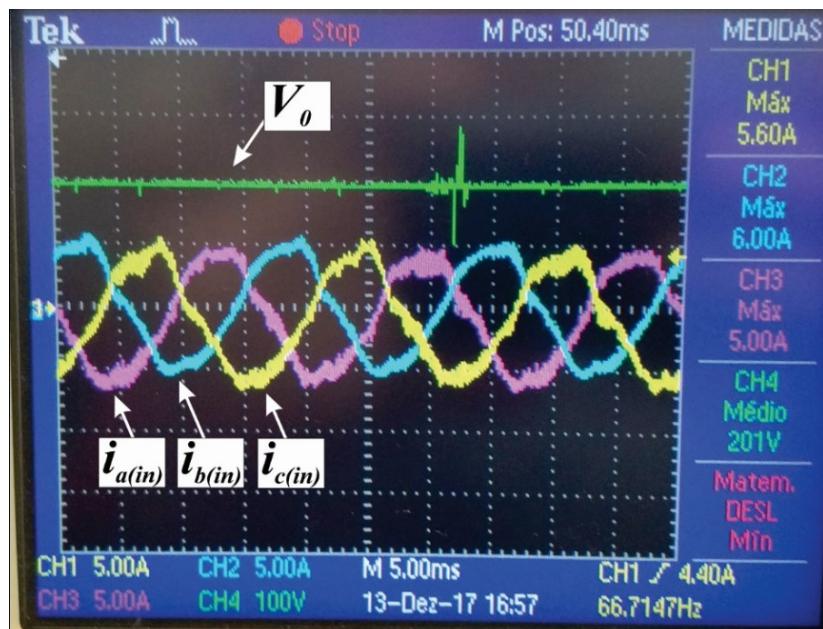

| FIGURA 51 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR HISTERESE OPERANDO COM CARGA DE 520 W.....                                                                                                                | 84 |

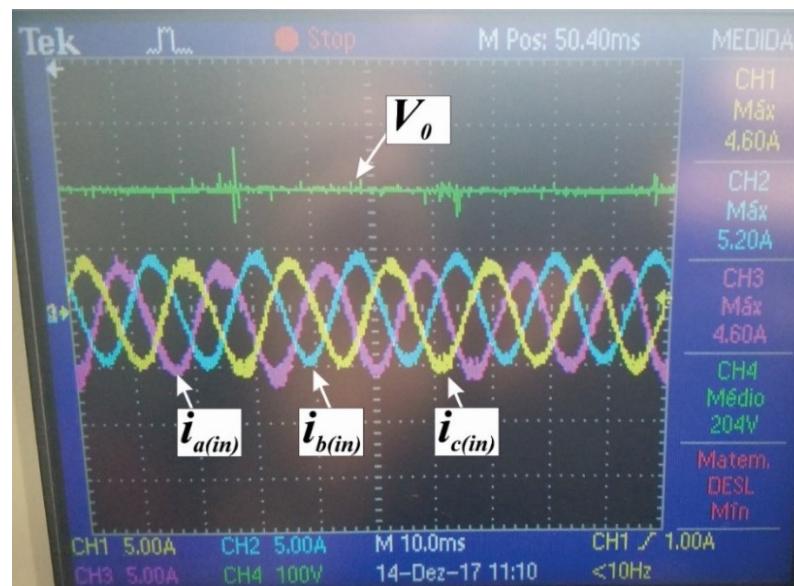

| FIGURA 52 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR PWM OPERANDO COM CARGA DE 520 W.....                                                                                                                      | 84 |

|                                                                                                                                                               |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

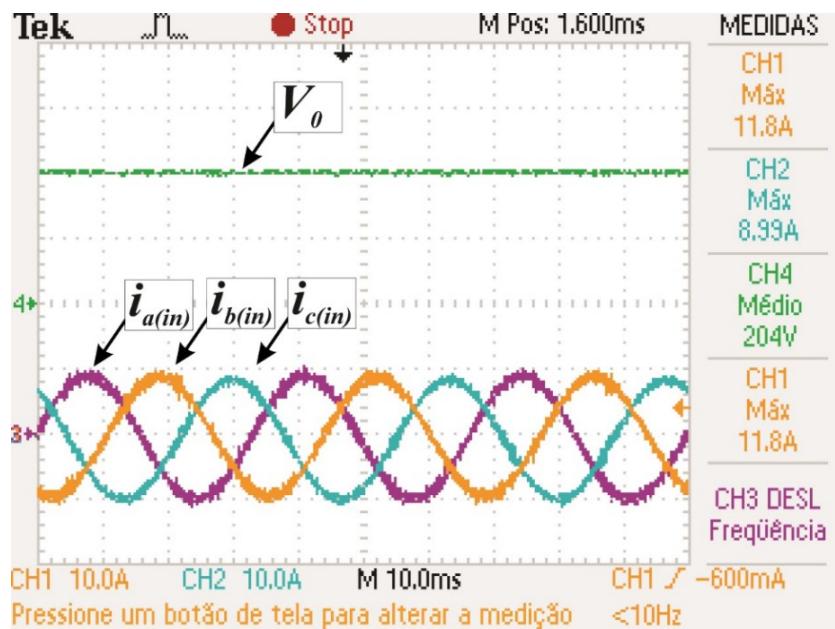

| FIGURA 53 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR DQ0 OPERANDO COM CARGA DE 520 W.....        | 85 |

| FIGURA 54 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR HISTERESE OPERANDO COM CARGA DE 1250 W..... | 85 |

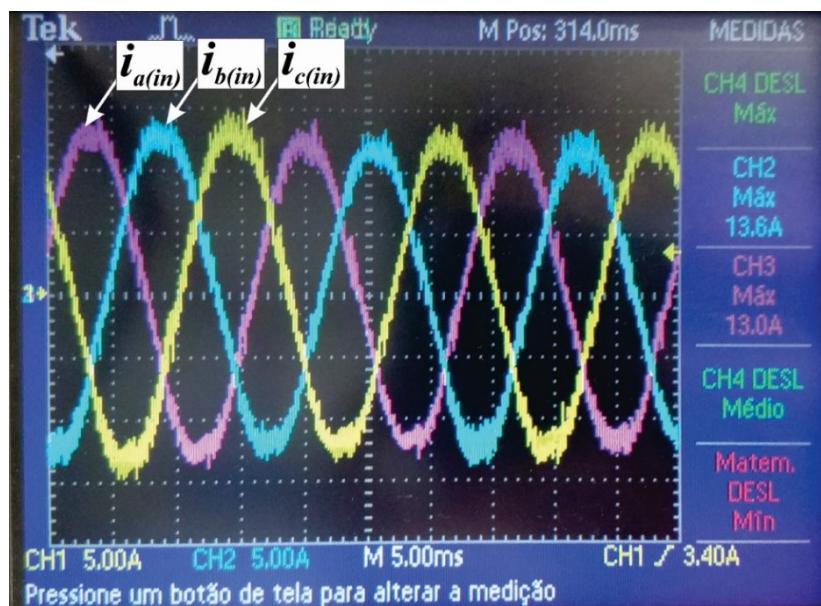

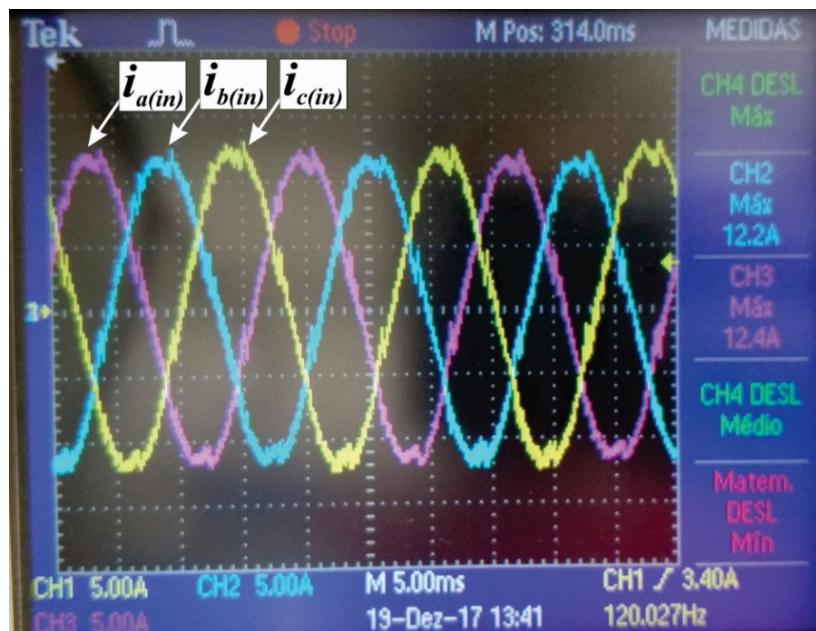

| FIGURA 55 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR PWM OPERANDO COM CARGA DE 1250 W.....       | 86 |

| FIGURA 56 TENSÃO DE SAÍDA DO RHT E CORRENTES DE LINHA DE ALIMENTAÇÃO DAS FASES A, B E C UTILIZANDO O CONTROLE POR DQ0 OPERANDO COM CARGA DE 1250 W.....       | 86 |

## **LISTA DE TABELAS**

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| TABELA 1 - COMPARATIVO ENTRE OS MÉTODOS DE CONTROLE DO CONVERSOR BOOST.....                                 | 60 |

| TABELA 2 - REPRESENTAÇÃO MATEMÁTICA PARA CADA AFUNDAMENTO DE TENSÃO.....                                    | 70 |

| TABELA 3 - ESPECIFICAÇÕES DO DSP TMS320F28335 DA TEXAS INSTRUMENTS®.....                                    | 77 |

| TABELA 4 - ESPECIFICAÇÕES DO MÓDULO PARA AQUISIÇÃO E CONDICIONAMENTO DE SINAIS DE CORRENTE E DE TENSÃO..... | 78 |

| TABELA 5 - ESPECIFICAÇÕES DO MÓDULO DE CONVERSÃO DOS SINAIS DE SAÍDA DO DSP DE 0 A 3,3 V PARA 0 A 15 V..... | 78 |

| TABELA 6 - ESPECIFICAÇÕES DO GATE-DRIVER DRO100S25A DA SUPPLIER®.....                                       | 78 |

| TABELA 7 - ESPECIFICAÇÕES DA FONTE TRIFÁSICA PROGRAMÁVEL FCATHQ 450-22-100 DA SUPPLIER®.....                | 79 |

# SIMBOLOGIA

$CA$  - Corrente alternada

$C_B$  - Capacitor de saída do conversor Boost

$CC$  - Corrente contínua

$C_{FB}$  - Capacitor de saída do conversor Full-Bridge

$C_{NC}$  - Capacitor de saída do retificador não controlado de seis pulsos

$d$  - Razão cíclica de operação do conversor Full-Bridge

$DHT$  - Distorção Harmônica Total

$DHTI$  - Distorção Harmônica Total de Corrente

$dq0'$  - Direct-Quadrature-Zero Transformation

$DSP$  - *Digital Signal Processor*

$DSP$  - Digital Signal Processor

$e_{v(B)}$  - Diferença entre a referência de tensão  $V_{o(Boost)*}$  e a tensão  $V_{o(Boost)}$

$e_{v(FB)}$  - Diferença entre a referência de tensão  $V_o*$  e a tensão  $V_o$

$f$  - Frequência da rede (60 Hz)

$f$  – Frequência da Rede (60 Hz)

$f_{ch}$  - Frequência de chaveamento

FEELT - Faculdade de Engenharia Elétrica

$f_R$  - Frequência de ressonância

$f^s$  – Frequência de Chaveamento

$f\alpha$  – Frequência de Amostragem

$i_{a(in)}$  - Corrente de linha de entrada da fase A

$i_{a(Ret-1)}$  - Corrente drenada pela fase A de Ret-1

$i_{a(Ret-2)}$  - Corrente drenada pela fase A de Ret-2

$i_{b(in)}$  - Corrente de linha de entrada da fase B

$i_{b(Ret-1)}$  - Corrente drenada pela fase B de Ret-1

$i_{b(Ret-2)}$  - Corrente drenada pela fase B de Ret-2

$i_{c(in)}$  - Corrente de linha de entrada da fase C

$i_{c(Ret-1)}$  - Corrente drenada pela fase C de Ret-1

$i_{c(Ret-2)}$  - Corrente drenada pela fase C de Ret-2

$i_{Cfb}$  - Corrente no capacitor  $C_{FB}$

*IEC - International Electrotechnical Commission*

IGBT's – Insulated gate bipolar transistor

$i_{Ref-A}$  - Referência senoidal de corrente da fase A

$i_{Ref-B}$  - Referência senoidal de corrente da fase B

$i_{Ref-C}$  - Referência senoidal de corrente da fase C

$I_{RMS}$  - Valor eficaz das correntes de entrada

$i_{sen-A^*}$  - Referência senoidal gerada pelo PLL da fase A

$i_{sen-B^*}$  - Referência senoidal gerada pelo PLL da fase B

$i_{sen-C^*}$  - Referência senoidal gerada pelo PLL da fase C

$K$  - Ganho da função de transferência de primeira ordem

$L_B$  - Indutor de entrada do conversor Boost

$L_{FB}$  - Indutor do conversor Full-Bridge

MOSFET's – Transistor de Efeito de Campo de Metal-Óxido Semicondutor

NUPEP - Núcleo de Pesquisas em Eletrônica de Potência

PI - Proporcional Integral

PID - Proporcional Integral Derivativo

*PLL - Phase Locked Loop*

$P_o$  - Potência ativa total de saída

$P_{o(Ret-1)}$  - Potência ativa processada pela estrutura Ret-1

$P_{o(Ret-2)}$  - Potência ativa processada pela estrutura Ret-2

PWM – Modulação por Largura de Pulso

*PWM - Pulse Width Modulation*

*Ret-1* - Estrutura retificadora 1 do RHT

Ret-1 - Retificador Trifásico Não Controlado de Seis Pulsos

Ret-2 - Conversores Chaveados (SEPIC)

*Ret-2* - Estrutura retificadora 2 do RHT

$R_{FB}$  - Resistência de carga equivalente à operação do conversor Full-Bridge

*RHT* - Retificador híbrido trifásico

*RHT* - Retificador Híbrido Trifásico

*RNC* - Retificador não controlador

$S_{IB\dots 6B}$  - Interruptores do conversor Boost

$S_{IFB\dots 4FB}$  - Interruptores do conversor Full-Bridge

SVPWM - Modulação por Largura de Pulso no Espaço Vetorial

THDi - Distorção Harmônica de Corrente

$u$  - Vetor de entrada

UFU - Universidade Federal de Uberlândia

$u_{v(B)}$  - Saída do controlador de tensão do conversor Boost

$u_{v(FB)}$  - Saída do controlador de tensão do conversor Full-Bridge

$u_{v(sat)}$  - Saída saturada do controlador de tensão do conversor Full-Bridge

V – Volts, unidade de tensão elétrica

$v_0$  – Tensão de Saída

$v_{ab}$  - Tensão entre as fases A e B

$v_{ac}$  - Tensão entre as fases A e C

$v_{an}$  - Tensão entre a fase A e o neutro

$v_{ba}$  - Tensão entre as fases B e A

$v_{bc}$  - Tensão entre as fases B e C

$v_{bn}$  - Tensão entre a fase B e o neutro

$v_{ca}$  - Tensão entre as fases C e A

$v_{cb}$  - Tensão entre as fases C e B

$V_{CC}$  - Nível CC de tensão somada à onda dente de serra para utilização no PLL

$V_{GS1B}$  - Sinal de gatilho enviado para a chave  $S_{1B}$

$V_{GS1FB}$  - Sinal de gatilho enviado para a chave  $S_{1FB}$

$V_{GS2B}$  - Sinal de gatilho enviado para a chave  $S_{2B}$

$V_{GS2FB}$  - Sinal de gatilho enviado para a chave  $S_{2FB}$

$V_{GS3B}$  - Sinal de gatilho enviado para a chave  $S_{3B}$

$V_{GS3FB}$  - Sinal de gatilho enviado para a chave  $S_{3FB}$

$V_{GS4B}$  - Sinal de gatilho enviado para a chave  $S_{4B}$

$V_{GS4FB}$  - Sinal de gatilho enviado para a chave  $S_{4FB}$

$V_{GS5B}$  - Sinal de gatilho enviado para a chave  $S_{5B}$

$V_{GS6B}$  - Sinal de gatilho enviado para a chave  $S_{6B}$

$V_{o(Boost)}$  – Tensão de saída do Conversor Boost

Vref – Tensão de referência

$ZOH$  - Zero-Order Hold

$\omega$  - Frequência angular

# SUMÁRIO

|                                                                                                     |           |

|-----------------------------------------------------------------------------------------------------|-----------|

| <b>CAPÍTULO I .....</b>                                                                             | <b>20</b> |

| <b>1 INTRODUÇÃO GERAL.....</b>                                                                      | <b>20</b> |

| <b>1.1 Introdução .....</b>                                                                         | <b>20</b> |

| 1.1.1 <i>Modulação por Largura de Pulso (PWM) .....</i>                                             | 22        |

| 1.1.2 <i>Modulação por Largura de Pulso no Espaço Vetorial (SVPWM).....</i>                         | 23        |

| 1.1.3 <i>Modulação por Histerese.....</i>                                                           | 24        |

| <b>1.2 Contribuições da Dissertação .....</b>                                                       | <b>24</b> |

| <b>1.3 Objetivo da Dissertacão .....</b>                                                            | <b>27</b> |

| <b>1.4 Estrutura da Dissertação .....</b>                                                           | <b>27</b> |

| <b>CAPÍTULO II.....</b>                                                                             | <b>28</b> |

| <b>2 ESTRATÉGIAS DE CONTROLE DO RETIFICADOR HÍBRIDO TRIFÁSICO .....</b>                             | <b>28</b> |

| <b>2.1 Considerações Iniciais.....</b>                                                              | <b>28</b> |

| <b>2.2 Estratégia de Controle do Conversor Full-Bridge .....</b>                                    | <b>28</b> |

| <b>2.3 Estratégia de Controle do Conversor Boost.....</b>                                           | <b>30</b> |

| 2.3.1 <i>Controle do Conversor Boost pela Transformada dq0.....</i>                                 | 30        |

| A. Princípio de Funcionamento do Controle por dq0 implementado .....                                | 34        |

| B. Projeto do controlador de Corrente .....                                                         | 39        |

| C. Projeto do controlador de Tensão .....                                                           | 39        |

| D. Conclusões referente ao Contole por Transformada dq0.....                                        | 40        |

| 2.3.2 <i>Controle do Conversor Boost por Histerese .....</i>                                        | 41        |

| A. Princípio de Funcionamento do Controle por Histerese Implementado .....                          | 43        |

| B. Princípio de Funcionamento do PLL.....                                                           | 45        |

| C. Projeto dos Controladores.....                                                                   | 47        |

| D. Conclusões referente ao Contole por Histerese .....                                              | 54        |

| 2.3.3 <i>Controle do Conversor Boost por PWM .....</i>                                              | 54        |

| <b>2.4 Comparação Entre as Estratégias de Controle do Conversor Boost.....</b>                      | <b>59</b> |

| <b>CAPÍTULO III .....</b>                                                                           | <b>61</b> |

| <b>3 RESULTADOS DE SIMULAÇÃO COMPUTACIONAL.....</b>                                                 | <b>61</b> |

| <b>3.1 Considerações Iniciais .....</b>                                                             | <b>61</b> |

| <b>3.2 Esquemático de Simulação .....</b>                                                           | <b>61</b> |

| <b>3.3 Resultados de Simulação do RHT sob Condições Normais de Suprimento da Rede Elétrica.....</b> | <b>64</b> |

| <b>3.4 Resultados de Simulação do RHT sob Condições de Afundamentos de Tensão .....</b>             | <b>70</b> |

| <b>3.5 Considerações finais .....</b>                                                               | <b>74</b> |

| <b>CAPÍTULO IV .....</b>                                                                            | <b>76</b> |

| <b>4 RESULTADOS EXPERIMENTAIS.....</b>                                                              | <b>76</b> |

|                                                                                                                                   |            |

|-----------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>4.1 Protótipo Experimental .....</b>                                                                                           | <b>76</b>  |

| <b>4.2 Implementação dos Algoritmos de Controle.....</b>                                                                          | <b>79</b>  |

| 4.2.1 <i>Estratégia de Controle do Computador 2 – Conversor Full-Bridge .....</i>                                                 | <i>80</i>  |

| 4.2.2 <i>Estratégia de Controle do Computador 1 – Conversor Boost .....</i>                                                       | <i>81</i>  |

| A. Configurações de Hardware do Conversor Boost por Histerese.....                                                                | 82         |

| B. Configurações de Hardware do Conversor Boost por PWM e dq0 .....                                                               | 82         |

| <b>4.3 Resultados Experimentais do RHT Operando com Potência de 520 W .....</b>                                                   | <b>83</b>  |

| <b>4.4 Resultados Experimentais do RHT Operando com Potência de 1250 W .....</b>                                                  | <b>85</b>  |

| <b>4.5 Considerações finais .....</b>                                                                                             | <b>86</b>  |

| <b>CAPÍTULO V .....</b>                                                                                                           | <b>88</b>  |

| <b>5 CONCLUSÕES.....</b>                                                                                                          | <b>88</b>  |

| <b>CAPÍTULO VI .....</b>                                                                                                          | <b>90</b>  |

| <b>6 REFERÊNCIAS BIBLIOGRÁFICAS .....</b>                                                                                         | <b>90</b>  |

| <b>APÊNDICE A – CÓDIGO DE CONTROLE DO RHT EMBARCADO NO DPS TMS320F28335 PARA<br/>CONTROLE DO CONVERSOR FULL-BRIDGE .....</b>      | <b>95</b>  |

| <b>APÊNDICE B – CÓDIGO DE CONTROLE DO RHT EMBARCADO NO DPS TMS320F28335 PARA<br/>CONTROLE DO CONVERSOR BOOST – PWM .....</b>      | <b>98</b>  |

| <b>APÊNDICE C – CÓDIGO DE CONTROLE DO RHT EMBARCADO NO DPS TMS320F28335 PARA<br/>CONTROLE DO CONVERSOR BOOST – HISTERESE.....</b> | <b>106</b> |

| <b>APÊNDICE D – CÓDIGO DE CONTROLE DO RHT EMBARCADO NO DPS TMS320F28335 PARA<br/>CONTROLE DO CONVERSOR BOOST – DQ0 .....</b>      | <b>114</b> |

# CAPÍTULO I

## 1 Introdução Geral

---

### 1.1 Introdução

A efetiva utilização das fontes de energia alternativa de pequeno porte exige, na grande maioria dos casos, a utilização de conversores de potência dedicados. Tais equipamentos visam tornar a energia gerada adequada para o suprimento de cargas elétricas convencionais e chaveadas, permitir a interligação com diferentes fontes de energia e dispositivos de armazenagem, além da conexão com a rede pública [1]-[4]. Além destes motivos, a utilização de conversores de potência é necessária para entregar a energia com qualidade aceitável do ponto de vista da carga, com reduzido conteúdo harmônico e com amplitude e frequência da tensão compatíveis [5].

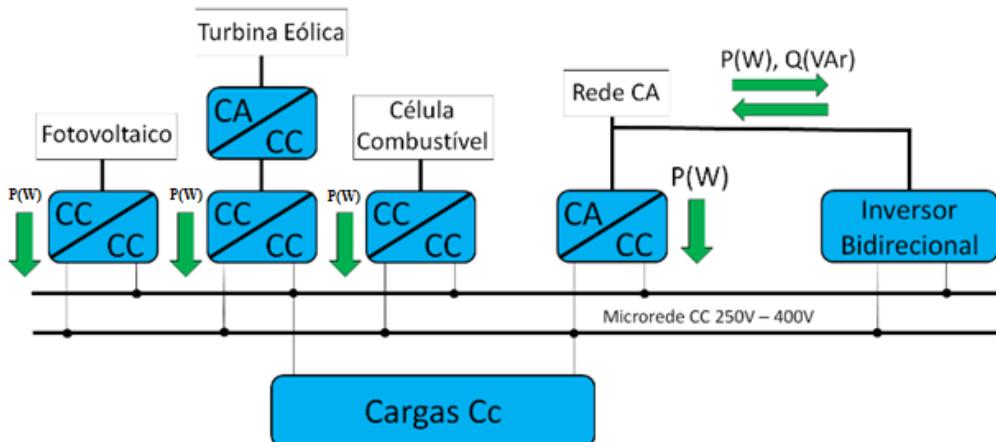

Conversores CA-CC são comumente utilizados para fazer interface entre a rede CA de alimentação e o barramento CC onde estão conectadas as cargas e fontes renováveis de energia que compõem a microrrede, como retratada na Figura 1 são utilizados para a injeção de potência no barramento CC a partir da rede CA, em condições onde a energia gerada pelos centros de microgeração não é suficiente para suprir as cargas da microrrede [2]-[9]. Em condição de excedente de energia no barramento CC, uma parcela dessa energia pode ser injetada na rede CA de alimentação por meio de conversores CC-CA [10]-[14], ou confinada em sistemas de armazenamento de energia através da utilização de conversores CC-CC, que por sua vez servem também para converter a tensão do barramento CC em diferentes níveis de tensão, utilizados pelas distintas cargas presentes na microrrede.

É importante destacar que quando há a interface de conexão entre a rede CA fornecida pela concessionária de energia elétrica e a microrrede, perturbações da rede CA de alimentação, como afundamentos temporários de tensão e interrupções de suprimento da energia elétrica, podem afetar o sistema de distribuição CC presente na microrrede, provocando circulação de correntes de alta magnitude, ao longo dos alimentadores que interligam o serviço público de distribuição CA à microrrede [15].

Figura 1 Diagrama esquemático de uma microrrede CC.

Fonte: (RODRIGUES, 2016).

Pesquisas em torno de conversores CA-CC e estruturas retificadoras híbridas (integração entre retificadores passivos e conversores chaveados) têm despertado o interesse por parte da comunidade científica no sentido de desenvolver métodos de controle destas estruturas para promover a regulação da tensão no barramento CC e fornecer à rede das concessionárias correntes com baixo conteúdo harmônico e elevado fator de potência.

Tais estratégias de controle, aplicadas na geração dos pulsos de gatilho para os dispositivos de chaveamento, são consideradas como sendo o núcleo dos conversores. Basicamente, são executadas em três partes. A primeira corresponde à aquisição dos sinais essenciais de tensão e de corrente, usados para alimentar os processadores que executam o algoritmo de controle. A segunda corresponde à geração dos sinais de referência que o conversor irá seguir. A terceira é a geração dos pulsos de gatilho para os dispositivos de chaveamento.

Em conversores CA-CC operando apenas na alimentação de cargas com corrente contínua, duas variáveis são controladas, a corrente de entrada ( $i_{fase}$ ) e a tensão no barramento CC ( $v_0$ ). A corrente de entrada deve estar em fase com a tensão na entrada para garantir o fator de potência unitário, além disso, deverá apresentar o mínimo de distorção harmônica possível. A tensão no barramento CC deve ser constante e com a mínima ondulação possível. Estas três características são os objetivos de controle dos retificadores ativos.

O objetivo de controle da maioria das estratégias encontradas na literatura é que a corrente de entrada seja uma réplica da tensão de entrada, pois a grande preocupação nos projetos de controladores é manter o fator de potência unitário. Porém deve também haver uma preocupação quanto à forma de onda da tensão de entrada, pois se a mesma apresentar distorção, a corrente controlada também será distorcida [16].

---

A primeira parte da estratégia de controle de um conversor corresponde à aquisição dos sinais essenciais de tensão e corrente. Os sinais adquiridos geralmente são a tensão CA, as correntes de entrada e a tensão no barramento CC do conversor. Nesta etapa os sinais adquiridos pelos sensores são digitalizados e usados na realização das etapas de cálculo.

A segunda parte da estratégia é a execução do algoritmo de controle. Nesta etapa são realizados os cálculos necessários para o correto funcionamento do conversor, como também a regulação das variáveis do sistema. Vários tipos de controladores são empregados na etapa do controle dos conversores, como controladores PI (Proporcional Integral) e PID (Proporcional Integral Derivativo) por possuírem rápida resposta dinâmica e ao mesmo tempo manter a estabilidade do sistema conversor. A saída desta etapa do controle geralmente é o sinal de referência, tensão ou corrente, que deverá ser utilizado para gerar os pulsos de gatilho dos dispositivos de chaveamento.

No caso de retificadores, a referência é geralmente um sinal senoidal que o retificador deverá seguir de acordo com o chaveamento dos seus IGBT's ou MOSFET's. A maioria das estratégias de controle aplicadas exigem transformações matemáticas complexas e um número elevado de variáveis a serem medidas. Dentre os métodos existentes, o modo de controle de corrente é usado em conversores pela necessidade de geração de uma referência de corrente a ser seguida pelo conversor [17].

A terceira parte da estratégia de controle é justamente a geração dos sinais de gatilho para os dispositivos de estado sólido que compõem o conversor. Os sinais de tensão e corrente adquiridos e a corrente de referência servem de alimentação para este estágio do controlador, o qual tem como saída os pulsos para cada chave, que determinam o tempo que cada chave deverá ficar fechada. Na literatura, as técnicas de geração dos pulsos de gatilho mais conhecidas para retificadores são a modulação por largura de Pulso (PWM), Modulação por Largura de Pulso no Espaço Vetorial (SVPWM) e Histerese.

### 1.1.1 Modulação por Largura de Pulso (PWM)

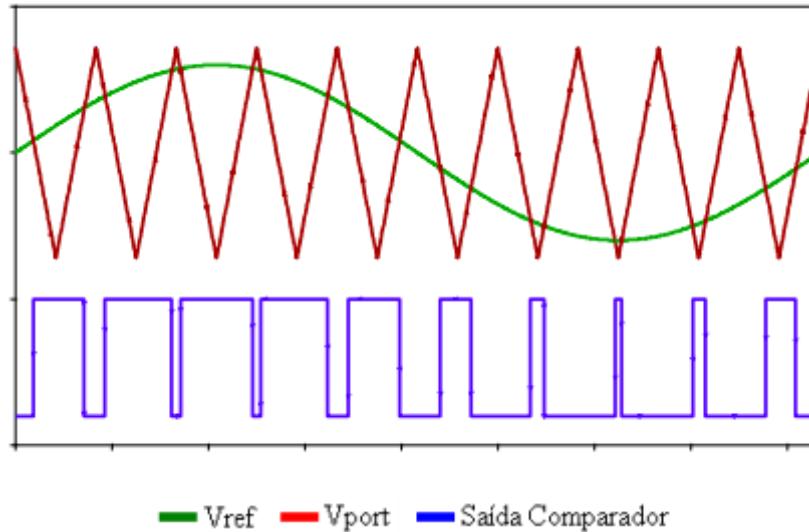

Esta técnica consiste na comparação de dois sinais de tensão, um de baixa frequência (referência) e o outro de alta frequência (portadora), resultando em um sinal alternado com frequência fixa e largura de pulso variável, assim como demonstrado na Figura 2 [16].

Figura 2 Demonstrativo de sinal gerado na saída da modulação por PWM.

Fonte: (RODRIGUES, 2016).

### 1.1.2 Modulação por Largura de Pulso no Espaço Vetorial (SVPWM)

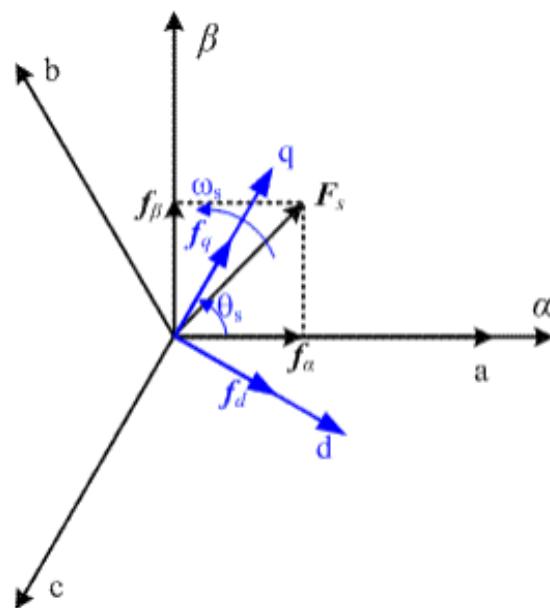

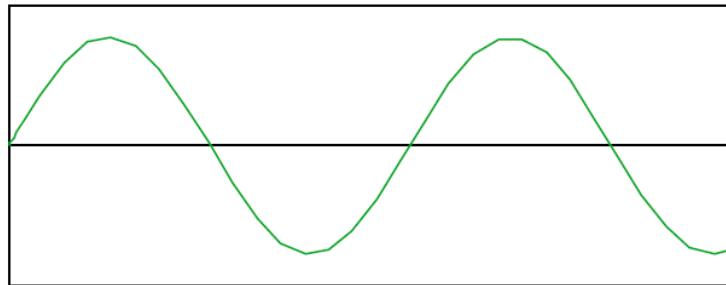

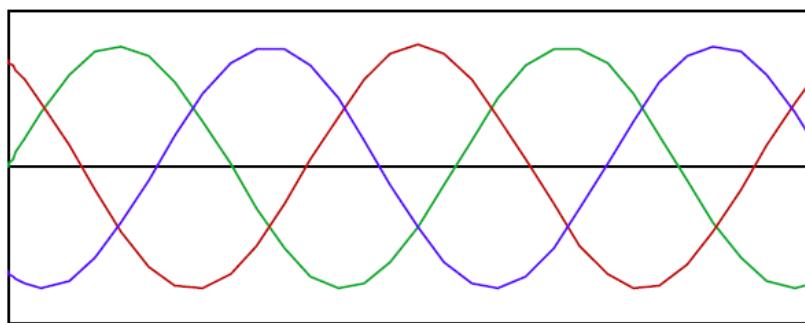

Na literatura, nota-se que as pesquisas existentes mostram que este tipo de controle é separado em três famílias distintas, a que usa o sistema de coordenadas ‘abc’, a que usa o sistema de coordenadas ‘ $\alpha\beta0$ ’ e a que usa o sistema de coordenadas ‘dq0’ (direct-quadrature-zero transformation). Nestas modulações por espaços vetoriais, a corrente de entrada é controlada como uma quantidade de vetor no domínio  $\alpha\beta$  ou dq, assim elas são acionadas pela diferença entre cada onda senoidal trifásica de 120 graus com a portadora, conforme Figura 3 [48].

Figura 3 Relação entre os sistemas de coordenadas ‘abc’, ‘ $\alpha\beta0$ ’ e ‘dq0’.

Fonte: (BORGONOVO, 2001).

### 1.1.3 Modulação por Histerese

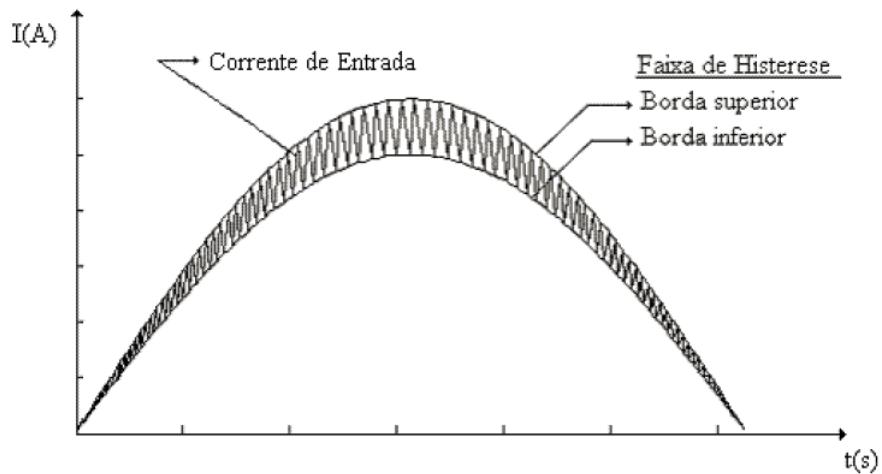

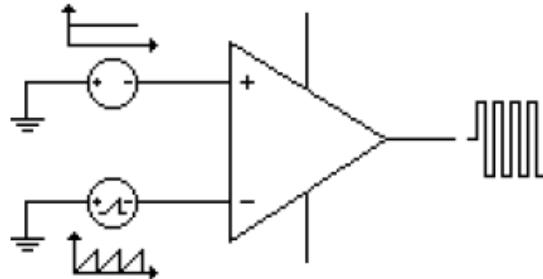

Esta técnica de modulação baseia-se no monitoramento da corrente de entrada ao longo de uma determinada faixa, denominada faixa de histerese [18]. A corrente de entrada, obtida a partir de um sensor de corrente, é comparada com as referências senoidais que compõem os extremos desta faixa. Quando a corrente de entrada atinge o limite exterior da mesma, o conversor é comutado para a etapa de operação, de maneira que a corrente inverta o sentido de variação, passando a oscilar dentro do limite estabelecido pela faixa de histerese, conforme mostra a Figura 4.

Figura 4 Modelo de monitoração da corrente através da faixa de histerese.

Fonte: (BODE e HOLMES, 2000).

## 1.2 Contribuições da Dissertação

No intuito de amenizar os problemas relacionados às oscilações de tensão no barramento CC que uma microrrede está sujeita, às intermitências das fontes alternativas de energia, à conexão excessiva de microgeradores, à conexão e remoção de cargas CC de grande potência e aos curtos-circuitos, o Núcleo de Pesquisas em Eletrônica de Potência (NUPEP) da Faculdade de Engenharia Elétrica (FEELT) da Universidade Federal de Uberlândia (UFU) vem desenvolvendo pesquisas com relevantes publicações envolvendo a utilização de retificadores híbridos robustos, de alto fator de potência e elevado rendimento. Ressalta-se a publicação [19], onde se inclui a contribuição desta dissertação a qual apresenta uma inovadora estrutura retificadora híbrida trifásicas que por sua vez é derivada e aprimorada das publicações de [20] e [21].

---

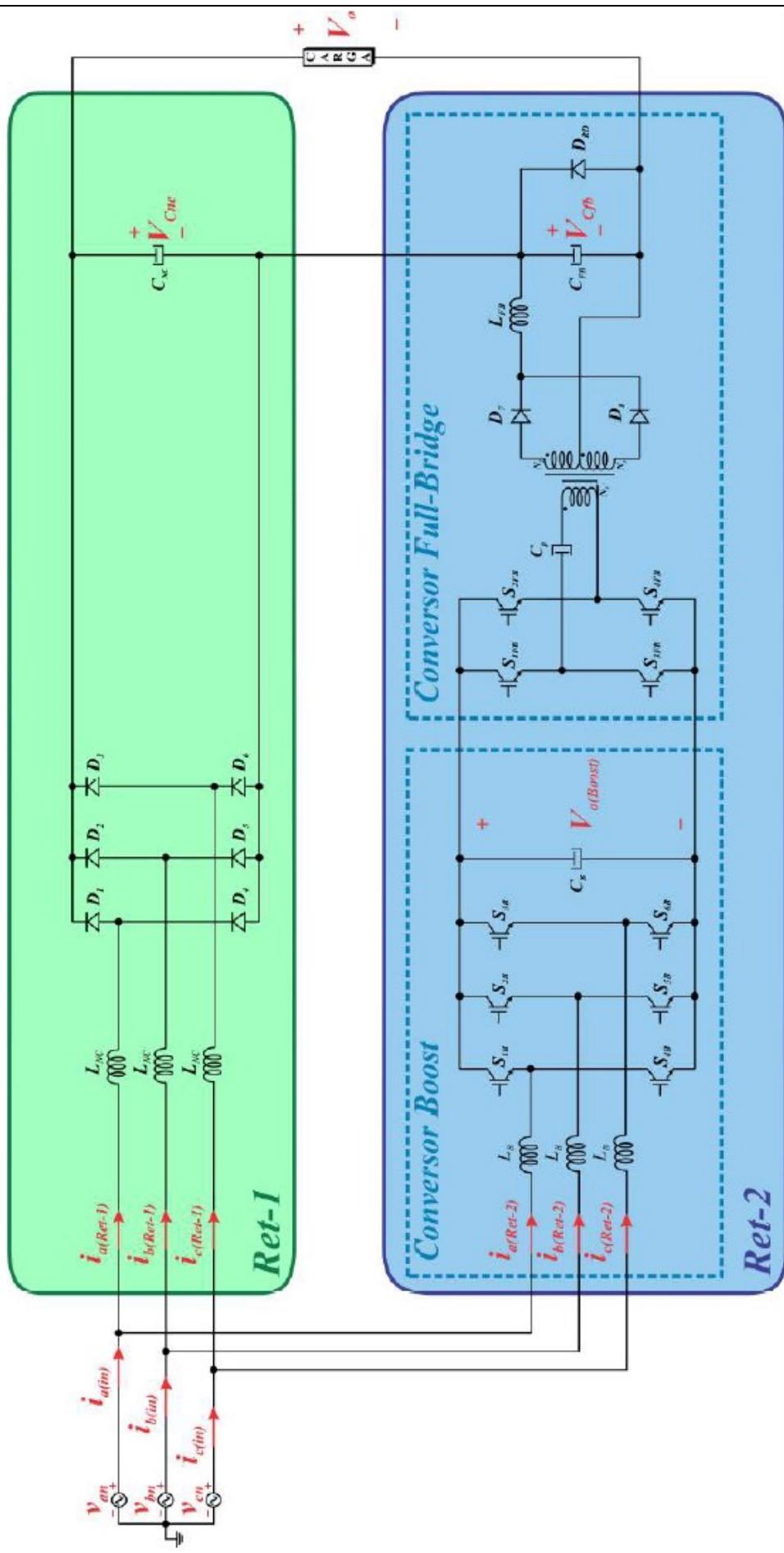

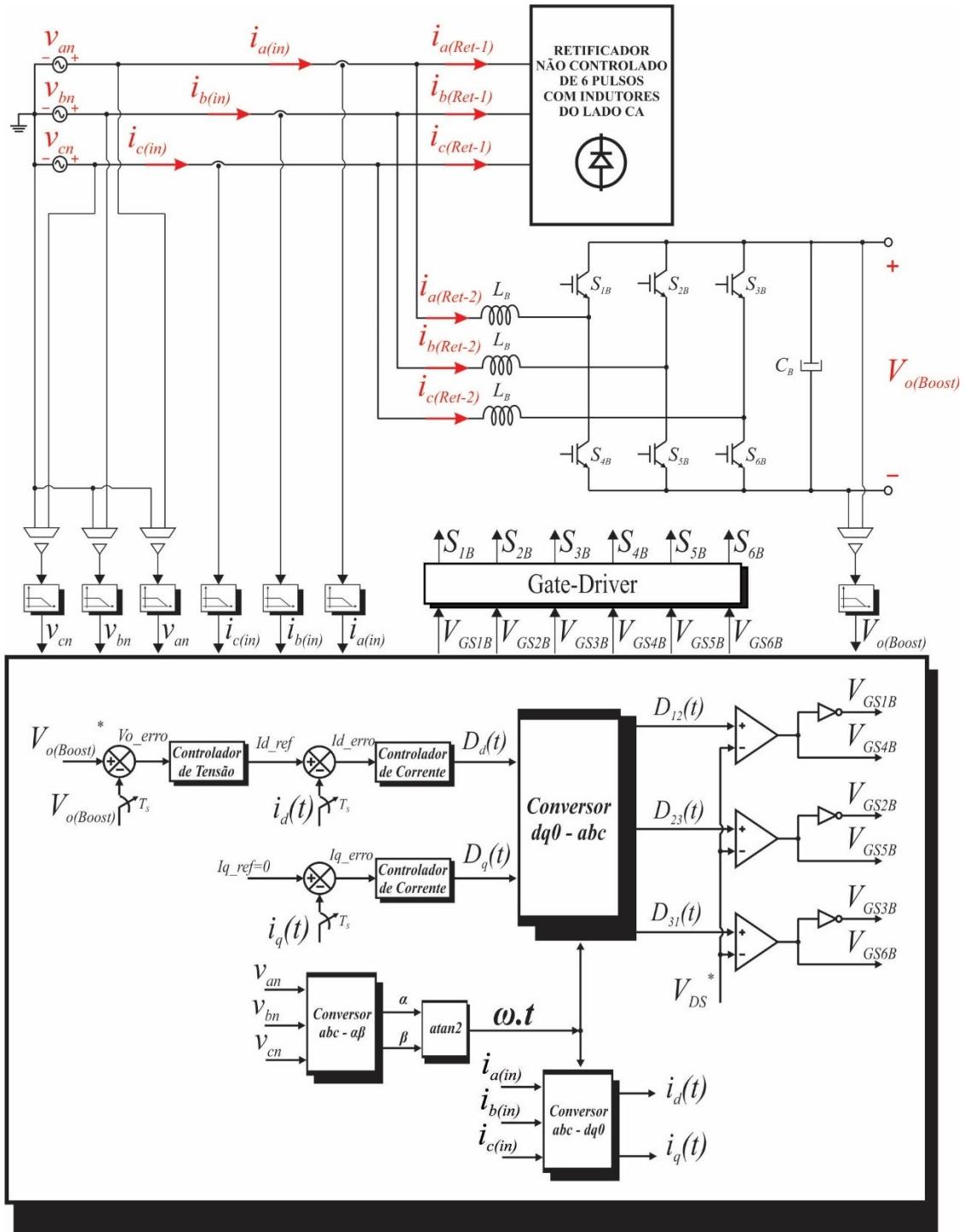

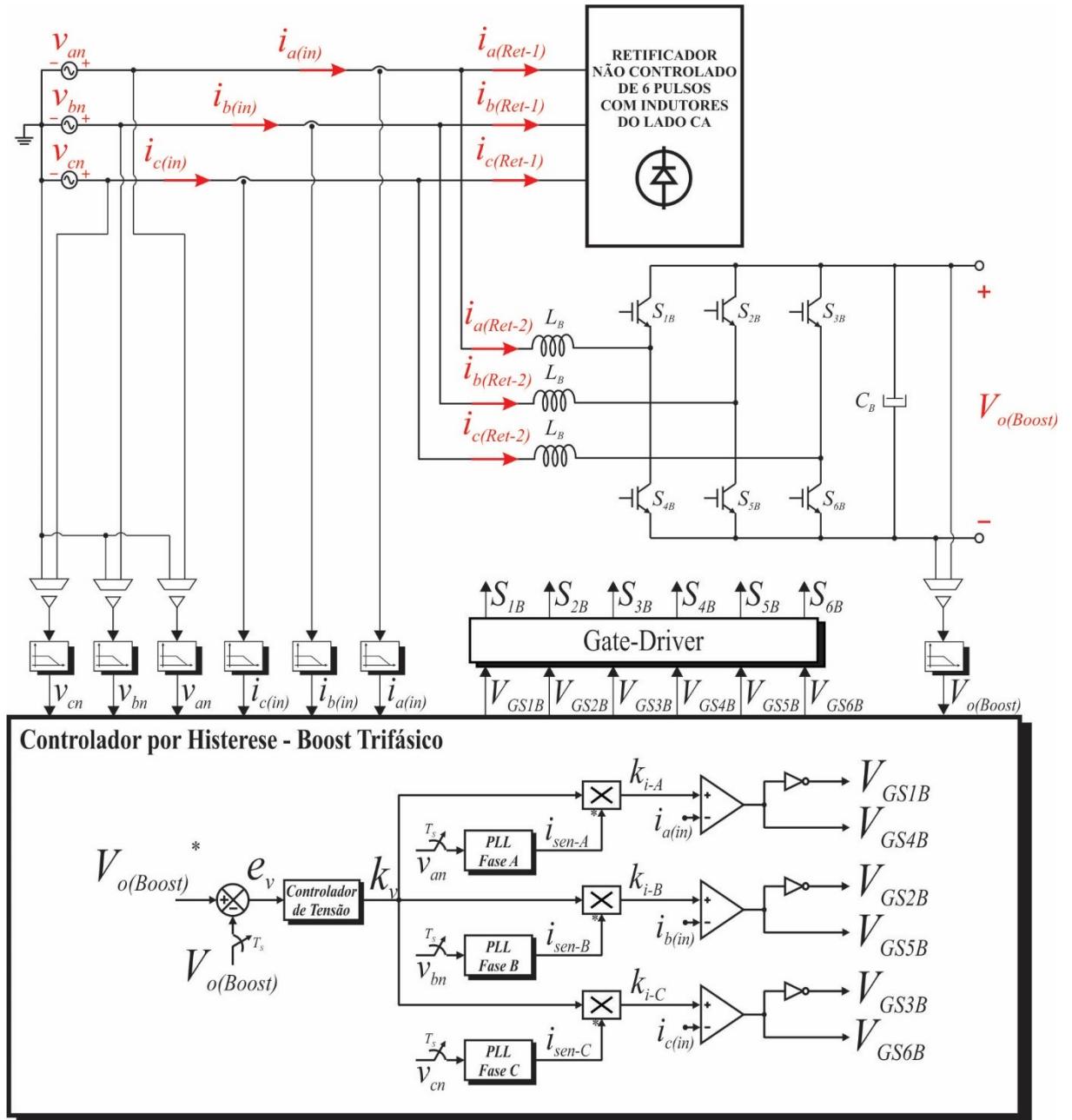

A estrutura proposta por [19], ilustrada na Figura 5, consiste em um retificador não controlado de seis pulsos com indutores do lado CA, denominado de Ret-1. A entrada é conectada em paralelo e a saída é conectada em série com a estrutura Ret-2, que por sua vez é composta por um conversor Boost trifásico totalmente controlado com indutores do lado CA responsável pela imposição de correntes de linha de entrada senoidais, cascaneado a um conversor CC-CC Full-Bridge isolado responsável por promover a compensação série de tensão no barramento CC.

Desta forma, este retificador híbrido trifásico (RHT) é capaz de promover a regulação da tensão no barramento CC em 400 V, utilizando compensação série de tensão, e ao mesmo tempo, proporcionar a imposição de correntes de linha de entrada senoidais para assegurar alto fator de potência e a mitigação do conteúdo harmônico de corrente.

Assim, a fim de oferecer uma melhor alternativa para o controle do conteúdo harmônico de corrente injetado na rede elétrica [22]-[26], este trabalho apresenta uma comparação entre três diferentes métodos de controle do conversor Boost trifásico de seis chaves da estrutura retificadora híbrida trifásica proposta em [19], que são: (i) histerese; (ii) PWM; e (iii) dq0.

Deve-se ressaltar ainda o fato de que a utilização de técnicas de controle digital para aplicações envolvendo eletrônica de potência propiciam significativas vantagens, pois permitem uma maior versatilidade e flexibilidade operacional, e ainda garantem uma redução considerável dos circuitos de controle, uma vez que extensos circuitos de comando que utilizam componentes discretos, podem ser substituídos por um único dispositivo capaz de realizar, digitalmente, múltiplas funções [13]-[15], [19]-[20].

Para tal, a presente dissertação de mestrado volta-se para a implementação de estratégias de controle utilizando o DSP (Digital Signal Processor) TMS320F28335 da Texas Instruments®. Desta forma, os conversores chaveados são capazes de impor a forma de onda desejada, assegurando alto fator de potência e reduzida distorção harmônica total de corrente (DHTI).

Concluindo, destaca-se que, neste trabalho, será apresentada uma avaliação dos três métodos de controle que leva em consideração a correção do fator de potência, a imposição de correntes de linha de entrada senoidais (tendo como base a distorção harmônica de corrente e a regulação da tensão de alimentação do conversor Full-Bridge. Para validar a análise teórica realizada, um protótipo de 5 kW foi construído e avaliado em laboratório.

Figura 5 Estrutura Retificadora Híbrida Trifásica (RHT) proposta em [27].

Fonte: (RODRIGUES e SILVA, 2016).

### 1.3 Objetivo da Dissertação

O objetivo desta pesquisa é averiguar se o controle por histerese utilizado na tese [27] para o conversor Boost trifásico com correção de fator de potência e alta densidade de potência da estrutura retificadora híbrida trifásica, em questão, quando comparado aos controles por PWM e por dq0 apresenta diferenças ao ponto de interferir na qualidade das correntes de linha de entrada e na regulação de tensão no barramento CC quando submetidos aos distúrbios de afundamentos de tensão e degraus de carga, pontos estes que são importantes para avaliar se este RHT atende aos requisitos para utilização em microrredes. Espera-se que os três tipos de controle sejam adequados para a utilização no RHT e que não haja grandes diferenças significativas entre eles.

### 1.4 Estrutura da Dissertação

Esta dissertação está dividida em cinco capítulos, incluindo este introdutório, o qual apresenta um resumo sobre os principais objetivos e contribuições do presente trabalho.

No Capítulo 2 é apresentado a estrutura retificadora híbrida em questão, destacando as características operacionais para imposição de correntes de linha de entrada senoidais e regulação de tensão no barramento CC. Neste capítulo são apresentadas também a teoria e a análise matemática referente aos três tipos de controle em estudo.

No Capítulo 3 são apresentados os principais resultados de simulações computacionais obtidos utilizando a plataforma PSim® a fim de validar os métodos de controle estudados.

No Capítulo 4 são apresentados os resultados experimentais obtidos com um protótipo de laboratório de 5 kW de potência.

E por fim, no Capítulo 5, concluindo esta dissertação de Mestrado, é apresentado uma síntese dos principais resultados alcançados, evidenciando as principais questões atreladas à operação e controle do conversor Boost, bem como algumas sugestões para trabalhos futuros.

---

## CAPÍTULO II

# 2 Estratégias de Controle do Retificador Híbrido Trifásico

---

### 2.1 Considerações Iniciais

O foco deste capítulo é a apresentação da estratégia de controle adotada para estabelecer com que o RHT realize a imposição de correntes de linha de entrada senoidais e a regulação de tensão no barramento CC. A técnica de controle para regulação de tensão é baseada na compensação série de tensão, feita pelo conversor Full-Bridge e as estratégias para imposição de corrente seguem os princípios de controle por histerese, PWM e dq0 no conversor Boost trifásico.

### 2.2 Estratégia de Controle do Conversor Full-Bridge

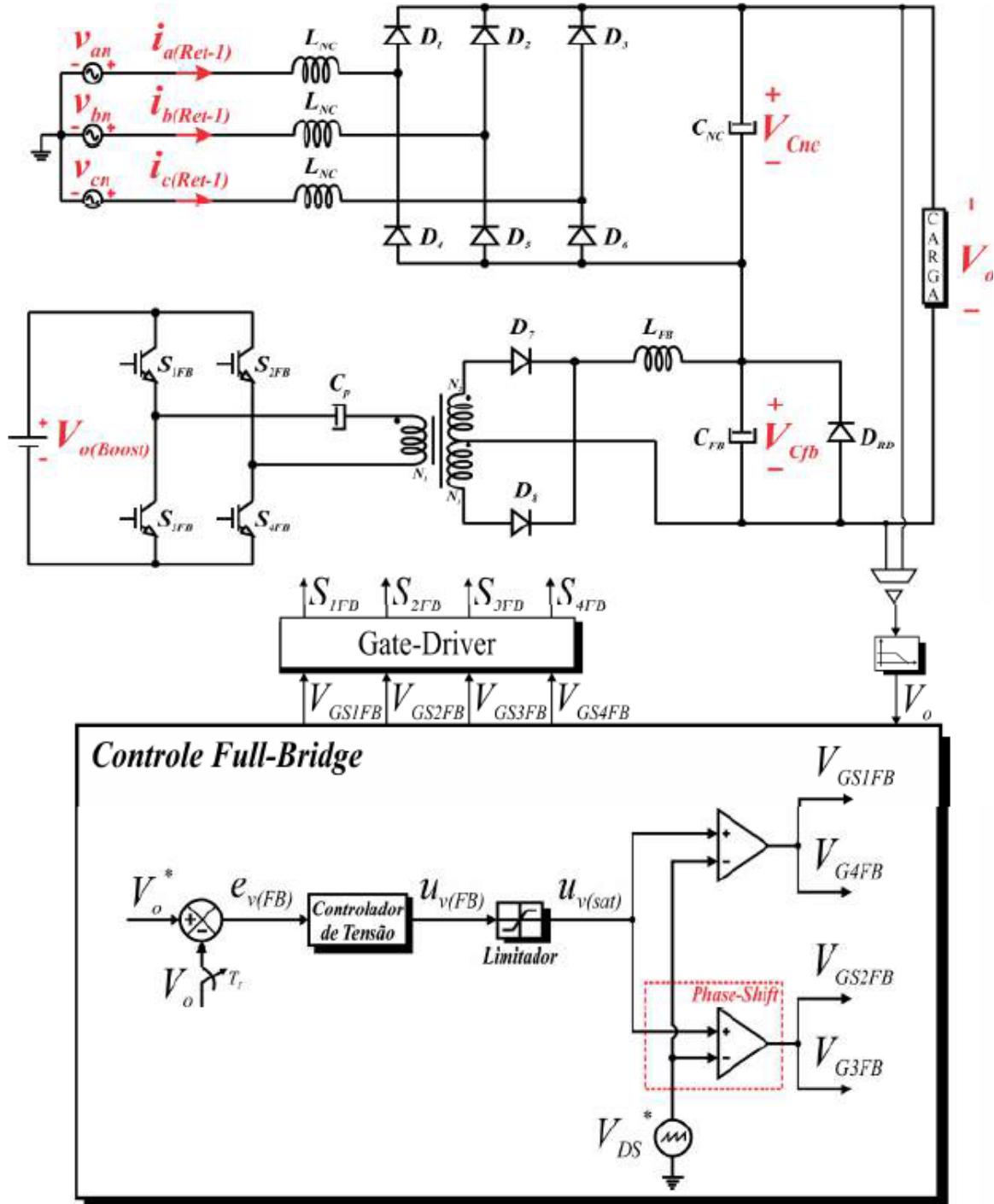

A técnica de controle utilizada para o RHT objetiva a compensação série de tensão no barramento CC através da utilização de um conversor Full-Bridge isolado cujo capacitor de saída é ligado em série com o capacitor de saída do retificador não controlado [27].

No que diz respeito à compensação série de tensão no barramento CC, a Figura 6 demonstra o diagrama esquemático do circuito de controle do conversor Full-Bridge, considerando o circuito equivalente, onde a saída do conversor Boost é vista pela entrada do conversor Full-Bridge como uma fonte de tensão  $V_{o(Boost)}$ .

De modo a promover uma tensão de 400 V no barramento CC, utiliza-se um controlador de tensão que processa o sinal de erro  $e_{v(FB)}$  entre a tensão de saída  $V_o$  e a referência de tensão  $V_{o*}$ , definida em 400 V. O controlador fornece um sinal de saída  $u_{v(FB)}$  que é utilizado para a geração dos pulsos enviados aos interruptores  $S_{1FB}$ ,  $S_{2FB}$ ,  $S_{3FB}$  e  $S_{4FB}$  do conversor Full-Bridge. O objetivo da lógica para geração dos pulsos dos interruptores do conversor Full-Bridge é reduzir o erro  $e_{v(FB)}$  a zero e consequentemente estabelecer que a tensão no barramento CC siga a referência de tensão desejada.

Conforme definido no equacionamento matemático apresentado em [27], para garantir que a razão cíclica máxima de operação dos interruptores seja de 0,49 para a metade do período de chaveamento ( $T_{ch}$ ), aplica-se um limitador sobre o sinal de saída  $u_{v(FB)}$  do controlador de tensão. Para a geração dos sinais de pulso enviados às chaves  $S_{1FB}$  ( $V_{GS1FB}$ ) e  $S_{4FB}$  ( $V_{GS4FB}$ ), estabelece-se uma estratégia de controle baseada em modulação por largura de pulso, onde é realizada a comparação entre a saída saturada ( $u_{v(sat)}$ ) e uma onda dente-de-serra de amplitude

unitária e frequência de 25 kHz ( $V_{DS*}$ ). Desta forma, enquanto  $u_{v(sat)}$  for maior que  $V_{DS*}$ , níveis altos de pulso são enviados para  $S_{1FB}$  e  $S_{4FB}$ , e caso contrário, são enviados níveis baixos de pulso.

Figura 6 Diagrama esquemático do circuito de controle do conversor Full-Bridge.

Fonte: (RODRIGUES, 2016).

## 2.3 Estratégia de Controle do Conversor Boost

Além da técnica de compensação série de tensão no barramento CC através da utilização de um conversor Full-Bridge o RHT objetiva também a imposição de correntes de linha de entrada senoidais através da utilização do conversor Boost trifásico para garantir uma baixa distorção harmônica de corrente e um elevado fator de potência na entrada.

O controle deste Conversor Boost é o foco principal de estudo deste trabalho, onde os métodos de controle por histerese, PWM e dq0 foram comparados afim de averiguar se ocorrem diferenças significativas, ao ponto de interferir na qualidade das correntes de linha de entrada e na regulação de tensão no barramento CC.

### 2.3.1 Controle do Conversor Boost pela Transformada dq0

Utilizando a teoria dos eixos girantes dq [28]-[31], o controle vetorial deste conversor é realizado alinhando o eixo **d** com o vetor tensão da rede. Será utilizado o método convencional de controle da tensão na saída do conversor em que a mesma é forçada a seguir um sinal de referência.

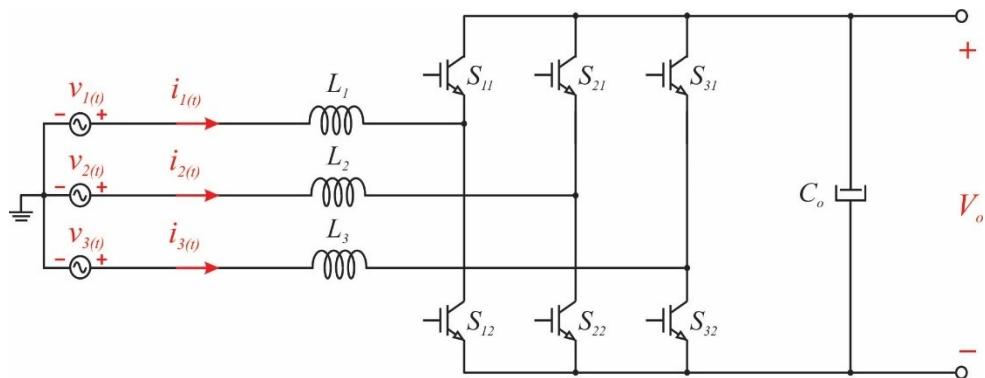

Na dissertação de mestrado de [48] foi elaborado e demonstrado uma técnica de controle para o conversor Boost apresentado na Figura 7. Uma parte desta demonstração será citado para melhor entendimento desta técnica de controle.

Figura 7 Circuito do conversor Boost trifásico simplificado para análise.

Fonte: (RODRIGUES, 2016).

Para iniciar a análise supõe-se que a alimentação é senoidal e equilibrada, de forma que as tensões de fase são definidas pela equação (1).

$$\begin{cases} V_1(t) = V_p \cdot \sin(\omega \cdot t) \\ V_2(t) = V_p \cdot \sin(\omega \cdot t - 120^\circ) \\ V_3(t) = V_p \cdot \sin(\omega \cdot t + 120^\circ) \end{cases} \quad (\text{Eq. 1})$$

Desta forma, as tensões de linha são dadas por:

$$\begin{cases} V_{12}(t) = V_1(t) - V_2(t) = \sqrt{3} \cdot V_p \cdot \sin(\omega \cdot t + 30^\circ) \\ V_{23}(t) = V_2(t) - V_3(t) = \sqrt{3} \cdot V_p \cdot \sin(\omega \cdot t - 90^\circ) \\ V_{31}(t) = V_3(t) - V_1(t) = \sqrt{3} \cdot V_p \cdot \sin(\omega \cdot t + 150^\circ) \end{cases} \quad (\text{Eq. 2})$$

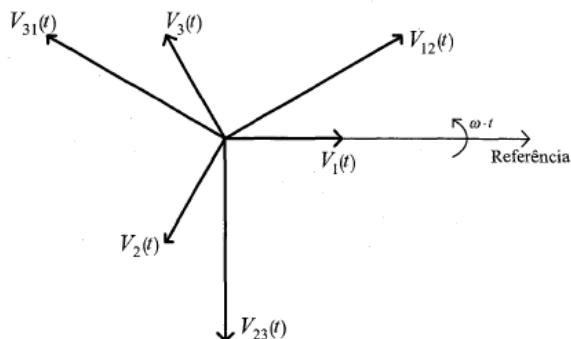

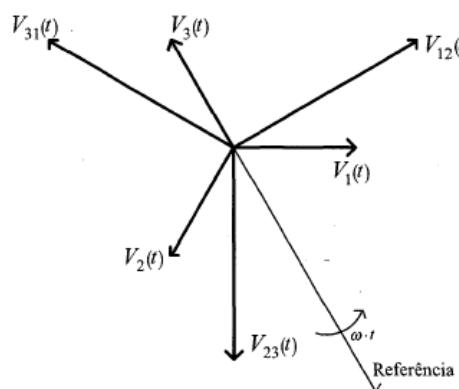

Assim, as tensões de linha e de fase podem ser representadas vetorialmente conforme apresentado na Figura 8, onde a referência permanece em repouso e os vetores que representam as tensões giram no sentido anti-horário com velocidade angular correspondente à frequência da rede.

Alterando-se a referência convenientemente, onde a referência ainda está em repouso e os vetores (que representam as tensões) permanecem girando no sentido anti-horário, tem-se a Figura 9.

Figura 8 Representação vetorial das tensões de fase e de linha.

Fonte: (BORGONOVO, 2001).

Figura 9 Representação vetorial das tensões de fase e de linha, com a referência convenientemente deslocada (atrasada 60° em relação à referência da Figura 8).

Fonte: (BORGONOVO, 2001).

Então, a partir da Figura 9, com a referência deslocada ( $60^\circ$  atrasada em relação à referência anterior apresentada na Figura 8), as tensões de linha são dadas por:

$$\begin{cases} V_{12}(t) = \sqrt{3}.V_p \cdot \sin(\omega.t + 90^\circ) = \sqrt{3}.V_p \cdot \cos(\omega.t) \\ V_{23}(t) = \sqrt{3}.V_p \cdot \sin(\omega.t - 30^\circ) = \sqrt{3}.V_p \cdot \cos(\omega.t - 120^\circ) \\ V_{31}(t) = \sqrt{3}.V_p \cdot \sin(\omega.t + 210^\circ) = \sqrt{3}.V_p \cdot \cos(\omega.t + 120^\circ) \end{cases} \quad (\text{Eq. 3})$$

De posse destas informações foi desenvolvido um equacionamento para obter o modelo do conversor visto a partir da entrada (CA) [48]. Este equacionamento foi desenvolvido com o intuito de obter a equação (4).

$$\begin{cases} 0 = L \cdot \frac{dI_o(t)}{dt} + V_o \cdot D_o(t) \\ \sqrt{\frac{3}{2}} \cdot V_p = L \cdot \frac{dI_d(t)}{dt} - \omega \cdot L \cdot I_q(t) + V_o \cdot D_o(t) \\ 0 = L \cdot \frac{dI_q(t)}{dt} + \omega \cdot L \cdot I_d(t) + V_o \cdot D_o(t) \end{cases} \quad (\text{Eq. 4})$$

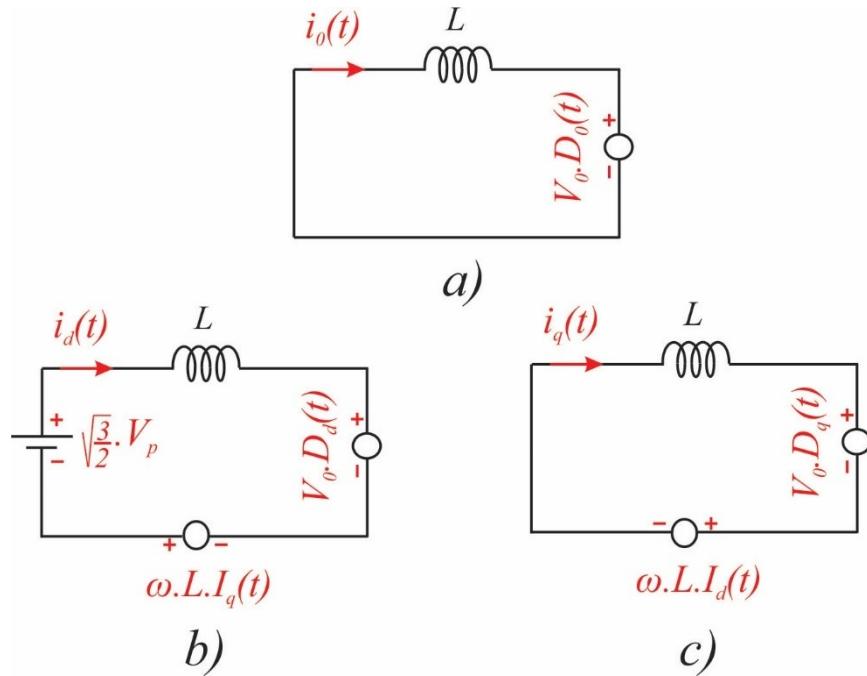

A partir da equação (4), obtém-se os circuitos equivalentes de sequência 0, sequência d e sequência q, apresentados na Figura 10.

Figura 10 Circuitos equivalentes das sequências a) 0; b) d; c) q.

Fonte: (BORGONOVO, 2001).

Visando obter a função de transferência das correntes em função das razões cíclicas, desenvolve-se a equação (4) obtendo-se a equação (5).

$$\begin{bmatrix} i_d(s) \\ i_q(s) \end{bmatrix} = \frac{V_0}{L} \cdot \frac{1}{s^2 + \omega^2} \cdot \begin{bmatrix} -s & -\omega \\ \omega & -s \end{bmatrix} \cdot \begin{bmatrix} d_d(s) \\ d_q(s) \end{bmatrix} \quad (\text{Eq. 5})$$

Desta forma, tem-se na equação (5) a função de transferência das correntes em função das razões cíclicas, deve-se lembrar, no entanto que as razões cíclicas  $D_d(t)$  e  $D_q(t)$  não são efetivamente grandezas físicas, mas variáveis às quais deve-se aplicar a transformada inversa de Park, para então se obter as razões cíclicas reais, este estudo será apresentado com detalhes mais adiante na definição da arquitetura do sistema de controle.

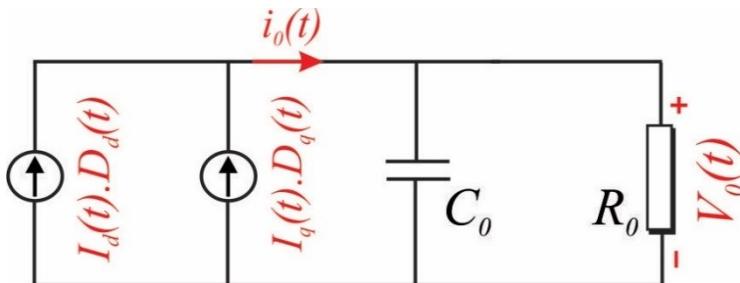

Além do equacionamento para obter o modelo do conversor visto a partir da entrada (CA) um equacionamento para obter o modelo do conversor visto a partir da saída (CC) também foi desenvolvido em [48]. Este equacionamento foi desenvolvido com o intuito de obter a equação (6).

$$I_0(t) = I_d(t) \cdot D_d(t) + I_q(t) \cdot D_q(t) \quad (\text{Eq. 6})$$

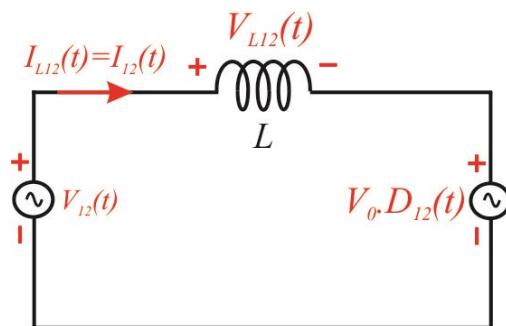

A partir da equação (6) o circuito equivalente visto a partir da saída (CC), é apresentado na Figura 11.

Figura 11 Circuito equivalente visto pela saída (CC) do conversor Boost.

Fonte: (BORGONOVO, 2001).

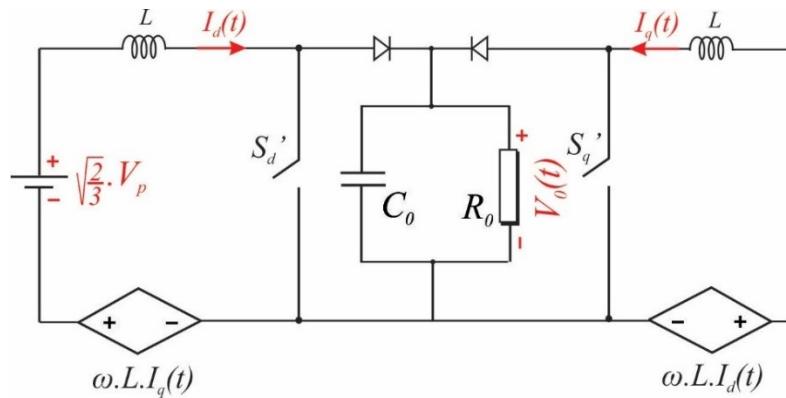

Fazendo uma interseção dos circuitos equivalentes vistos pela entrada apresentados na Figura 10 b) e na Figura 10 c), com o circuito equivalente visto pela saída apresentado na Figura 11, pode-se obter um circuito equivalente para o conversor, que é apresentado na Figura 12.

Figura 12 Circuito equivalente para o conversor Boost, visto pela entrada ou pela saída, quando aplicada a transformação de Park.

Fonte: (BORGONOVO, 2001).

Na Figura 12 os interruptores  $S_d'$  e  $S_q'$  se comportam da seguinte maneira:

$$\begin{cases} S_d' = \text{aberto}, \text{se } D_d(t) = 1 \\ S_d' = \text{fechado}, \text{se } D_d(t) = 0 \\ S_q' = \text{aberto}, \text{se } D_q(t) = 1 \\ S_q' = \text{fechado}, \text{se } D_q(t) = 0 \end{cases}$$

#### A. Princípio de Funcionamento do Controle por dq0 implementado

Inicialmente, considera-se que o conversor vai operar como conversor CA-CC, com potência reativa nula, ou seja,  $Q_{IN} = 0$ , desta forma, observando a equação (7), observa-se que para que se tenha potência reativa nula na entrada, a corrente de sequência q ( $I_q(t)$ ) deve seguir uma referência nula, ou seja, sua referência deve ser zero.

$$\begin{cases} P_{IN} = V_d \cdot I_d \\ Q_{IN} = V_d \cdot I_q \end{cases} \quad (\text{Eq. 7})$$

Por outro lado, se a potência reativa for nula, a partir da equação (8) se obtém a equação (9). Desta forma tem-se uma função de transferência bastante simples para a tensão de saída em função da corrente de sequência d, podendo-se então implementar uma malha de tensão, que irá gerar diretamente a referência para a corrente de sequência d ( $I_d(t)$ )[48].

$$v_0(s) = \frac{\sqrt{3}V_pR_0}{\sqrt{2}V_0} \cdot \left( i_d(s) \cdot \frac{1 - s \cdot \frac{2L.P_0.\eta}{3.V_p^2}}{1 + s.R_0.C_0} - i_q(s) \cdot \frac{2.Q_{IN}.L}{3.V_p^2} \cdot \frac{s}{1 + s.R_0.C_0} \right) \quad (\text{Eq. 8})$$

$$\frac{v_0(s)}{i_d(s)} = \frac{\sqrt{3}V_p R_0}{\sqrt{2}V_0} \cdot \frac{1-s \cdot \frac{2LP_0\eta}{3V_p^2}}{1+sR_0C_0} \quad (\text{Eq. 9})$$

Deve-se lembrar ainda que é necessário aplicar a transformada inversa de Park sobre as variáveis de controle  $D_d(t)$  e  $D_q(t)$ , obtendo-se então  $D_{12}(t)$ ,  $D_{23}(t)$  e  $D_{31}(t)$ , onde a partir destas pode-se obter  $D_1(t)$ ,  $D_2(t)$  e  $D_3(t)$ , sobre as quais aplica-se a modulação PWM para comandar diretamente os interruptores, conforme referência ilustrativa da Figura 13. A arquitetura proposta para o sistema de controle é apresentada na Figura 14.

Então, já que a potência reativa desejada na entrada é nula, a tensão de saída depende unicamente da corrente  $I_d(t)$  de forma que se pode utilizar um controlador linear convencional para a malha de tensão.

Já para a malha de corrente, a função de transferência das correntes em função das razões cíclicas é apresentada na equação (10).

$$\begin{aligned} i_d(s) &= \frac{V_0}{L} \left[ -d_d(s) \cdot \frac{s}{s^2 + \omega^2} - d_q(s) \cdot \frac{\omega}{s^2 + \omega^2} \right] \\ i_q(s) &= \frac{V_0}{L} \left[ -d_d(s) \cdot \frac{\omega}{s^2 + \omega^2} - d_q(s) \cdot \frac{s}{s^2 + \omega^2} \right] \end{aligned} \quad (\text{Eq. 10})$$

Entretanto, como o objetivo neste momento não é otimizar a resposta dinâmica do sistema, mas basicamente comprovar a validade do estudo apresentado, serão feitas algumas considerações, afim de simplificar o projeto dos controladores.

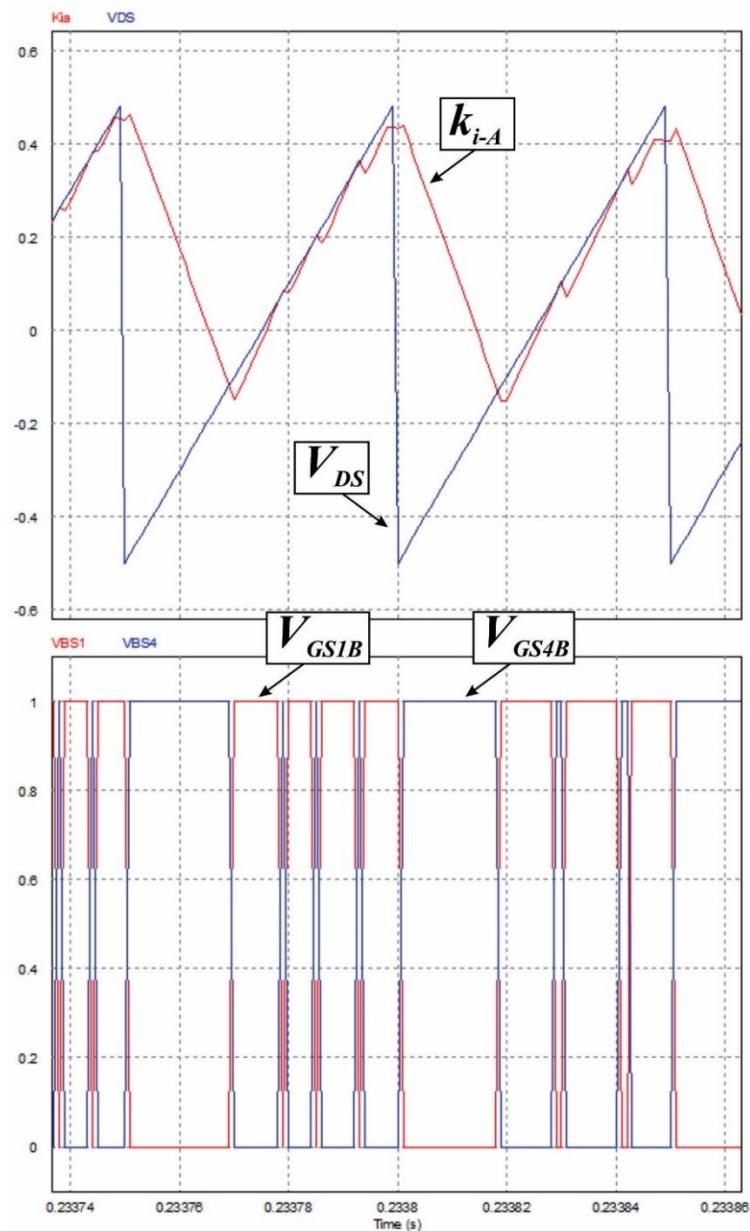

Figura 13 Lógica de variação dos sinais de gatilho dos interruptores S1B e S4B do conversor Boost por dq0.

Fonte: Dados do próprio autor.

Figura 14 Diagrama esquemático do circuito de controle do conversor Boost por dq0.

Fonte: Adaptado de (BORGONOVO, 2001) e (RODRIGUES, 2016).

Inicialmente, define-se que a frequência de cruzamento da função de transferência de laço aberto da malha de corrente deve estar ao menos uma década abaixo da frequência da rede, desta forma pode-se afirmar que:

$$\begin{cases} s + \omega \approx \omega \\ s^2 + \omega^2 = \omega^2 \end{cases} \quad (\text{Eq. 11})$$

Adotando então esta hipótese, a função de transferência da equação (10) resume-se a:

$$\begin{cases} \frac{i_d(s)}{d_q(s)} = -\frac{V_0}{\omega \cdot L} \\ \frac{i_q(s)}{d_d(s)} = \frac{V_0}{\omega \cdot L} \end{cases} \quad (\text{Eq. 12})$$

Desta forma, a partir da equação (9) pode-se definir um circuito equivalente para se analisar a corrente  $I_{12}(t)$ , que é apresentado na Figura 15, lembrando que o circuito é idêntico e os resultados analógicos para as correntes  $I_{23}(t)$  e  $I_{31}(t)$ .

Figura 15 Circuito equivalente visto pela corrente  $I_{12}(t)$ .

Fonte: (BORGONOVO, 2001)

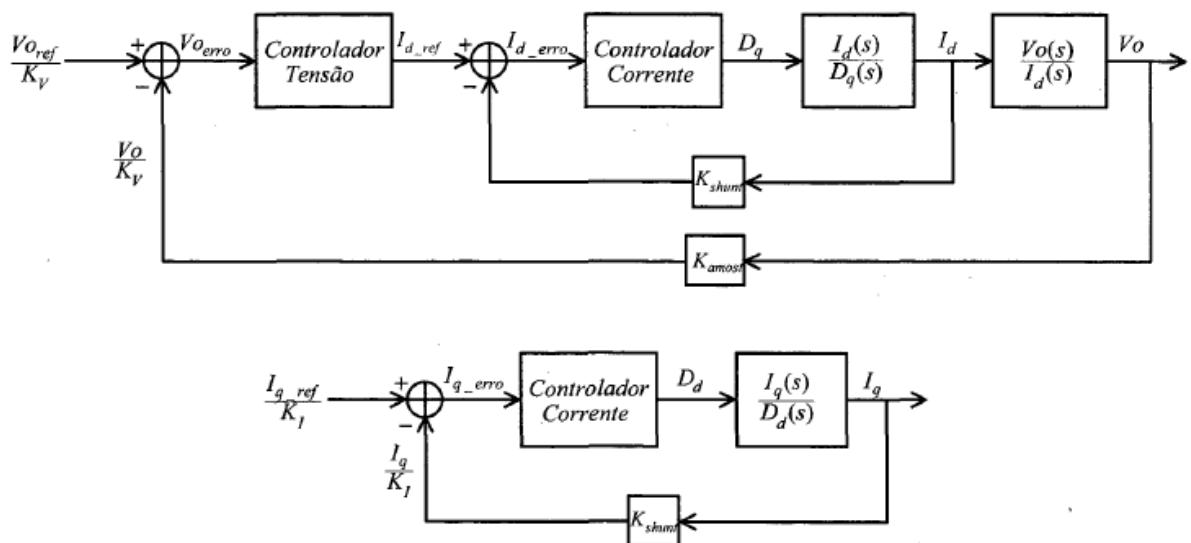

A partir das hipóteses adotadas, pode-se implementar malhas de controle independentes para controlar as correntes  $I_d(t)$  e  $I_q(t)$ , de forma que o sistema de controle proposto pode ser representado pelo diagrama de blocos mostrado na Figura 16.

Figura 16 Representação por diagrama de blocos para o sistema de controle por dq0.

Fonte: (BORGONOVO, 2001)

### B. Projeto do controlador de Corrente

A partir da equação (12) pode-se observar que é possível utilizar o mesmo controlador de corrente tanto para controlar a corrente  $I_d(t)$ , quanto para a corrente  $I_q(t)$ , exceto por uma inversão de sinais, o que pode ser resolvido facilmente, bastando realimentar positivamente a corrente  $I_d(t)$ . Assim sendo, tem-se a função de transferência completa do sistema:

$$\begin{aligned} i_d(s) &= \frac{V_0}{L} \left[ -d_d(s) \cdot \frac{s}{s^2 + \omega^2} - d_q(s) \cdot \frac{\omega}{s^2 + \omega^2} \right] \\ i_q(s) &= \frac{V_0}{L} \left[ d_d(s) \cdot \frac{\omega}{s^2 + \omega^2} - d_q(s) \cdot \frac{s}{s^2 + \omega^2} \right] \end{aligned} \quad (\text{Eq. 13})$$

Desta forma, analisando a equação (13) em [48] consegue-se, por analogia, sugerir a utilização de um controlador integrador para as duas malhas de corrente, que na verdade pode-se utilizar o mesmo controlador para garantir o erro estático nulo. Assim, a função de transferência do controlador é dada por:

$$G(s) = k \cdot \frac{(s + \frac{1}{T_i})}{s} \quad (\text{Eq. 14})$$

Onde  $k$  é a constante do sistema e  $T_i$  o tempo integral.

### C. Projeto do controlador de Tensão

Analizando o diagrama de blocos da Figura 16, a função de transferência total da planta pode ser dada pela equação (15).

$$G(s) = \frac{\sqrt{3} \cdot V_p \cdot V_0}{\sqrt{2} \cdot P_0 \cdot K_{shunt}} \cdot \frac{1 - s \cdot \frac{2 \cdot L \cdot P_0 \cdot \eta}{3 \cdot V_p^2}}{\left(1 + \frac{V_T \cdot R \cdot C \cdot \omega \cdot L}{K_{shunt} \cdot V_0}\right) \cdot \left(1 + s \cdot \frac{V_0^2}{P_0} \cdot C_0\right)} \quad (\text{Eq. 15})$$

Ou:

$$G(s) = k_v \cdot \frac{1 - \frac{s}{\omega_{Z1}}}{\left(1 + \frac{s}{\omega_{P1}}\right) \cdot \left(1 + \frac{s}{\omega_{P2}}\right)} \quad (\text{Eq. 16})$$

Onde:

$$\left\{ \begin{array}{l} k_v = \frac{\sqrt{3}.V_p.V_0}{\sqrt{2}.P_0.K_{shunt}} \\ \omega_{Z1} = \frac{3.V_p^2}{2.L.P_0.\eta} \\ \omega_{P1} = \frac{K_{shunt}.V_0}{2.\pi.V_T.R.C.f_r.L} \\ \omega_{P2} = \frac{P_0}{V_0^2.C_0} \end{array} \right. \quad (\text{Eq. 17})$$

No entanto, para simplificar o projeto do controlador, determina-se que a frequência de cruzamento da função de transferência de laço aberto  $\omega_c$  seja tal que:

$$\left\{ \begin{array}{l} \omega_c < \frac{\omega_{Z1}}{10} \\ \omega_c < \frac{\omega_{P2}}{10} \end{array} \right. \quad (\text{Eq. 18})$$

Em termos práticos, será possível observar mais adiante que estas considerações são factíveis, principalmente com relação à frequência do zero, que aliás está no semi-plano direito, o que faz com que seu diagrama de fase, na frequência, se comporte como se fosse um zero, desta forma o fato da frequência deste zero ser bastante elevada em relação à frequência de cruzamento facilita o projeto do controlador.

Assim, feitas as considerações, a função de transferência apresentada na equação (16) resume-se a equação (19).

$$G(s) = \frac{k_v}{\left(1 + \frac{s}{\omega_{P1}}\right)} \quad (\text{Eq. 19})$$

#### D. Conclusões referente ao Controle por Transformada dq0

Nesta seção foi apresentado um resumo do equacionamento matemático da técnica de controle por dq0 para o conversor Boost que foi desenvolvido em [48]. Neste resumo foi demonstrado que para chegar nas funções de transferências dos controladores de corrente e de tensão foi necessário elaborar um princípio de funcionamento para o controle descrito que por sua vez foi desenvolvido com base nas análises matemáticas desenvolvidas para os modelos do conversor Boost visto a partir da entrada (CA) e da saída (CC). Toda esta análise foi desenvolvida levando-se em consideração a teoria dos eixos girantes dq para realizar o controle vetorial deste conversor.

### 2.3.2 Controle do Conversor Boost por Histerese

Esta técnica de modulação baseia-se no monitoramento da corrente de entrada ao longo de uma determinada faixa, denominada faixa de histerese [18]. A corrente de entrada, obtida a partir de um sensor de corrente, é comparada com as referências senoidais que compõem os extremos desta faixa. Quando a corrente de entrada atinge o limite exterior da mesma, o conversor é comutado para a próxima etapa de operação, e a corrente passa a oscilar dentro do limite estabelecido pela faixa de histerese, conforme mostra a Figura 4.

A frequência de chaveamento resultante é variável, o que implicará componentes harmônicas da corrente de entrada múltiplas da menor frequência obtida, o que pode ser comprovado através da análise de Fourier. Outro fato também importante a ser considerado reside nos elementos de filtragem do conversor, que assumirão dimensões ampliadas, pois devem ser dimensionados para a menor frequência.

Assim, qualquer tentativa de elevar a menor frequência de chaveamento a um nível equivalente utilizado no controle com frequência fixa resultaria em um aumento das perdas por comutação, uma vez que a frequência média de chaveamento do conversor também aumentaria. Alguns trabalhos relatam a utilização do controle por histerese com mais de uma largura de banda, com o intuito de reduzir a variação da frequência de chaveamento e consequentemente, minimizar os efeitos indesejáveis da mesma [32].

O método de controle por histerese apresenta as seguintes características:

- Frequência variável;

- Elevado fator de potência;

- Operação em modo contínuo;

- Necessidade de um sensor de corrente e de um multiplicador para a regulação da tensão de saída, tornando o esquema do circuito de controle complexo.

O projeto e a análise do controle pela corrente média para a correção do fator de potência de entrada dos conversores CA-CC têm sido assunto de vários artigos técnicos [33]-[36]. Nesta técnica de controle, o sinal da corrente de entrada é subtraído da corrente de referência, e posteriormente aplicado a um circuito compensador com pólos e zeros, dimensionados em função dos parâmetros do conversor. A saída deste circuito compensador é comparada com um sinal triangular periódico para gerar os pulsos com frequência constante, os quais serão utilizados a chave de acionamento do conversor. A Figura 17 ilustra o comportamento da corrente de entrada quando esta estratégia de controle é empregada [49].

O circuito compensador, presente neste esquema de controle, deve ser projetado para obter uma resposta dinâmica rápida sem sofrer os efeitos das oscilações da corrente de entrada. Para isso, é necessário que este circuito filtre as componentes de maior frequência presentes no sinal de erro e, ao mesmo tempo, possa atuar como integrador para frequências mais baixas, proporcionando, assim, um erro menor em regime permanente. Assim, a Figura 18 ilustra esta forma de controle.

Figura 17 Comportamento da corrente no indutor do filtro no controle por histerese pela corrente média.

Fonte: (GALELLI, 2005).

Figura 18 Diagrama de blocos representando o controle por histerese pela corrente média.

Fonte: (GALELLI, 2005).

Como a corrente de referência varia constantemente em função de sua característica senoidal, sempre haverá um pequeno erro intrínseco, que em determinados trechos será positivo ou negativo, uma vez que, através da ação do circuito integrador presente no circuito de compensação, o erro médio tende a oscilar em torno de zero.

---

#### A. Princípio de Funcionamento do Controle por Histerese Implementado

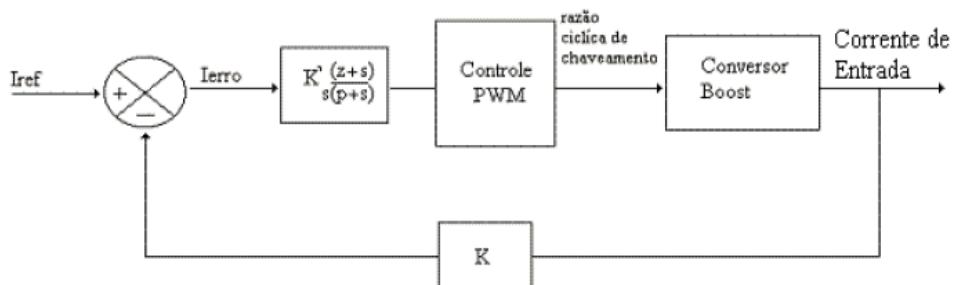

O controle por histerese implementado nesta dissertação baseia-se nesta técnica de controle por corrente média e consta basicamente de duas malhas, a interna de corrente e a externa de tensão. Para o correto funcionamento desta estratégia de controle, são realizadas sete aquisições de sinais: os sinais das correntes de linha de entrada ( $i_{a(in)}$ ,  $i_{b(in)}$  e  $i_{c(in)}$ ); os sinais das tensões fase-neutro ( $v_{an}$ ,  $v_{bn}$  e  $v_{cn}$ ); e o sinal da tensão no capacitor CB ( $V_{o(Boost)}$ ). É importante ressaltar que as aquisições das tensões de alimentação são realizadas para fins de referências de fase utilizadas pelos PLLs (Phase Lock Loop) visando estabelecer referências de corrente senoidais em fase com as tensões fase-neutro [27].

No que tange a imposição de correntes de linha de entrada e o fornecimento de uma tensão contínua de 350 V na entrada do conversor Full-Bridge, a Figura 19 demonstra o diagrama esquemático do circuito de controle do conversor Boost com o referido controle por histerese.

Para a malha de tensão, afim de promover uma tensão de 350 V na entrada do conversor Full-Bridge, utiliza-se um controlador de tensão que processa o sinal de erro  $e_v$  entre a tensão de saída do conversor Boost  $V_{o(Boost)}$  e a referência de tensão  $V_{o(Boost)}^*$ , definida em 350 V. O sinal de saída  $k_v$  deste controlador de tensão é então multiplicado às referências senoidais digitais  $i_{sen-A}^*$ ,  $i_{sen-B}^*$  e  $i_{sen-C}^*$  geradas pelos PLLs de cada fase, de forma a variar a amplitude das referências de corrente objetivando compensar qualquer variação na tensão  $V_{o(Boost)}$ .

Assim, caso alguma queda na tensão de saída do conversor Boost ocorra (devido a um afundamento temporário nas tensões de alimentação, por exemplo), o controlador de tensão gera um sinal  $k_v$ , que ao ser multiplicado a  $i_{sen-A}^*$ ,  $i_{sen-B}^*$  e  $i_{sen-C}^*$ , promove o aumento da amplitude destas referências, fazendo com que o conversor Boost drene mais corrente da rede de modo a manter o processamento da potência de saída constante, garantindo que a tensão  $V_{o(Boost)}$  permaneça no valor de referência. As referências finais de corrente  $k_{i-A}$ ,  $k_{i-B}$  e  $k_{i-C}$  são determinadas, portanto, pela multiplicação de  $i_{sen-A}^*$ ,  $i_{sen-B}^*$  e  $i_{sen-C}^*$ , respectivamente, pela saída  $k_v$  do controlador de tensão.

Figura 19 Diagrama esquemático do circuito de controle do conversor Boost por Histerese.

Fonte: (RODRIGUES, 2016).

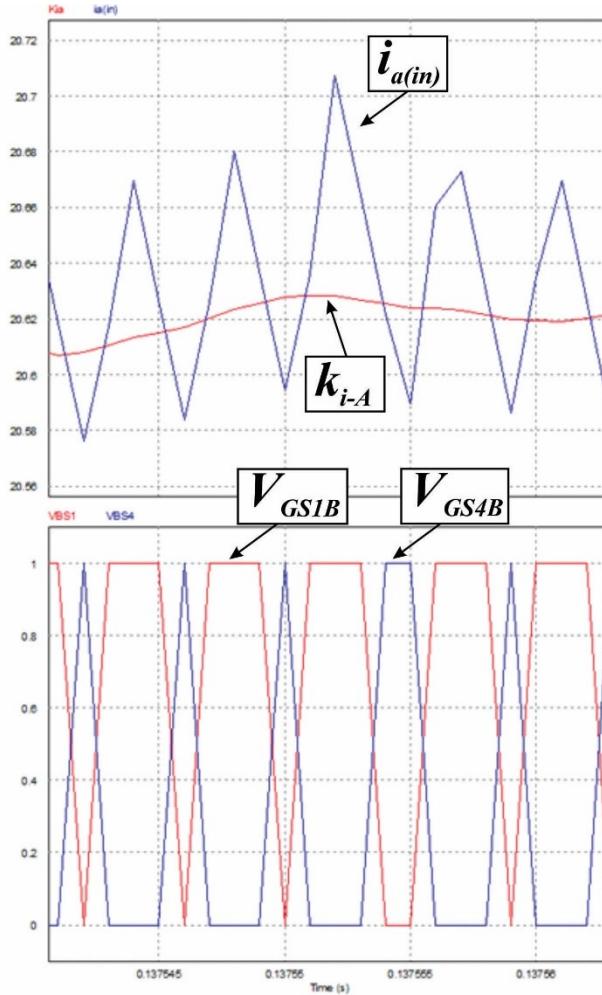

O controle de corrente por histerese por sua vez, baseia-se na comparação entre as correntes de linha de entrada  $i_{a(in)}$ ,  $i_{b(in)}$  e  $i_{c(in)}$  do RHT, obtidas a partir de sensores de corrente, e as referências finais de corrente  $i_{Ref-A}$ ,  $i_{Ref-B}$  e  $i_{Ref-C}$ , respectivamente [18]. Essa comparação dá origem aos sinais de大门  $V_{GS4B}$ ,  $V_{GS5B}$  e  $V_{GS6B}$  que são enviados às chaves  $S_{4B}$ ,  $S_{5B}$  e  $S_{6B}$ , respectivamente. Como o funcionamento dos interruptores do conversor Boost ocorre de forma complementar, os sinais de大门 de  $S_{1B}$ ,  $S_{2B}$  e  $S_{3B}$  ( $V_{GS1B}$ ,  $V_{GS2B}$  e  $V_{GS3B}$ ) são gerados aplicando-se uma lógica *not* nos sinais de大门  $V_{GS4B}$ ,  $V_{GS5B}$  e  $V_{GS6B}$ , respectivamente, conforme referência ilustrativa da Figura 20.

Portanto, tomando como exemplo o controle da corrente da fase A, caso a referência  $i_{Ref_A}$  seja maior que a corrente  $i_{a(in)}$ , nível alto de pulso é enviado para a chave  $S_{4B}$  e nível baixo de pulso é enviado para a chave  $S_{1B}$ . Caso o contrário ocorra, nível baixo de pulso é enviado para a chave  $S_{4B}$  e nível alto de pulso é enviado para a chave  $S_{1B}$ . Os controles das correntes drenadas pelas outras fases seguem a mesma analogia.

Figura 20 Lógica de variação dos sinais de gatilho dos interruptores S1B e S4B do conversor Boost por Histerese.

Fonte: (RODRIGUES, 2016).

### B. Princípio de Funcionamento do PLL

Tomando como exemplo a fase A, a Figura 21 demonstra o esquema de implementação do PLL. O sinal de saída do PLL ( $i_{sen-A}^*$ ) é gerado a partir do cálculo do seno de uma onda dente-de-serra ( $V_{DS}$ ). O valor da frequência da onda dente-de-serra define a frequência do sinal senoidal de saída. Portanto, para que  $i_{sen-A}^*$  apresente uma frequência de 60 Hz, é necessário configurar  $V_{DS}$  para esta mesma frequência.

Figura 21 Diagrama esquemático do PLL implementado para a fase A.

Fonte: (RODRIGUES, 2016).

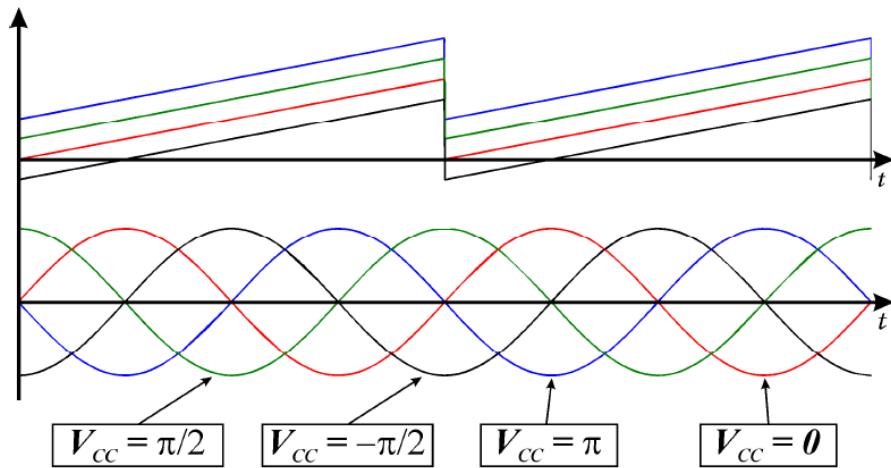

A mudança na fase  $i_{sen-A}^*$  dependerá da inclusão de um nível CC ( $V_{CC}$ ) em  $V_{DS}$ . A presença de um nível CC com valor positivo define que o seno de  $V_{DS}$  apresente um avanço de fase e um nível CC com valor negativo define que o seno de  $V_{DS}$  apresente um atraso de fase, conforme ilustrado na Figura 22.

Figura 22 Relação entre o nível CC da onda dente-de-serra e a fase da senóide de saída do PLL.

Fonte: (RODRIGUES, 2016).

A proporcionalidade entre o sinal  $V_{CC}$  adicionado a  $V_{DS}$  e a fase de  $i_{sen-A}^*$  será utilizada para controlar o sinal de saída do PLL, adiantando ou atrasando a referência senoidal de forma a sincroniza-la em fase com a tensão de fase.

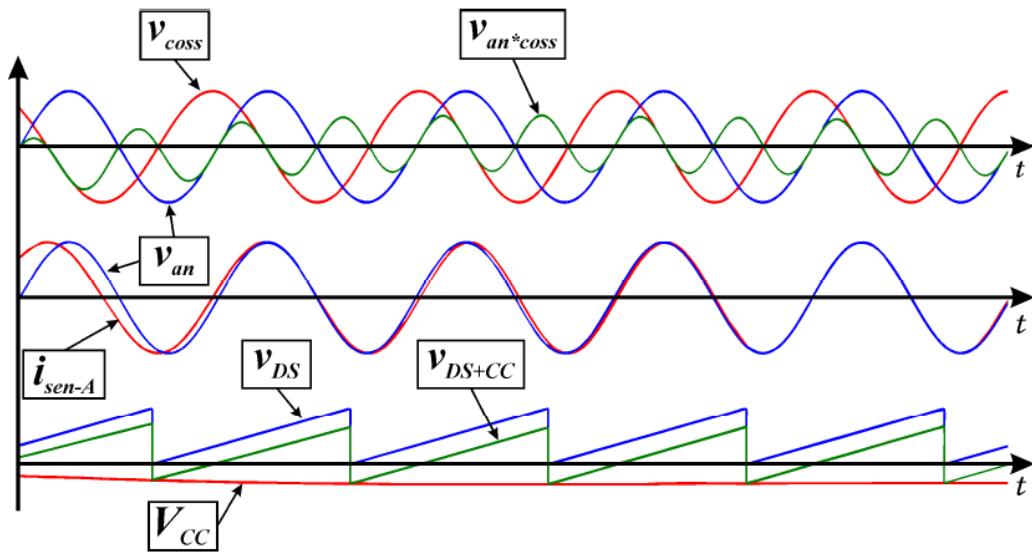

O sinal  $V_{CC}$  é gerado através da ação de um controlador proporcional integral (PI), cuja entrada é o resultado da saída de um filtro passa-baixa. Este filtro é projetado de forma a obter o valor médio do seu sinal de entrada, sendo este composto pelo produto de um sinal cossenoidal ( $V_{coss}$ ) com o sinal correspondente à amostra da tensão de fase  $v_{an}$  com amplitude reduzida, conforme demonstrado na Figura 23.

Figura 23 Representação dos sinais internos gerados na implementação do PLL.

Fonte: (RODRIGUES, 2016).

Uma vez que o controlador PI opera buscando gerar uma saída de modo a tornar sua entrada nula e que o resultado da multiplicação de duas senóides somente apresentará valor médio nulo se estas senóides forem defasadas de  $90^\circ$  uma da outra, o controlador PI trabalhará de forma a gerar o sinal  $V_{CC}$  que somado à  $V_{DS}$  resulte no sinal  $V_{DS+CC}$  cujo cosseno é defasado de  $90^\circ$  da tensão de fase  $v_{an}$ . Portanto, o seno de  $V_{DS+CC}$  resultará em um sinal em fase com a tensão de alimentação, dando origem à referência  $i_{sen-A}^*$ . Vale salientar que o sinal  $V_{DS}$  é ajustado para atingir o valor máximo de  $2\pi$  no final de seu período, garantindo uma variação de  $0^\circ$  a  $360^\circ$  no ângulo da senóide que define a referência senoidal  $i_{sen-A}^*$ .

O princípio de funcionamento dos PLLs das fases B e C é análogo ao apresentado para a fase A.

### C. Projeto dos Controladores

Para o projeto destes controladores, optou-se por seguir três passos: (i) Modelagem matemática e representação no Espaço de Estados; (ii) Utilização de um método de integração para solução do modelo matemático; e (iii) Solução do modelo matemático para os conversores operando em malha aberta. Todos estes passos são descritos na tese apresentada em [27].

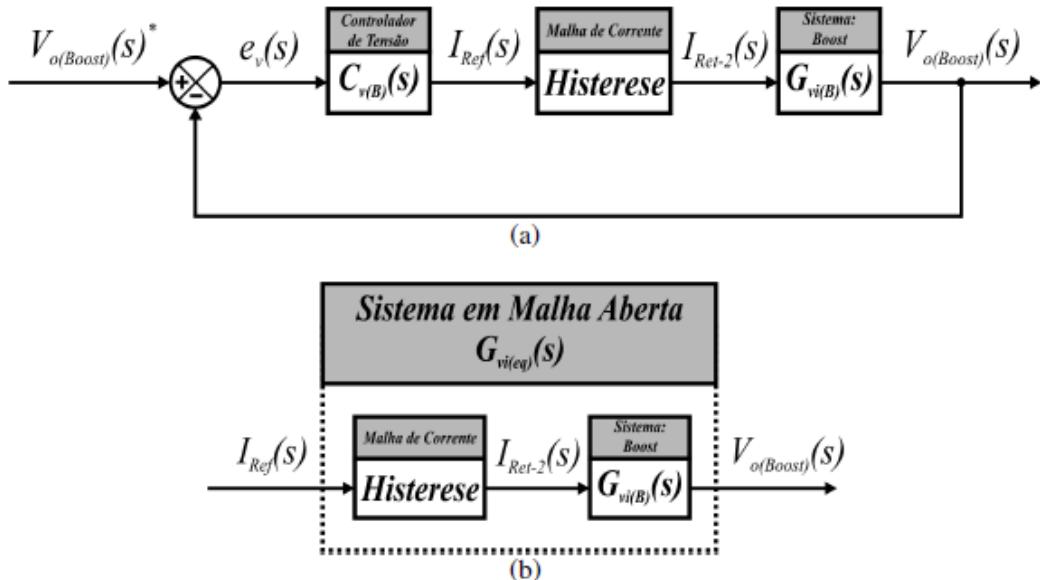

O diagrama de blocos do sistema equivalente do conversor Boost por Histerese pode ser representado através da Figura 24, o qual permite projetar o controlador de tensão com base na análise da função de transferência equivalente do sistema em malha aberta  $G_{vi(eq)}(S)$ . Esta função relaciona a tensão controlada no capacitor de saída do conversor Boost ( $V_{o(Boost)}(S)$ ) –

variável controlada) com a manipulação das amplitudes das correntes de linha  $i_{a(Ret-2)}$ ,  $i_{b(Ret-2)}$  e  $i_{c(Ret-2)}$  impostas na entrada do conversor Boost a partir da variação das amplitudes das referências senoidais de corrente  $i_{Ref-A}$ ,  $i_{Ref-B}$  e  $i_{Ref-C}$  ( $I_{Ref}(S)$  – variável manipulada).

Figura 24 Diagrama de blocos do sistema equivalente do conversor Boost com controle por Histerese: (a) em malha fechada e (b) em malha aberta.

Fonte: (RODRIGUES, 2016).

Definindo-se as variáveis manipuladas e controladas do sistema em malha aberta do conversor Boost, para a solução do modelo matemático e o consequente projeto do controlador de tensão, considerou-se o circuito apresentado na Figura 25 como sistema de análise. Após isto, foram verificadas as condições dos interruptores do circuito e levantadas as equações diferenciais que definem o comportamento do conversor.

Assim, as variáveis manipulada e controlada do sistema do conversor Boost, implementou-se um algoritmo na plataforma do software Matlab® responsável por realizar o método de integração trapezoidal e desenvolver a solução do modelo matemático do conversor Boost operando em malha aberta, conforme apresentado no Apêndice A da tese apresentada em [27].

Uma vez estabelecidas as condições que determinam a utilização das matrizes de sistema e de entrada, estabeleceu-se uma série de condições e verificou-se o comportamento da resposta da tensão no capacitor de saída do conversor, mediante a um degrau de amplitude. A Figura 26 ilustra o comportamento da resposta transitória da tensão no capacitor de saída do conversor Boost no instante da execução do degrau de amplitude das referências de corrente.

Percebe-se que a resposta do sistema em malha aberta apresenta uma característica bastante amortecida, podendo ser equiparada à resposta de um sistema de controle de primeira ordem.

Figura 25 Execução da solução do modelo matemático do conversor Boost por Histerese para o degrau nas amplitudes das referências de corrente.

Fonte: (RODRIGUES, 2016).

Considerando a resposta do sistema de primeira ordem, a Figura 26 fornece as informações necessárias para a estimativa da função de transferência do sistema em malha aberta do conversor Boost  $G_{vi(eq)}(S)$ , a qual relaciona a tensão  $V_{o(Boost)}$  com a variação das amplitudes das referências de corrente.