**UNIVERSIDADE FEDERAL DE UBERLÂNDIA

FACULDADE DE ENGENHARIA ELÉTRICA

PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA**

**NEI OLIVEIRA DE SOUZA**

**INVERSOR DE TENSÃO COM CONTROLADOR DE AÇÃO

REPETITIVA E “PD-FEEDFORWARD” EMBARCADO EM FPGA**

**UBERLÂNDIA

2018**

**NEI OLIVEIRA DE SOUZA**

**INVERSOR DE TENSÃO COM CONTROLADOR DE AÇÃO

REPETITIVA E “PD-FEEDFORWARD” EMBARCADO EM FPGA**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Uberlândia, como requisito parcial à obtenção do título de Mestre em Ciências.

Orientador: Prof. Dr. Ernane Antônio Alves Coelho

**UBERLÂNDIA

2018**

Dados Internacionais de Catalogação na Publicação (CIP)

Sistema de Bibliotecas da UFU, MG, Brasil.

---

S729i

2018

Souza, Nei Oliveira de, 1965-

Inversor de tensão com controlador de ação repetitiva e “PD-FEEDFORWARD” embarcado em FPGA / Nei Oliveira de Souza. - 2018.

91 f. : il.

Orientador: Ernane Antônio Alves Coelho.

Dissertação (mestrado) - Universidade Federal de Uberlândia,

Programa de Pós-Graduação em Engenharia Elétrica.

Disponível em: <http://dx.doi.org/10.14393/ufu.di.2018.285>

Inclui bibliografia.

1. Engenharia elétrica - Teses. 2. Field programmable gate arrays - Teses. 3. Inversores elétricos - Teses. I. Coelho, Ernane Antônio Alves. II. Universidade Federal de Uberlândia. Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

---

CDU: 621.3

Maria Salete de Freitas Pinheiro – CRB6/1262

**NEI OLIVEIRA DE SOUZA**

**INVERSOR DE TENSÃO COM CONTROLADOR DE AÇÃO REPETITIVA E “PD-FEEDFORWARD” EMBARCADO EM FPGA**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Uberlândia, como requisito parcial à obtenção do título de Mestre em Ciências.

Uberlândia, 02 de março de 2018.

**BANCA EXAMINADORA**

---

Prof. Dr. Ernane Antônio Alves Coelho – UFU

Orientador

---

Prof. Dr. Henrique José Avelar – CEFET MG

Banca externo

---

Prof. Dr. Gustavo Brito de Lima – UFU

Banca interno

---

Prof. Dr. Igor Santos Peretta – UFU

Banca interno

## **Dedicatória**

*Aos que torcem por mim em todos esses anos – minha família: Adriana, Nei Jr., Mariana e Ana Carolina – e que sofrem as consequências dos meus sucessos ou fracassos.*

*À minha mãe, por ter me possibilitado a existência e me permitido estudar, com toda a dificuldade que os despossuídos têm.*

*Aos meus irmãos Otaniel e Auta, e in memoriam ao Neiri, Rosângela e Júlio Souza.*

*Aos primos Paulo César Firmino e Carlos Antônio de Oliveira.*

*Aos amigos in memoriam Maria Aparecida Borges Riemslag e Wilhelmus Antonius Maria Riemslag.*

*Aos colegas de escola que não tiveram como terminar esta jornada da vida e ficaram pelo caminho, não porque morreram, mas por falta de oportunidade. Neste modo como vivemos, a chance de chegar à faculdade é definida pela condição socioeconômica. Assim, os mais abastados serão “doutores” e os outros, tudo, menos doutores. Claro, existem exceções de ambos os lados. Mas a regra é geral. Assim, dedico aos colegas dos primeiros anos de escola e do ensino noturno, que não conheço nenhum que chegou a terminar o ensino fundamental. Mas, neste conjunto, os tenho encontrado pela vida nas mais diversas profissões: Vendedor do Triângulo da Sorte, vendedor de Consórcio Primo Rossi, Eletricista de autos, Faxineiras, Segurança, Pizzaiolo, Feirante, Pintor, Carteiro, Telefonista. E os que morreram: o Luiz, alcoólatra; Gilmar, drogas; Alemão, drogas...*

*VIVA A MERITOCRACIA!*

## Agradecimentos

Agradeço a todos que, direta ou indiretamente, contribuiriam para a realização desta pesquisa: das faxineiras, que me propiciaram um ambiente limpo, aos doutores, com quem troquei ideias e que me incentivaram. Provavelmente devo esquecer alguém, já que são muitos e ninguém faz nada sozinho; que me perdoem os esquecidos.

Agradeço em especial a minha esposa Adriana, pelo companheirismo ao longo dos anos, a minhas filhas Mariana e Ana Carolina e meu filho Nei Júnior, e à Conceição Leal, pela compreensão e apoio.

Agradeço à Faculdade de Engenharia Elétrica, na pessoa de seus diretores, pela oportunidade que me foi dada ao longo dos anos, me possibilitando fazer o curso de Engenharia Elétrica e o mestrado. Dentre os diretores, não posso deixar de destacar dois: Renato Alves Pereira, que me deu apoio no curso de graduação, e Marcelo Lynce Ribeiro, que me deu apoio na pós-graduação.

Agradeço aos professores, são todos merecedores, mas em especial ao Prof. João Batista Vieira Júnior, pelo apoio e por acreditar em mim, e ao Prof. Ernane Antônio Alves Coelho, por aceitar ser meu orientador por duas vezes, por me ajudar a superar este grande desafio, por ser humilde, justo e amigo.

Ao amigo Edgard Afonso Lamunier, por me acompanhar ao longo desses anos, me orientado em todas as dificuldades.

Aos técnicos Carlinho, Rubinho, Hélio, Rafael, Hermano e Claudemir.

Às secretárias, em especial à Marcília.

Ao NUPEP, pelo apoio, e a todos os colegas e amigos da pós-graduação, especialmente a Eric Chaves, Fernando Rocha, Henrique Carvalho e Leandro Vilefort.

## **Perguntas de um operário letrado**

Quem construiu Tebas, a das sete portas?

Nos livros vem o nome dos reis,

Mas foram os reis que transportaram as pedras?

Babilónia, tantas vezes destruída,

Quem outras tantas a reconstruiu? Em que casas

Da Lima Dourada moravam seus obreiros?

No dia em que ficou pronta a Muralha da China para onde

Foram os seus pedreiros? A grande Roma

Está cheia de arcos de triunfo. Quem os ergueu? Sobre quem

Triunfaram os Césares? A tão cantada Bizâncio

Só tinha palácios

Para os seus habitantes? Até a legendária Atlântida

Na noite em que o mar a engoliu

Viu afogados gritar por seus escravos.

O jovem Alexandre conquistou as Índias

Sozinho?

César venceu os gauleses.

Nem sequer tinha um cozinheiro ao seu serviço?

Quando a sua armada se afundou Filipe de Espanha

Chorou. E ninguém mais?

Frederico II ganhou a guerra dos sete anos

Quem mais a ganhou?

Em cada página uma vitória.

Quem cozinhava os festins?

Em cada década um grande homem.

Quem pagava as despesas?

Tantas histórias

Quantas perguntas

Bertolt Brecht

## **Resumo**

A pesquisa desenvolvida é sobre a aplicação do uso da FPGA na área de Eletrônica de Potência. Desenvolveu-se um controle para inversor de tensão CC/CA monofásico com filtro de saída LC controlado por PWM senoidal unipolar, tendo como carga um retificador não controlado. O controle implementado, o qual integra as ações de controle repetitiva e PD-Feedforward, foi todo embarcado em FPGA, assim como as funções de geração de tensão de referência, geração de portadora triangular e PWM digital, comparador digital para proteção e operações matemáticas em ponto fixo do tipo multiplica e acumula para as funções digitais. Uma parte das funções foi implementada por meio de *software* com alto nível de abstração, e outra parte foi implementada em baixo nível, através de linguagem de descrição de *hardware*. A pesquisa visa mostrar a viabilidade da aplicação das FPGAs em Eletrônica de Potência, como uma alternativa aos DSPs, para o controle de conversores, realizando o cálculo das leis de controle em ponto fixo, e não somente para a substituição de circuitos digitais. A pesquisa é inédita para o NUPEP (Núcleo de Pesquisa em Eletrônica de Potência) da Faculdade de Engenharia Elétrica da Universidade Federal de Uberlândia. Portanto é uma pesquisa de início da utilização de FPGA na área de Eletrônica de Potência para o NUPEP.

**Palavras-chave:** FPGA. Controle Repetitivo. Embarcado. System Generator.

## **Abstract**

The research developed herein is based on the applied use of a FPGA to the area of Power Electronics. The authors developed a single-phase DC/CA inverter control with an LC output filter controlled by a unipolar sine wave PWM, which uses as its load a non-controlled rectifier. The implemented control, which integrates the repetitive control actions and PD-Feedforward, was embedded in FPGA, along with the functions of reference voltage generation, triangular carrier generation and digital PWM, digital comparison for protection and mathematical operations in multiple type fixed point and accumulations for digital functions. A part of these functions was implemented through the software using high level abstraction, and the other part was implemented using low level abstraction through the hardware description language. This research study aims at showing the feasibility of applying FPGAs in Power Electronics, as an alternative to DSPs for converter control by performing the calculation for the control laws in fixed point, and not only for the substitution of digital circuits. This is a novel research project here at NUPEP (Núcleo de Pesquisa em Eletrônica de Potência) (Power Electronics research center)) at the electrical engineering faculty of the Federal University of Uberlandia. Therefore, this is an initial research project into the use of FPGA in the area of Power Electronics at NUPEP.

**Keywords:** FPGA. Repetitive control. Embedded. System Generator.

## Lista de Figuras

|                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| Figura 1 - Exemplo dos primeiros circuitos programáveis .....                                                   | 18 |

| Figura 2 - Conceito de FPGA [10] .....                                                                          | 19 |

| Figura 3 – Placa FPGA utilizada .....                                                                           | 23 |

| Figura 4 – Topologia ponte completa .....                                                                       | 26 |

| Figura 5 – Formas de ondas da modulação senoidal PWM .....                                                      | 27 |

| Figura 6 – Formas de ondas de um SPWM Bipolar .....                                                             | 28 |

| Figura 7 - Formas de ondas de um SPWM Unipolar .....                                                            | 29 |

| Figura 8 - Topologia do controle PID .....                                                                      | 30 |

| Figura 9 - Princípio do controle Repetitivo .....                                                               | 31 |

| Figura 10 - Controle Repetitivo Tradicional .....                                                               | 32 |

| Figura 11 - Sistema realimentado .....                                                                          | 33 |

| Figura 12 - Controlador Feedforward .....                                                                       | 34 |

| Figura 13 - Diagrama de controle do inversor com ação de controle instantânea e<br>repetitiva [8] .....         | 35 |

| Figura 14 - Diagrama de Bode da função $G_c(z)$ para $K_1=-0,175$ e $K_2=-0,011$ e<br>$f_s=5000\text{Hz}$ ..... | 36 |

| Figura 15 - Transitório de elevação de carga linear .....                                                       | 38 |

| Figura 16 - Transitório de redução de carga linear .....                                                        | 38 |

| Figura 17 - Desempenho do controlador PD-feedforward para uma carga não linear<br>.....                         | 39 |

| Figura 18 - Desempenho do controlador PD-feedforward + Repetitivo para uma<br>carga não linear .....            | 41 |

| Figura 19 - Gateways .....                                                                                      | 43 |

| Figura 20 - Gateway In .....                                                                                    | 44 |

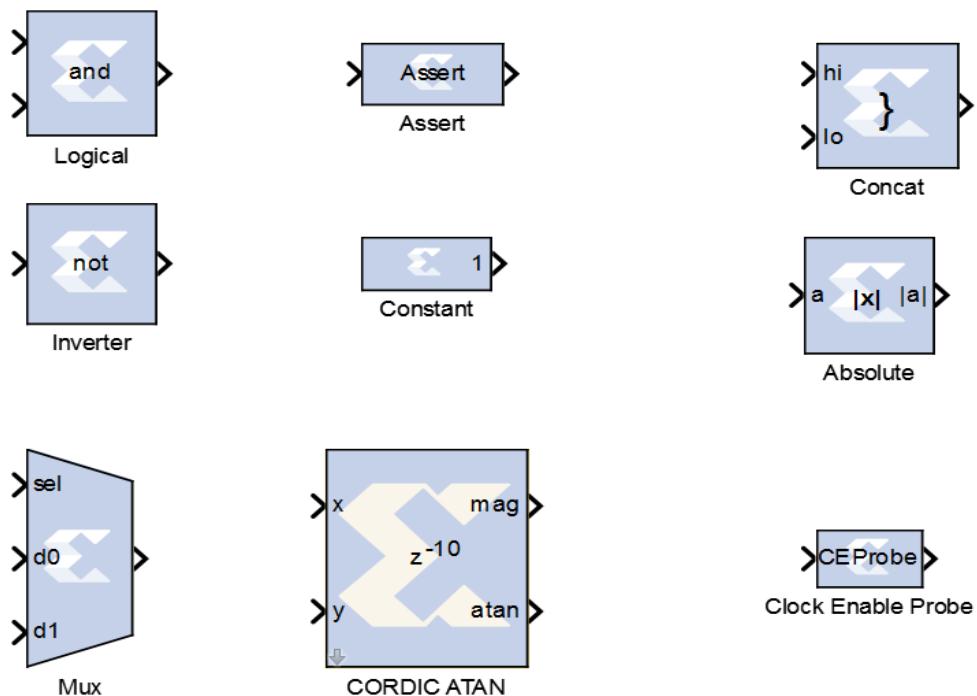

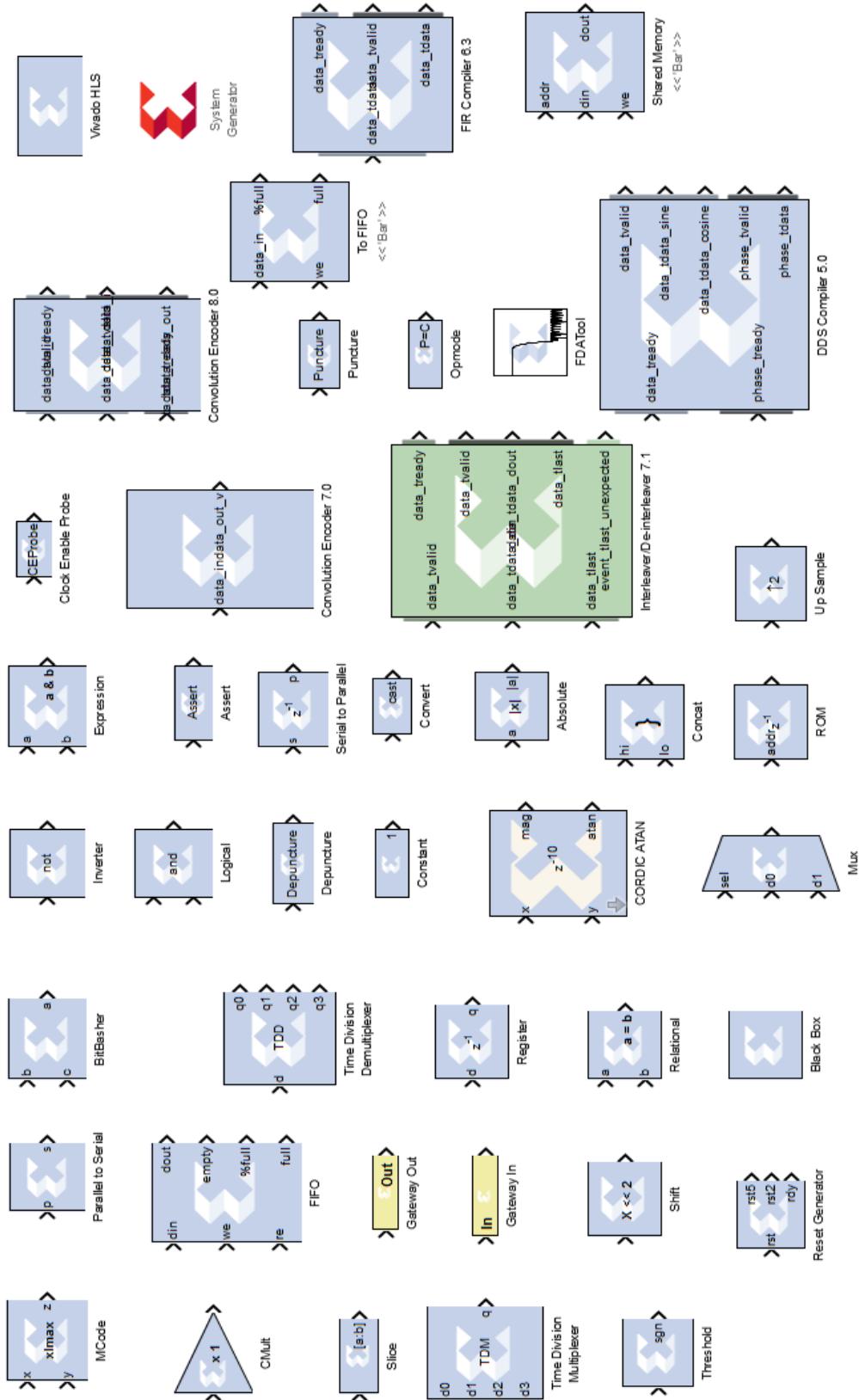

| Figura 21 - Exemplos de primitivas do System Generator .....                                                    | 45 |

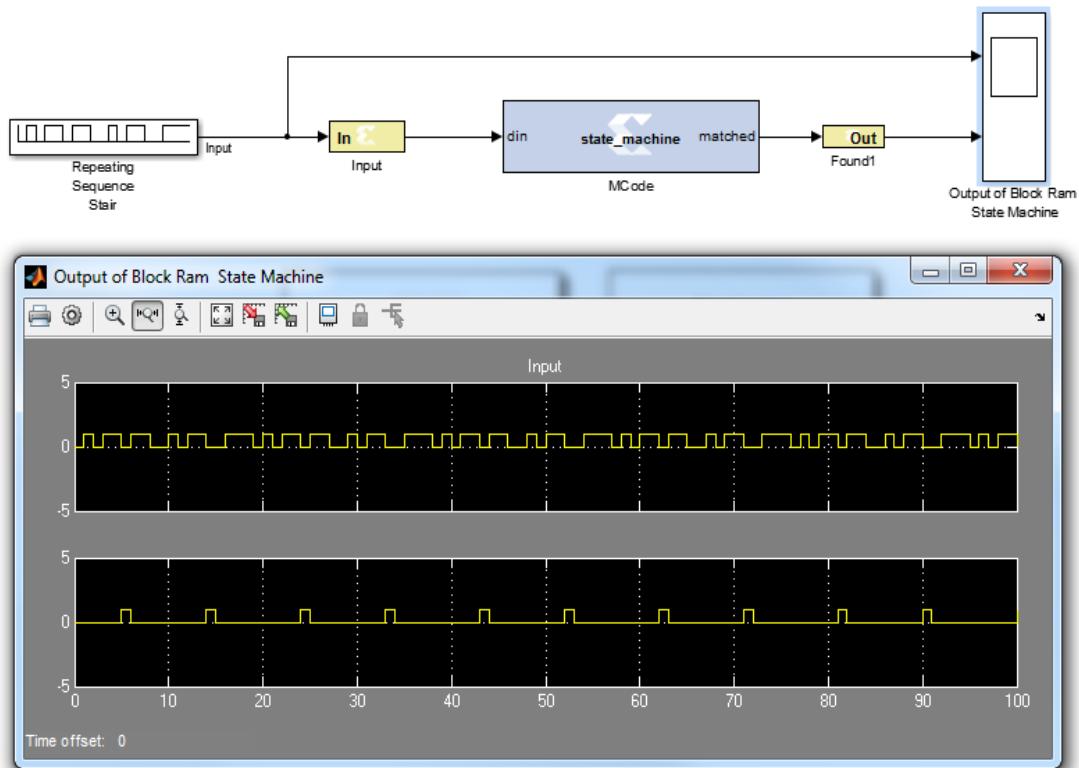

| Figura 22 - Exemplo implementado com o bloco Mcode .....                                                        | 47 |

| Figura 23 - Exemplo do uso do Black box para implementar a função "sample-and-<br>hold" .....                   | 47 |

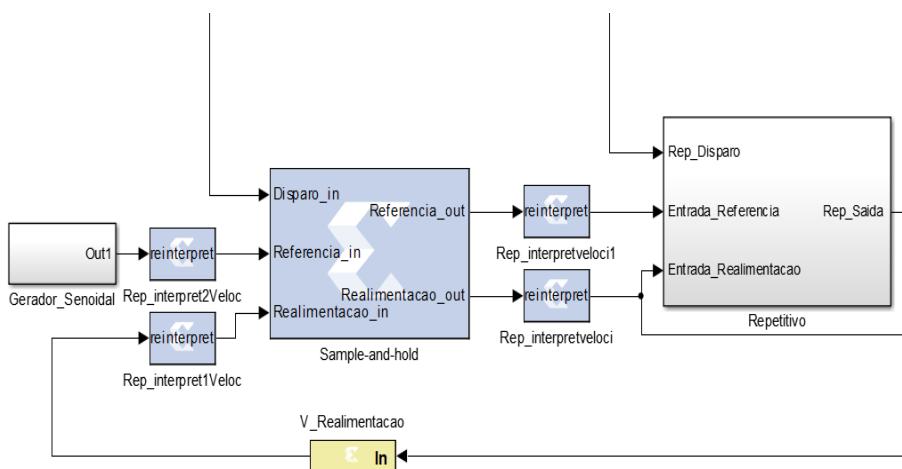

| Figura 24 - Simulação PSIM Controle Repetitivo .....                                                            | 49 |

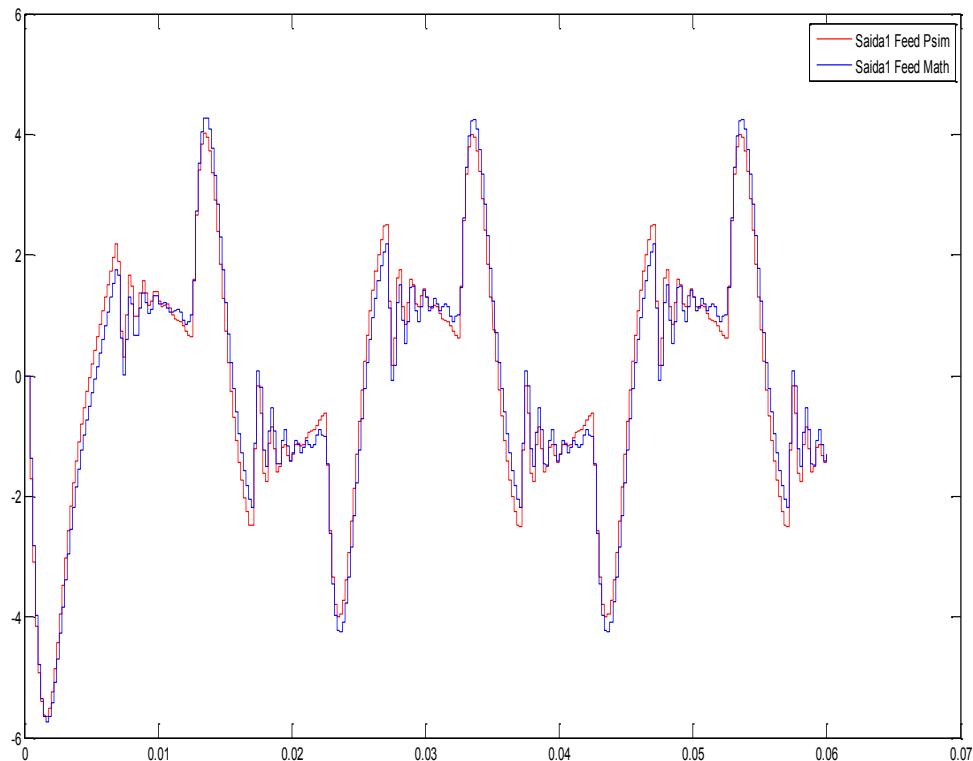

| Figura 25 - Sinal amostrado na saída do controlador <i>PD-feedforward</i> no System<br>generator e Psim .....   | 50 |

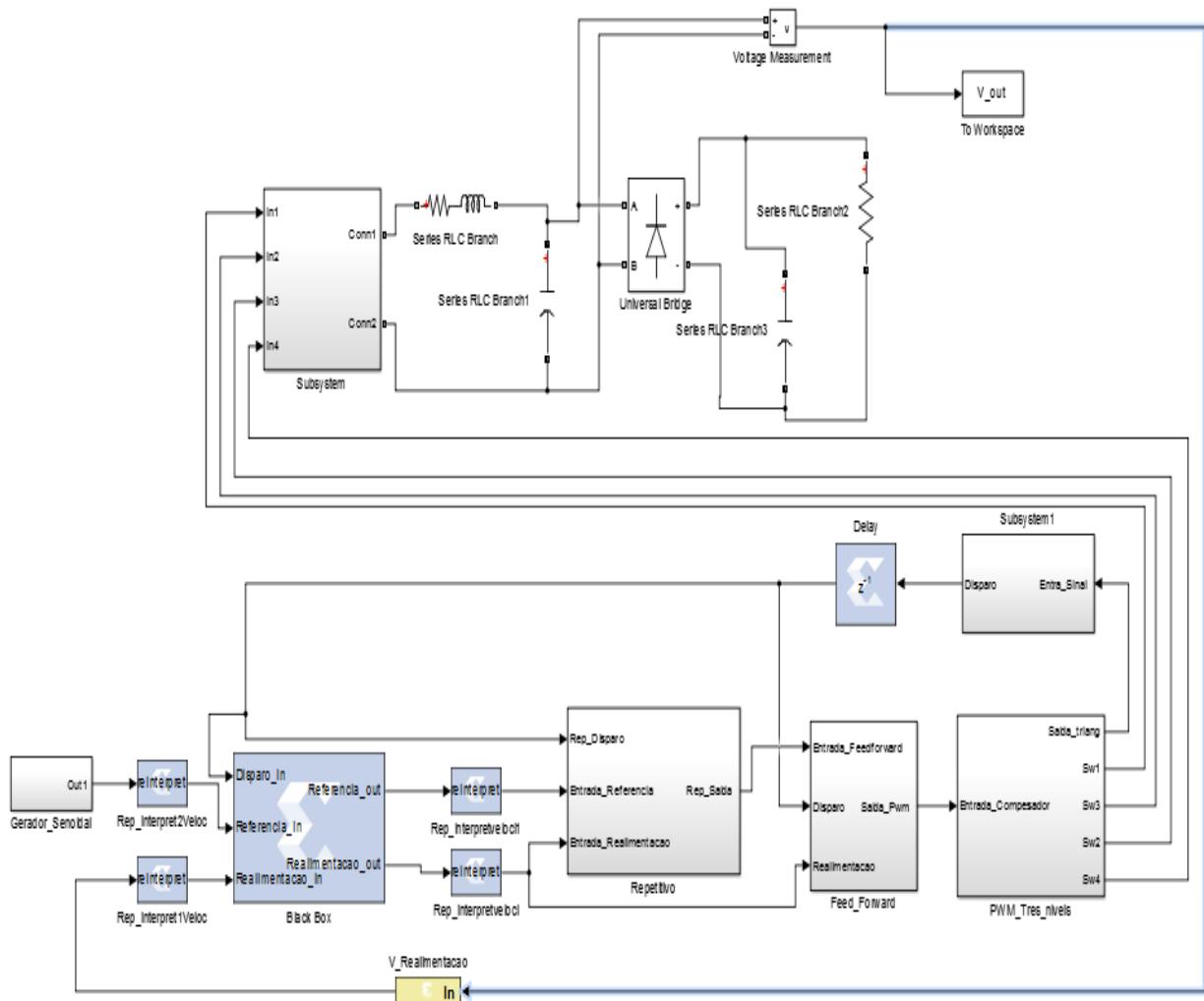

| Figura 26 - Projeto do controlador Repetitivo e <i>PD-feedforward</i> Simulado .....                            | 51 |

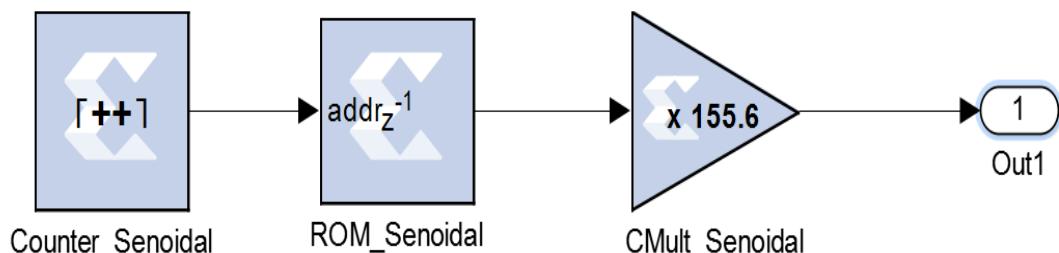

| Figura 27 - Circuito gerador do sinal de referência .....                                                       | 52 |

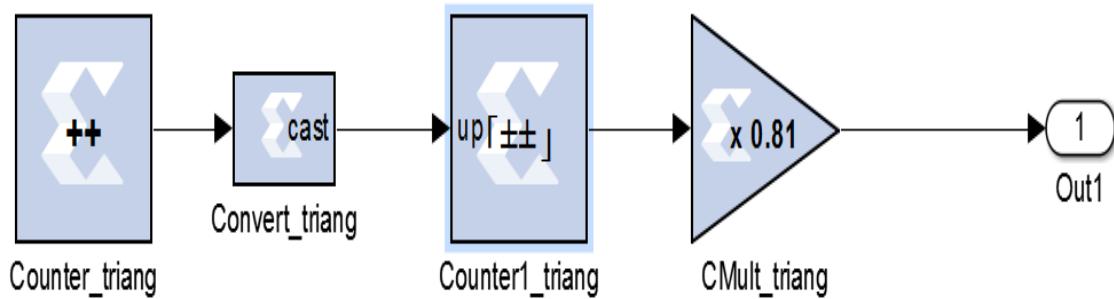

| Figura 28 - Circuito gerado da forma de onda triangular .....                                                   | 53 |

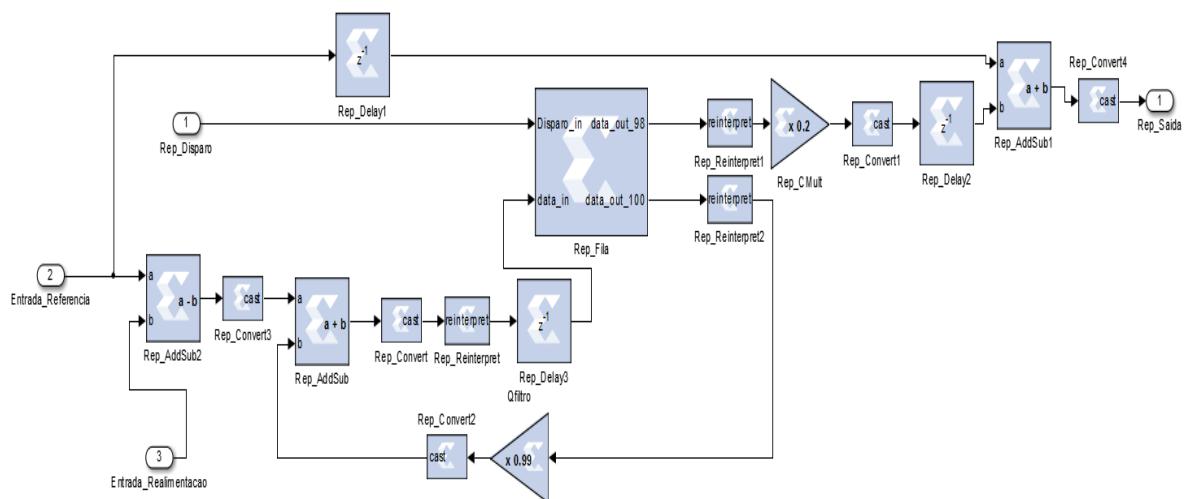

| Figura 29 - Função de transferência do Repetitivo .....                                                         | 53 |

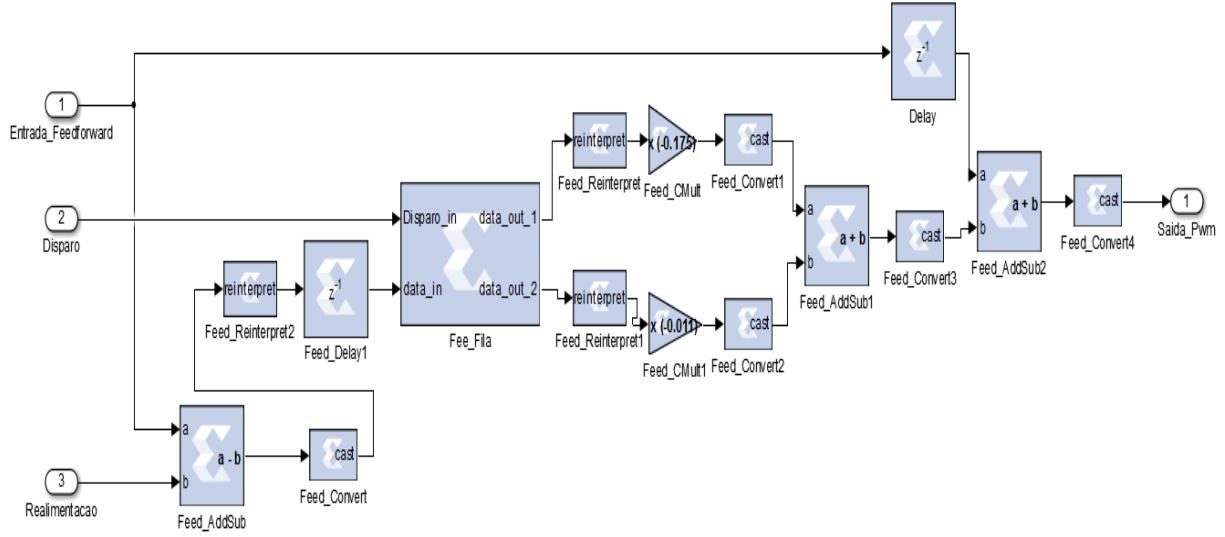

| Figura 30 - Equação de diferenças do <i>PD-feedforward</i> .....                                                | 54 |

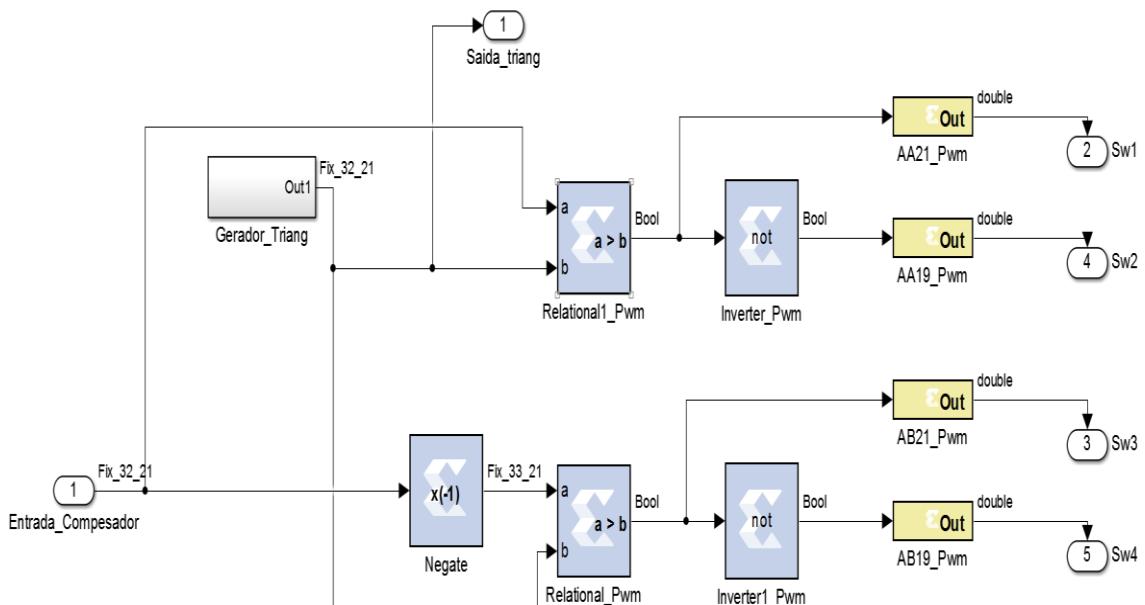

| Figura 31 - Circuito PWM .....                                                                                  | 54 |

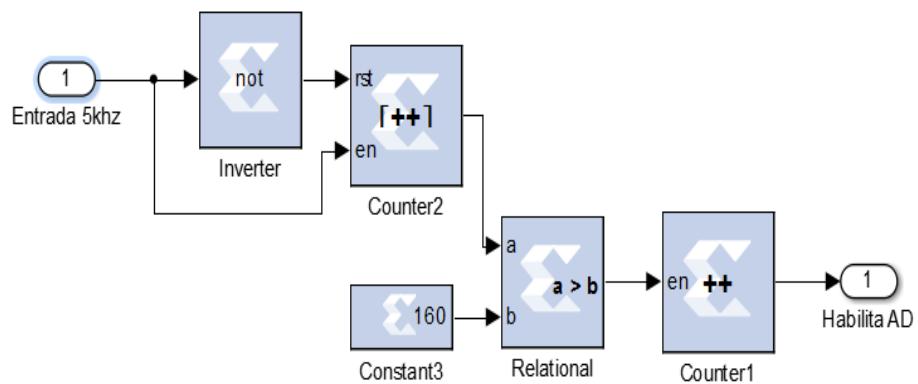

| Figura 32 - Circuito de atraso para aquisição .....                                                             | 56 |

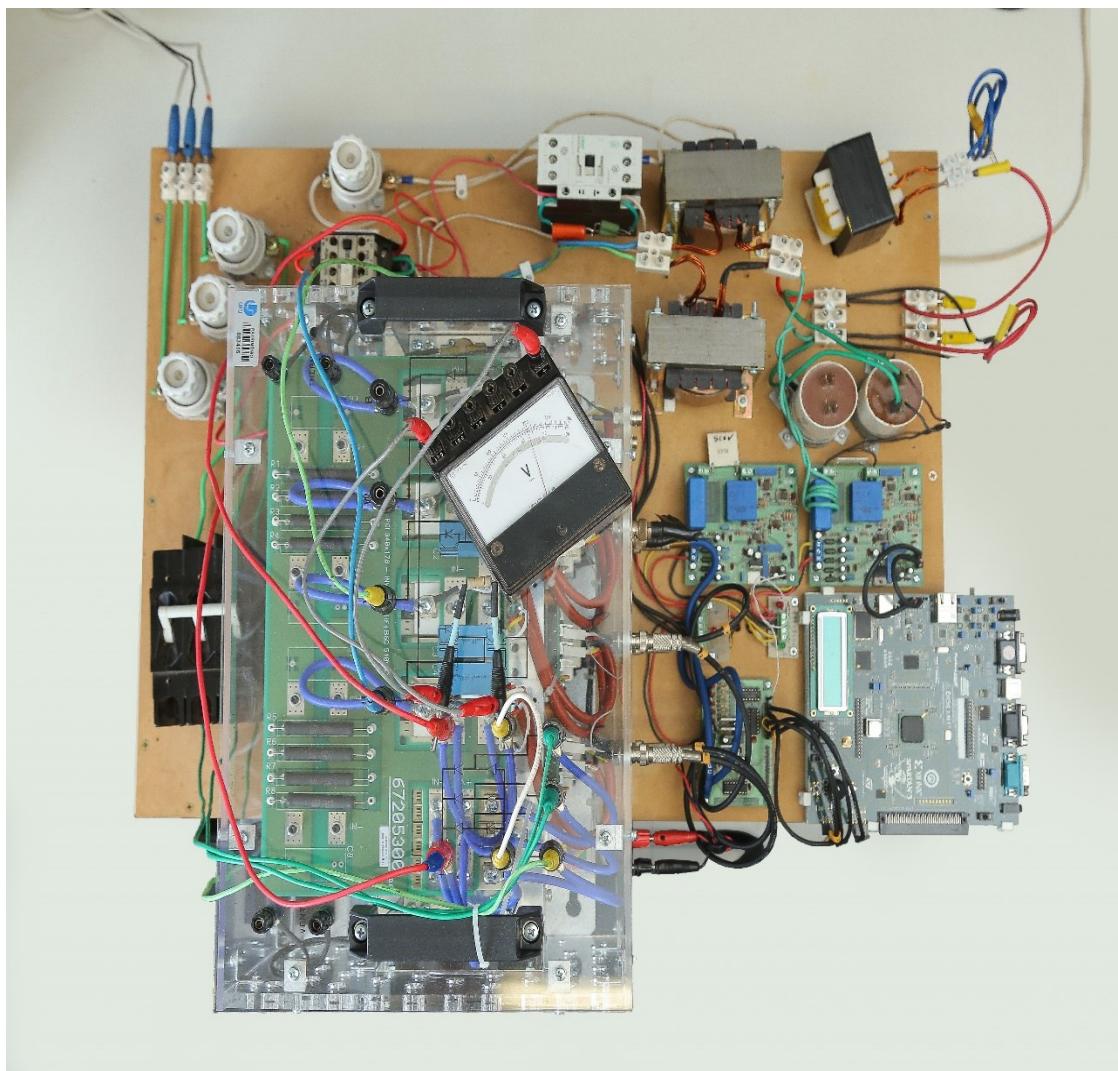

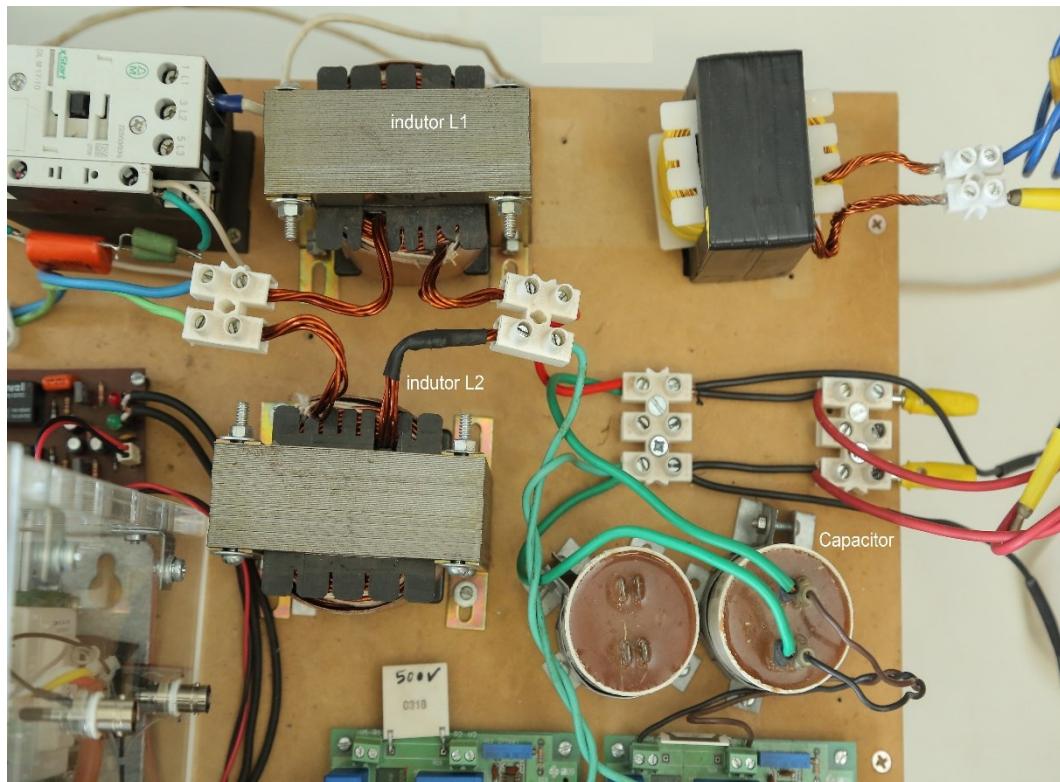

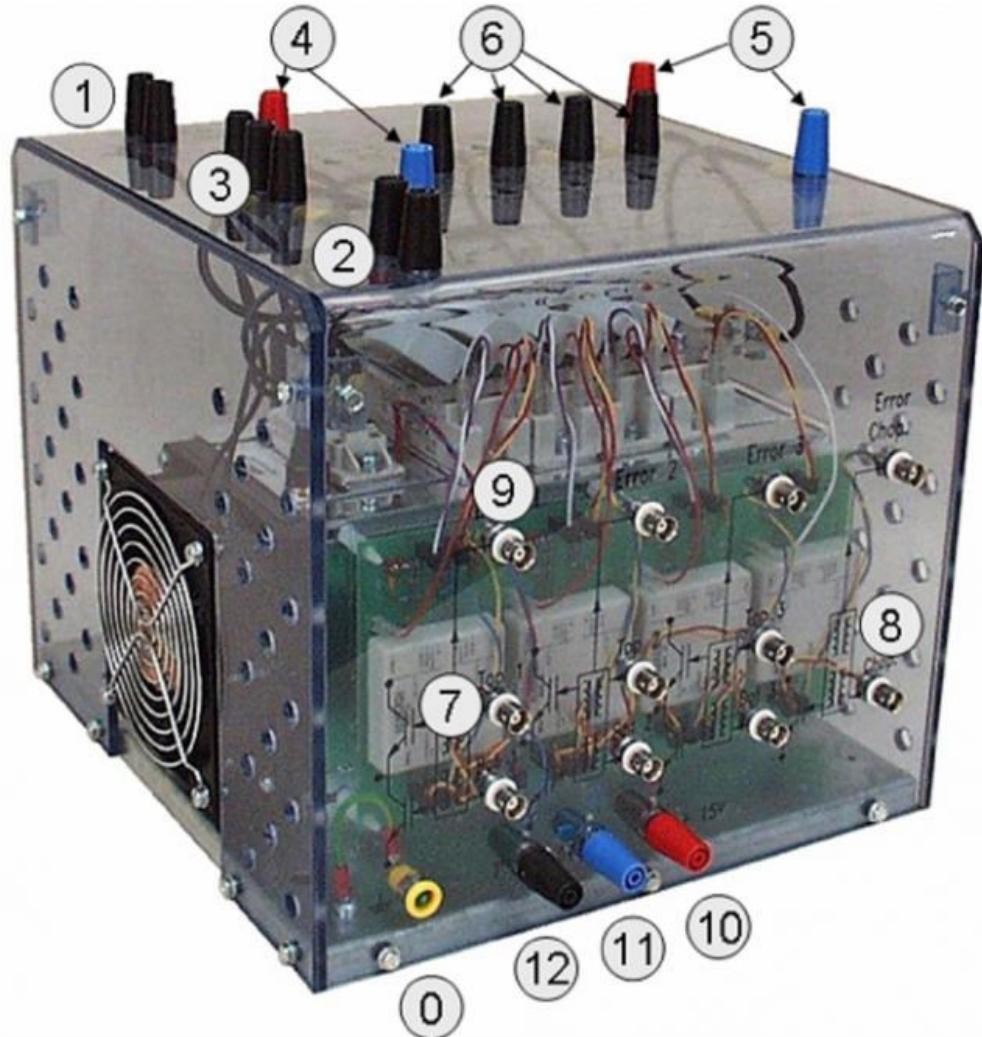

| Figura 33 - Imagem da planta .....                                                                              | 57 |

| Figura 34 - Diagrama de ligação da planta .....                                                                 | 58 |

|                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 35 - Placa de aquisição .....                                                                                                      | 58 |

| Figura 36 - Estágio de regulação e filtragem.....                                                                                         | 59 |

| Figura 37 - Estágio de regulagem: Divisor de tensão gerador do sinal de referência para compensação de <i>offset</i> .....                | 60 |

| Figura 38 - Filtro anti-aliasing .....                                                                                                    | 60 |

| Figura 39 - Estágio somador e gerado de offset .....                                                                                      | 61 |

| Figura 40 - Placa de adequação de tensão entre FPGA e Gate Driver, conectada. .                                                           | 62 |

| Figura 41 - Esquema da ligação da carga.....                                                                                              | 63 |

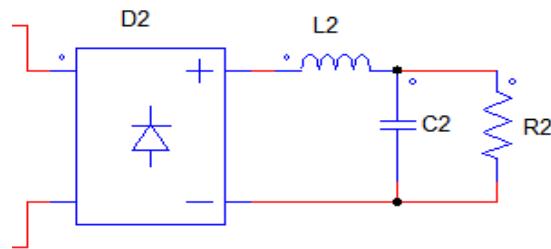

| Figura 42 - Retificador não controlado e capacitor de filtro .....                                                                        | 63 |

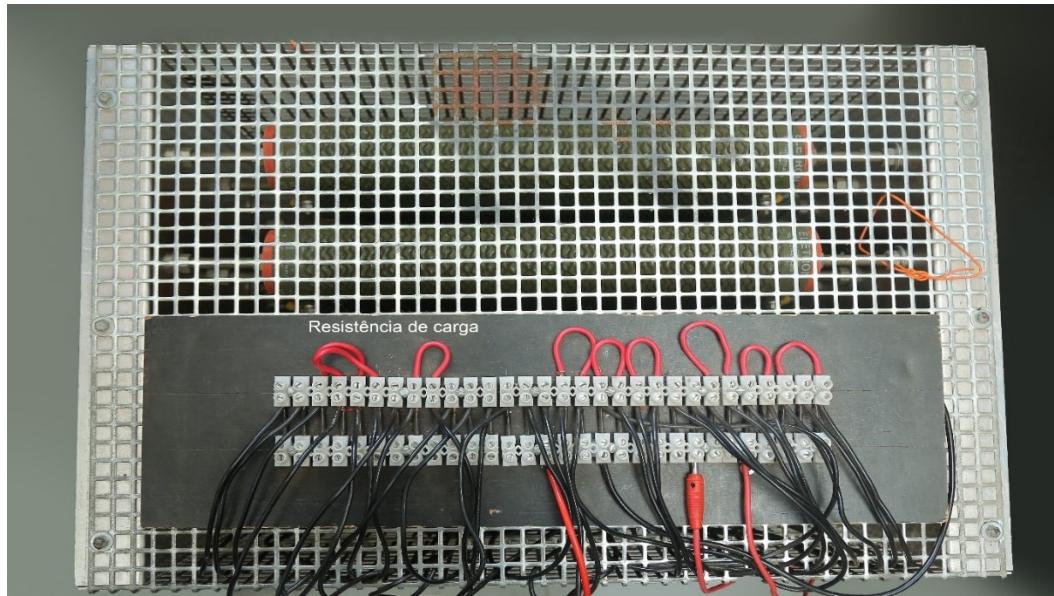

| Figura 43 - Resistência de Carga.....                                                                                                     | 64 |

| Figura 44 - Filtro LC .....                                                                                                               | 65 |

| Figura 45 - Módulo SemiKron.....                                                                                                          | 66 |

| Figura 46 - FPGA e conexão com AD e saída Gate drivers .....                                                                              | 67 |

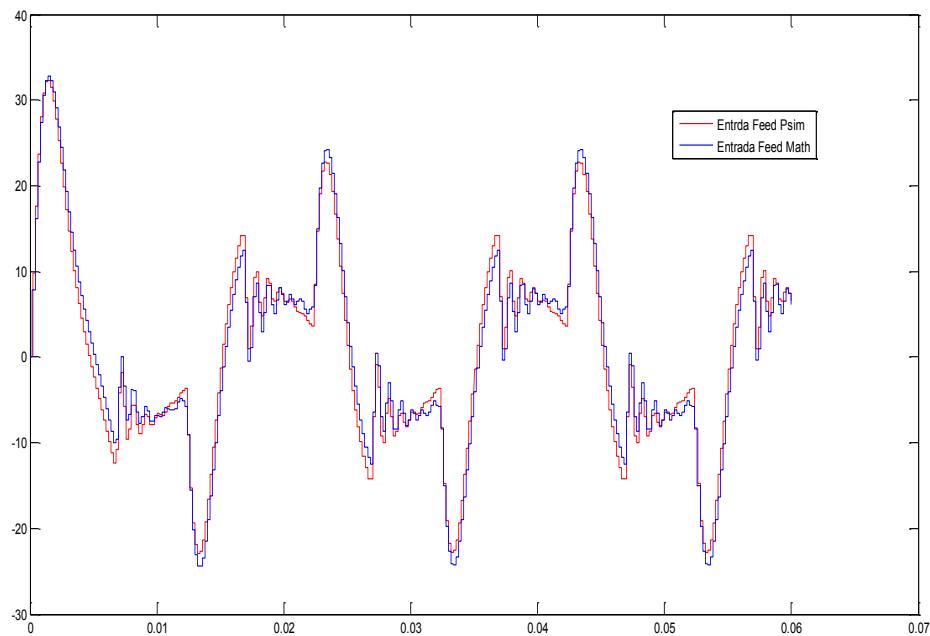

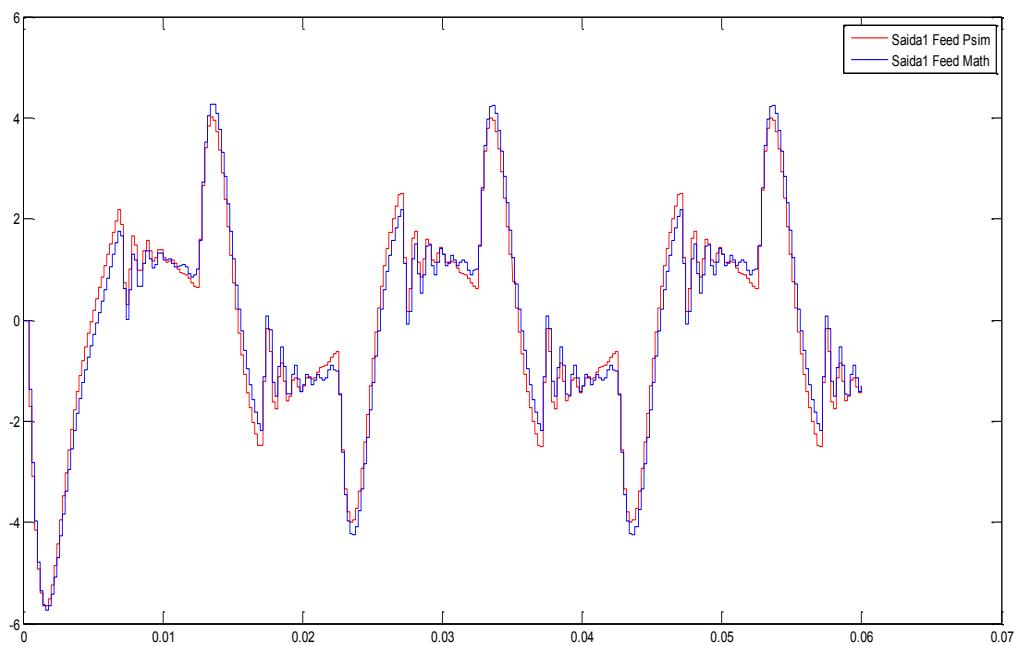

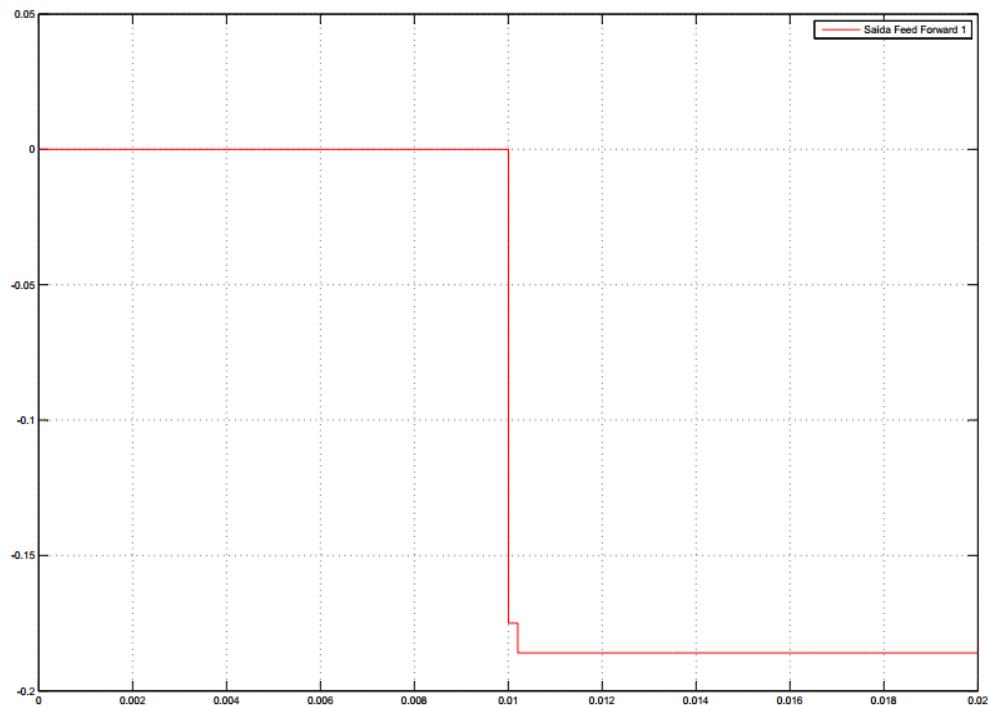

| Figura 47 - Sinais de entrada na função Feed Forward no PSIM e System Generator .....                                                     | 68 |

| Figura 48 - Sinais de saída na função Feed Forward no PSIM e System Generator                                                             | 69 |

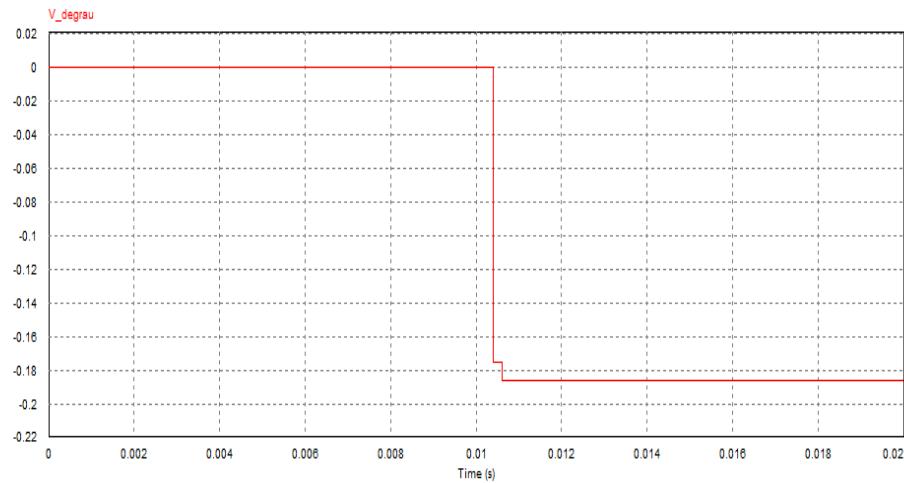

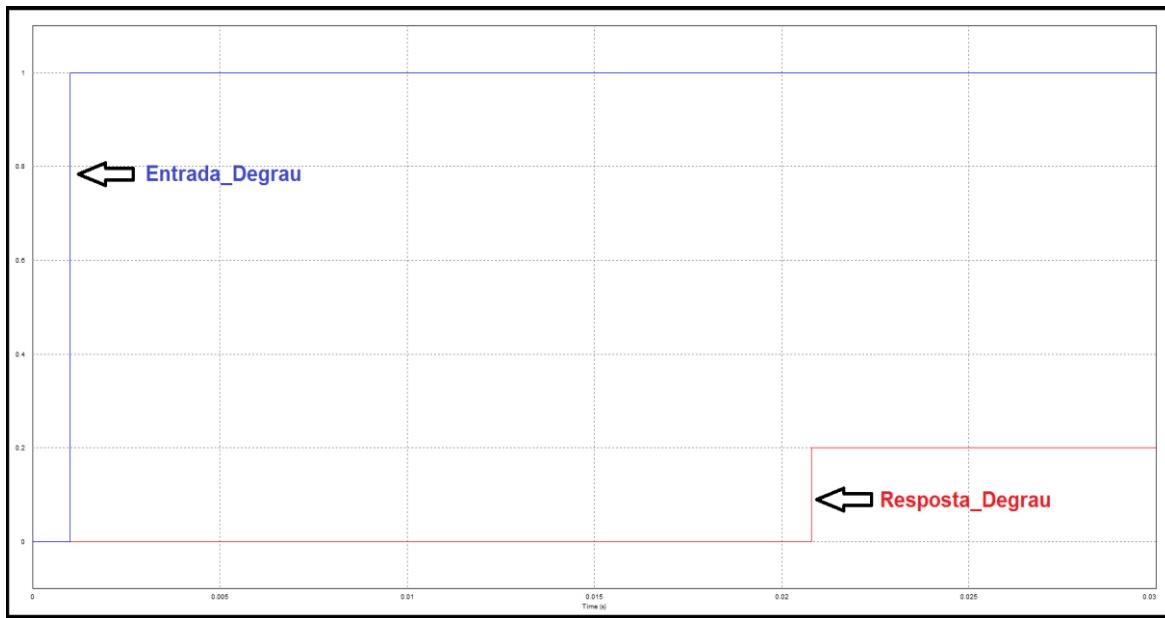

| Figura 49 - Resposta ao Degrau da função de transferência Feed Forward no PSIM .....                                                      | 70 |

| Figura 50 - Resposta ao Degrau da função de transferência Feed Forward no System Generator .....                                          | 70 |

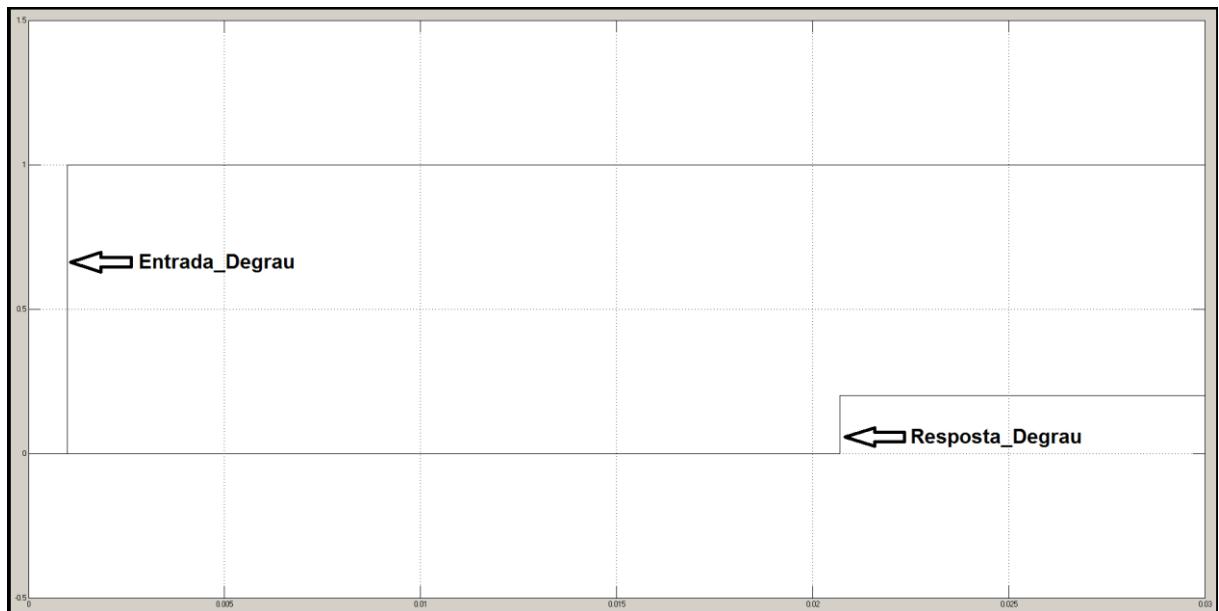

| Figura 51 - Resposta ao degrau no PSIM para a função de transferência Repetitiva .....                                                    | 71 |

| Figura 52 - Resposta ao degrau no System Generator para a função de transferência Repetitiva .....                                        | 71 |

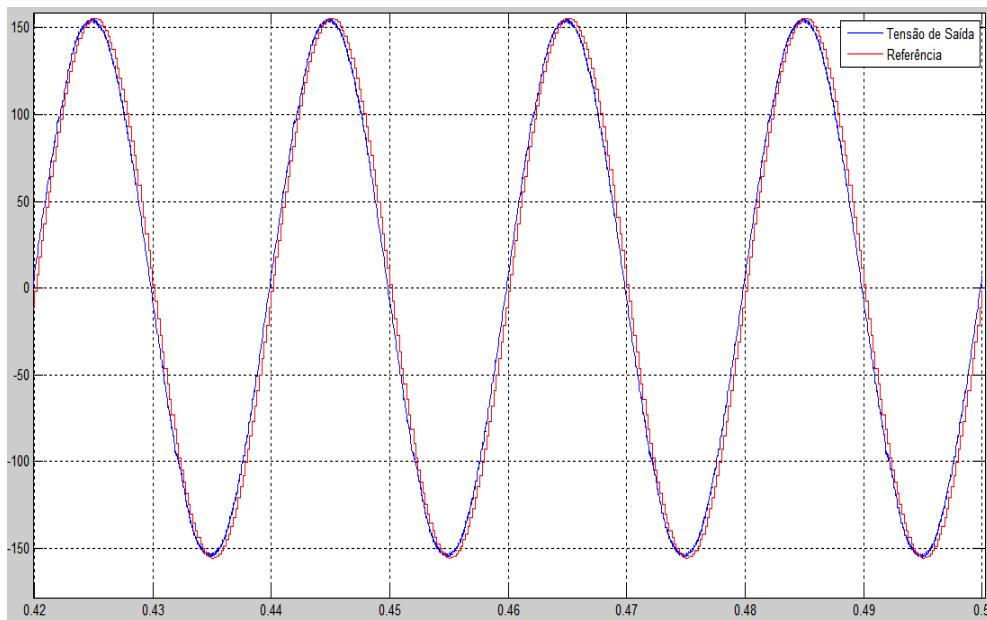

| Figura 53 - Resultado da simulação do controle Repetitivo e PD-feedforward no PSIM com tensão de referência e de saída.....               | 72 |

| Figura 54 - Resultado da simulação no PSIM do controle Repetitivo e <i>PD-feedforward</i> com o sinal de tensão e corrente de saída ..... | 72 |

| Figura 55 - Resultado da referência [8] como colocar a fonte? .....                                                                       | 73 |

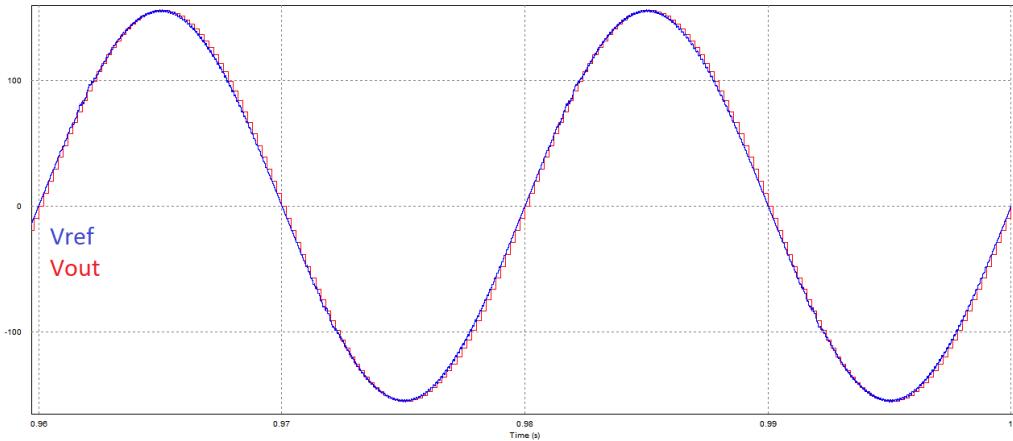

| Figura 56 - Resultado da simulação do controle Repetitivo no System Generator com o sinal de referência e tensão de saída.....            | 74 |

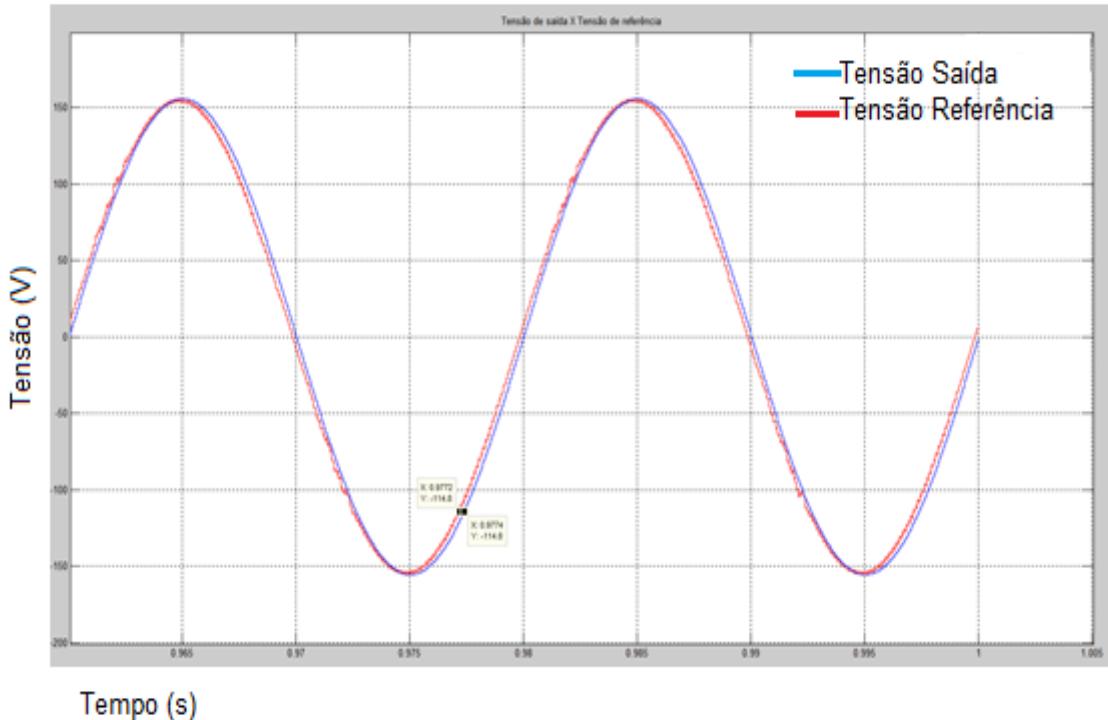

| Figura 57 - Resultado da co-simulação do controle Repetitivo com os sinais de tensão de saída e tensão de referência .....                | 75 |

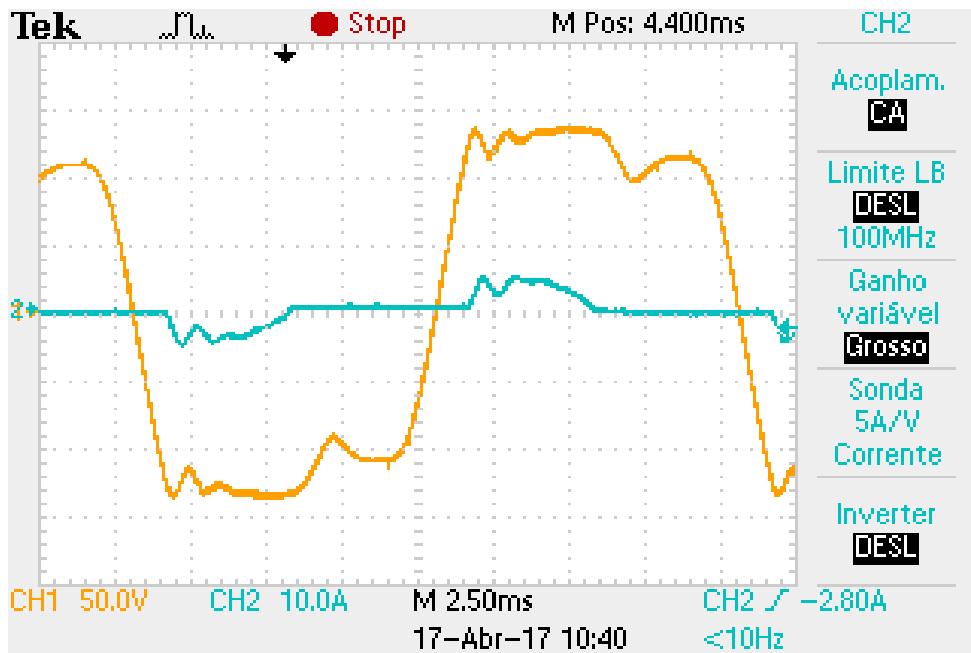

| Figura 58 - Resultado da planta em malha aberta para tensão e corrente de saída.                                                          | 76 |

| Figura 59 - Resultado em malha fechada, controle Repetitivo, tensão e corrente de saída .....                                             | 77 |

| Figura 60 - Espectro harmônico da corrente .....                                                                                          | 78 |

| Figura 61 - Espectro harmônico da tensão de saída .....                                                                                   | 78 |

## **Lista de Tabelas**

|                                                      |    |

|------------------------------------------------------|----|

| Tabela 1 - Parâmetros da simulação Feedforward.....  | 37 |

| Tabela 2 - Parâmetros dos controles Repetitivos..... | 40 |

| Tabela 3 - Parâmetros da carga.....                  | 64 |

| Tabela 4 - Parâmetros da Planta.....                 | 67 |

## Lista de Abreviaturas e Símbolos

|                 |                                                               |

|-----------------|---------------------------------------------------------------|

| A               | Ampère, unidade de corrente elétrica                          |

| A/D             | Analógico para Digital                                        |

| AHDL            | <i>Hardware description language</i> desenvolvida pela Altera |

| AO              | Amplificador Operacional                                      |

| ASIC            | <i>Application Specific Integrated Circuit</i>                |

| C(z)            | Compensador do ramo direto controlador repetitivo             |

| C( $z^{-1}$ )   | Representação no formato DSP de C(z)                          |

| CA              | Corrente alternada                                            |

| CC              | Corrente Continua                                             |

| CC-CA           | Corrente Continua-Corrente Alternada                          |

| CLB             | <i>Configurable Logic Block</i>                               |

| Cr              | Ganho do controlador repetitivo                               |

| d(z)            | Função discreta do distúrbio inerente à planta                |

| DCM             | <i>Direct Clock Manager</i>                                   |

| DSP             | <i>Digital Signal Processor</i>                               |

| e(z)            | Função discreta do erro de tensão                             |

| EDA             | <i>Electronic Design Automation</i>                           |

| FEELT           | Faculdade de Engenharia Elétrica                              |

| FPGA            | <i>Field Programmable Gate Array</i>                          |

| Gc(z)           | Compensador do controlador de ação instantânea                |

| Gd(z)           | Função de transferência do distúrbio                          |

| Gff(z)          | Função Feedforward do controlador de ação instantânea         |

| Gh(z)           | Função de realimentação do controlador de ação instantânea    |

| Gp(z)           | Função de transferência da planta                             |

| Grp( $z^{-1}$ ) | Função de transferência do controle Repetitivo (formato DSP)  |

| HIL             | <i>Hardware-in-loop</i>                                       |

| Hz              | Hertz, unidade de frequência                                  |

| I(s)            | Corrente de entrada do filtro LC                              |

| Io              | Corrente de saída do filtro LC                                |

| IEEE            | <i>Institute of Electrical and Electronics Engineers</i>      |

| IGBTS           | <i>Insulated Gate Bipolar Transistor</i>                      |

| IMC             | <i>Internal Model control</i>                                 |

| JTAG            | <i>Joint Test Action Group</i>                                |

| LC              | <i>Logic Cell</i>                                             |

| LCD             | <i>Liquid Crystal Display</i>                                 |

| LED             | <i>Light Emitting Diode</i>                                   |

| LUTS            | <i>Look-Up Tables</i>                                         |

| LVTTL           | <i>Low Voltage Transistor Transistor Logic</i>                |

| MAC             | <i>Multiply-and-accumulate (DSP instruction)</i>              |

| NUPEP           | Núcleo de Pesquisa em Eletrônica de Potência                  |

|                                   |                                                                     |

|-----------------------------------|---------------------------------------------------------------------|

| P(z)                              | Função discreta da planta                                           |

| PAL                               | <i>Programmable Logic Device</i>                                    |

| PD-Feedforward                    | Proporcional Derivativo <i>Feedforward</i>                          |

| PI                                | Proporcional Integral, controlador                                  |

| PID                               | Proporcional Integral derivado, controlador                         |

| PV                                | <i>Photovoltaic</i>                                                 |

| PWM                               | <i>Pulse Width Modulation</i>                                       |

| Q(z)                              | Função do ramo de realimentação do controlador repetitivo           |

| Q( $z^{-1}$ )                     | Representação no formato DSP de Q(z)                                |

| r(z)                              | Função discreta da tensão de referência                             |

| S(z)                              | Função discreta integrante de C(z)                                  |

| SPWM                              | <i>Sinusoidal pulse width modulation</i>                            |

| THD                               | <i>Distorção Harmônico Total</i>                                    |

| Ts                                | Período de amostragem                                               |

| UFU                               | Universidade Federal de Uberlândia                                  |

| UPS                               | <i>Uninterruptible Power Supplies</i>                               |

| USB                               | <i>Universal Serial bus</i>                                         |

| V <sub>o</sub>                    | Tensão de saída do filtro LC                                        |

| V <sub>ab</sub>                   | Tensão de entrada do filtro LC                                      |

| V <sub>cr</sub>                   | Tensão da portadora triangular para o PWM                           |

| V <sub>g1</sub> , V <sub>g3</sub> | Sinal para o gatilho das chaves IGBTs                               |

| VHDL                              | <i>Very Speed Integrated Circuit, Hardware Description Language</i> |

| VHDL                              | <i>VHSIC Hardware Description Language</i> )                        |

| VHSIC                             | <i>Very High Speed Integrated Circuit</i>                           |

| V <sub>m</sub>                    | Tensão moduladora para o PWM                                        |

| V <sub>ref</sub>                  | Tensão de referência                                                |

| Y(z)                              | Saída de planta                                                     |

| Z <sub>o</sub>                    | Impedância de carga do inversor                                     |

| Ω                                 | Ohm, unidade de resistência elétrica                                |

# SUMÁRIO

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>1 INTRODUÇÃO .....</b>                                                     | <b>14</b> |

| 1.1 Considerações iniciais .....                                              | 14        |

| 1.2 Justificativa .....                                                       | 15        |

| 1.3 Objetivo .....                                                            | 17        |

| <b>2 FPGA .....</b>                                                           | <b>18</b> |

| 2.1 Linguagem de Descrição de Hardware (HDL).....                             | 21        |

| 2.2 Fase de síntese para projeto utilizando FPGA.....                         | 22        |

| 2.3 Sobre a placa de desenvolvimento utilizada no projeto .....               | 23        |

| <b>3 PRINCÍPIOS DOS INVERSORES DE TENSÃO.....</b>                             | <b>26</b> |

| 3.1 Técnica de modulação .....                                                | 27        |

| 3.2 Técnicas de controle .....                                                | 29        |

| 3.2.1 Controle PID.....                                                       | 30        |

| 3.2.2 O controlador de Ação Repetitiva .....                                  | 31        |

| 3.2.3 Controle <i>Feedforward</i> .....                                       | 33        |

| 3.3 Técnicas de controle aplicadas ao Sistema Inversor de tensão .....        | 34        |

| 3.3.1 Controlador de Ação Instantânea.....                                    | 35        |

| 3.3.2 Controlador de Ação Repetitiva .....                                    | 39        |

| <b>4 METODOLOGIA .....</b>                                                    | <b>41</b> |

| 4.1 System Generator .....                                                    | 42        |

| 4.2 VHDL .....                                                                | 48        |

| 4.3 Construção dos controladores .....                                        | 48        |

| 4.4 Detalhes da metodologia .....                                             | 52        |

| 4.4.1 Funções de transferências .....                                         | 53        |

| 4.4.2 O circuito de ajuste do tempo de aquisição .....                        | 55        |

| <b>5 DESCRIÇÃO DA PLANTA .....</b>                                            | <b>57</b> |

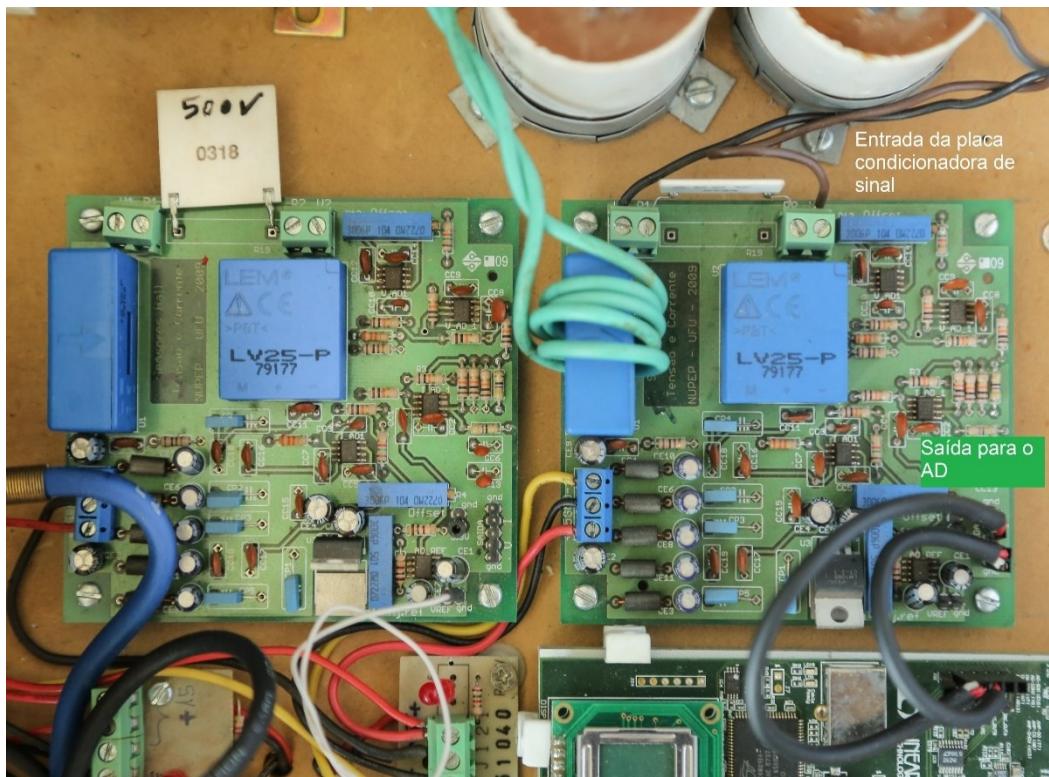

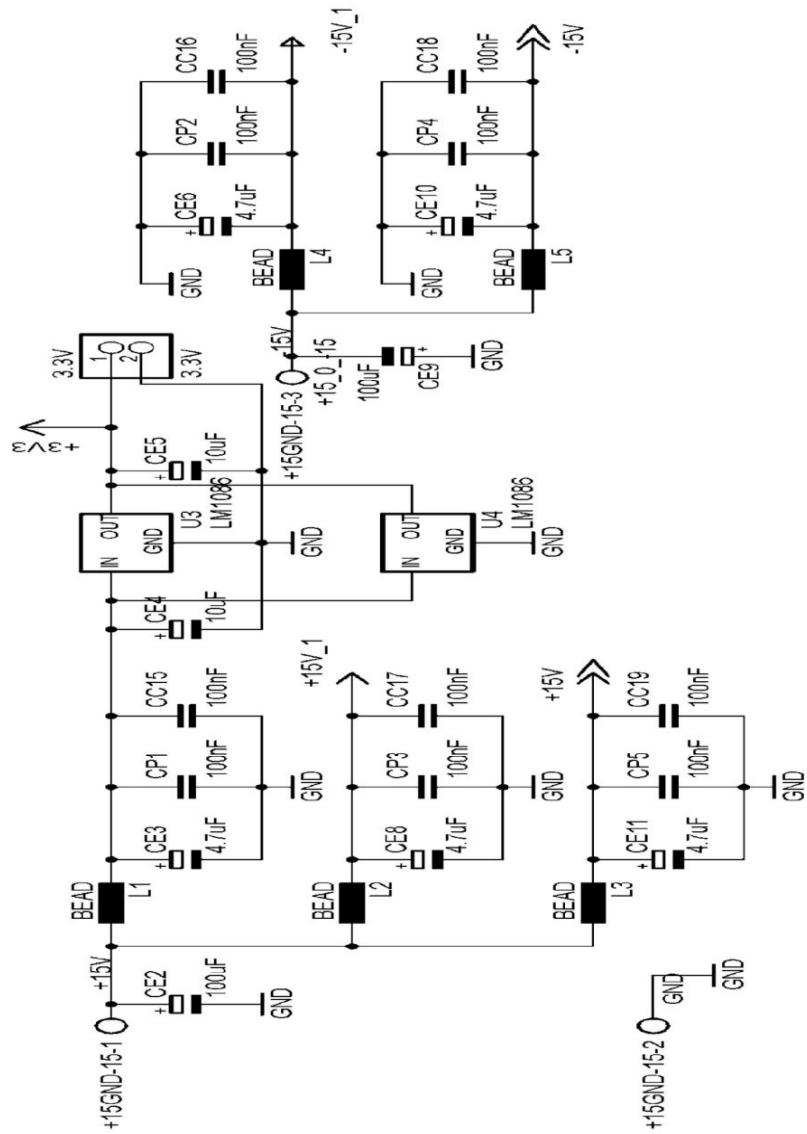

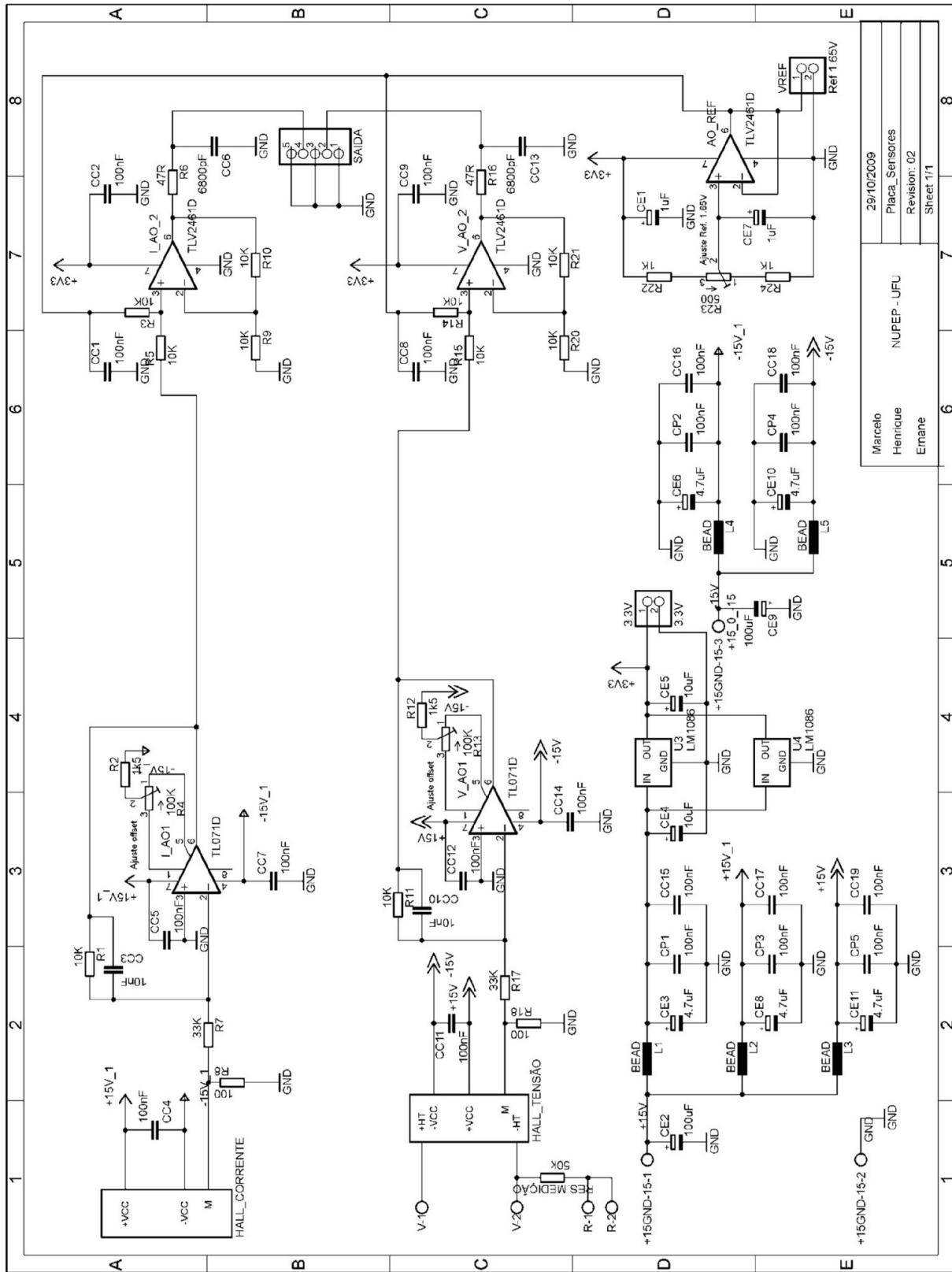

| 5.1 Placa de aquisição .....                                                  | 58        |

| 5.2 Placa de adequação dos sinais da FPGA para os Gate Drivers dos IGBTs .... | 61        |

| 5.3 A carga.....                                                              | 62        |

| 5.4 Filtro LC .....                                                           | 64        |

| 5.5 Módulo da Semikron .....                                                  | 65        |

| 5.6 FPGA .....                                                                | 66        |

|                                                                                        |           |

|----------------------------------------------------------------------------------------|-----------|

| <b>6 RESULTADOS.....</b>                                                               | <b>68</b> |

| 6.1 Resposta da Função de Transferência do Repetitivo e PD-feeforward no Sistema ..... | 68        |

| 6.2 Resposta ao Degrau da Função de Transferência do Repetitivo e PD-feeforward .....  | 69        |

| 6.3 Resultado da Simulação no PSIM.....                                                | 71        |

| 6.4 Resultado da Simulação no System Generator .....                                   | 74        |

| 6.5 Resultado da co-simulação no System Generator .....                                | 74        |

| 6.6 Resultados experimentais do controle Repetitivo implementado .....                 | 75        |

| <b>7 CONCLUSÃO E PROPOSTA PARA TRABALHOS FUTUROS .....</b>                             | <b>79</b> |

| <b>REFERÊNCIAS.....</b>                                                                | <b>81</b> |

| <b>APÊNDICE.....</b>                                                                   | <b>87</b> |

| APÊNDICE A - Exemplo de funções primitivas do System Generator .....                   | 87        |

| APÊNDICE B - Código implementado no bloco Black Box .....                              | 88        |

| <b>ANEXOS .....</b>                                                                    | <b>90</b> |

| ANEXO A - Circuito da placa de aquisição e condicionamento de sinais .....             | 90        |

| ANEXO B - Código implementado no bloco Mcode .....                                     | 91        |

## 1 INTRODUÇÃO

### 1.1 Considerações iniciais

O mundo passa atualmente por uma crise energética [1]. O consumo de energia elétrica é cada vez mais elevado, porque mais pessoas estão adquirindo bens que funcionam a partir da eletricidade. Com o aumento da demanda, as indústrias precisam produzir mais bens de consumo e, para isto, necessitam utilizar mais energia elétrica, que é um insumo básico para a indústria de transformação. O petróleo e o carvão mineral são utilizados como fontes de energia e são hoje os principais responsáveis pela maior parte da energia elétrica consumida no mundo. Porém, são recursos minerais e, como tal, não são renováveis [1-2]. Por isso, precisam ser poupadados.

Além da finitude desses recursos, há ainda o inconveniente grave da poluição originada pelo uso dessas fontes de energia e seus derivados. Felizmente, existem outras maneiras de se gerar energia elétrica, que são as fontes renováveis. As mais conhecidas destas fontes são a hidroeletricidade, a energia eólica e a solar. Todas estas formas de energia causam algum tipo de impacto ambiental, porém possuem a vantagem de serem renováveis, ou seja, seu aproveitamento é infinito.

A produção de energia elétrica utilizando a hidroeletricidade provoca alagamentos de grandes áreas pelos reservatórios necessários, comprometendo diversos ecossistemas. A utilização de energia eólica interfere nas rotas das aves migratórias, provoca o aquecimento do solo abaixo das pás e a ocupação de áreas muito extensas, além de possíveis modificações no regime dos ventos após a instalação do parque eólico [3]. A produção de energia solar, por sua vez, requer o uso de painéis fotovoltaicos e causa impacto ambiental com a mineração que é necessária para a obtenção dos metais insumos de sua confecção [4]. Porém, se utilizados nos lugares corretos, esses painéis podem ser uma alternativa muito interessante. A utilização mais racional dos painéis solares é sobre os telhados de residências, fábricas e edifícios. São áreas já impermeabilizadas e, portanto, com ecossistemas degradados, que podem ser aproveitadas sem necessidade de mais espaço alocado para isto.

Diante desse cenário de crise energética, brevemente descrito, é preciso buscar soluções para o problema que se apresenta como um desafio para o mundo

atual. As fontes de energias alternativas, como a eólica e a solar, são opções que podem diminuir o consumo das fontes não renováveis. Mais especificamente a fonte de energia solar, capaz de gerar energia elétrica a partir das irradiações solares, apresenta-se com uma excelente opção, principalmente para o Brasil, que tem grande incidência de raios solares durante quase o ano todo.

Os painéis solares são fontes não despacháveis. Assim, em grande parte das aplicações, os sistemas PV (Painel Voltaico) operam conectados à rede e são chamados sistemas *grid following*. Tais sistemas operam como uma fonte de corrente conectada à rede, sendo que a tensão no ponto de conexão é imposta pela rede. No caso de falta da rede, um algoritmo anti-ilhamento deve desligar o sistema, pois, além de não haver uma malha para regular a tensão, não há como garantir o fornecimento de energia à carga com uma fonte não despachável. Além disso, existem aspectos de segurança para os operadores do sistema que devem ser observados.

Em casos específicos, como nos sistemas distribuídos, ou micro-redes, há necessidade da operação ilhada para permitir o fornecimento ininterrupto de energia. Isto implica a necessidade de um nó formador de rede (*grid forming*) para a regulação da tensão na ausência da rede da concessionária. Este nó deve contemplar uma fonte primária despachável e um inversor com malha reguladora de tensão. Este pode ser, então, um inversor de tensão com controlador de ação *repetitiva* e *PD-feedforward* embarcado em FPGA (*Field Programmable Gate Array*), que é objeto da presente pesquisa.

## 1.2 Justificativa

O presente trabalho justifica se, de maneira geral, pelo fato de envolver um conversor CC-CA (Corrente Contínua-Corrente Alternada), que está presente em várias aplicações da área de Eletrônica de Potência. E especificamente pela necessidade de iniciar uma cultura para o uso da FPGA em Eletrônica de Potência no Núcleo de Eletrônica de Potência da Faculdade de Engenharia Elétrica da Universidade Federal de Uberlândia (FEELT-UFU), onde a maioria das implementações são realizadas com a utilização dos DSP (Digital Signal Processor). E quando ocorreu o uso de FPGA, sempre limitou-se a substituir circuitos digitais. Ademais, não há trabalhos realizados com a utilização de circuitos complexos

implementados em FPGA, como por exemplo o filtro digital. Neste sentido, este trabalho dá início à formação da cultura de utilizar a FPGA para a implementação de controle na área de Eletrônica de Potência da FEELT-UFU, e se beneficiar dessa tecnologia. Portanto, no presente trabalho são utilizadas as técnicas de controle digital para implementar um controle CC-CA todo embarcado em FPGA.

O controle digital apresenta diversas vantagens em comparação aos controles analógicos, dentre as quais destaca-se algumas:

- Solução programável: modificações, atualizações ou adaptações são realizadas via software;

- Menos sensível ao ruído ambiente;

- Suporta algoritmos avançados de controle;

- Permite as funções de controle adaptativo, não linear e *self-tuning*;

- Admite operação *sensorless*;

- Admite funções especiais: monitoramento, diagnóstico, proteção, etc;

- Capacidade de comunicação: permite a incorporação a um sistema integrado de controle;

- Capacidade de armazenamento de dados flexível [5].

Os sistemas digitais apresentam como desvantagens:

- Requer a conversão de dados (A/D – D/A);

- Métodos de análise e projeto são mais complexos;

- Taxa de amostragem e resolução podem afetar os níveis de rejeição aos distúrbios vinculados à carga;

- Os atrasos computacionais limitam a banda passante do sistema e podem afetar a estabilidade;

- Erros de quantização e truncamento podem afetar a precisão do controle;

- Durante a fase de ajuste, é difícil o acesso à variáveis intermediárias [5];

Na área de Eletrônica de Potência, o processador digital de sinais (DSP – *Digital Signal Processor*) é largamente utilizado para soluções de controle dos

sistemas digitais implementados. Esta opção está relacionada com suas características digitais, alta velocidade de processamento, versatilidade da linguagem de programação (C ou *Assembly*) e com sua característica de trabalhar com ponto flutuante, realizando operações complexas. Entretanto, mesmo com o elevado desempenho dos processadores (inclui os DSP) atuais, capazes de realizar instruções de MAC (*Multiply and accumulate*), as quais aceleram o cálculo de funções digitais, estes possuem apenas uma unidade aritmética e todos os cálculos dos controladores são realizados de forma sequencial.

Uma forma de acelerar o desempenho de um controlador é criar condições para a realização de cálculos em paralelo (simultaneamente) onde os mesmos são possíveis, ou seja, em partes do algoritmo de controle onde não há dependência sequencial de dados. Esta é justamente a vantagem das FPGAs: o processamento paralelo [6-7].

Devido à importância das FPGAs como solução para a implementação de controladores digitais em Eletrônica de Potência, enfatiza-se que este trabalho visa contribuir para a inserção da cultura de utilização das FPGAs no Laboratório de Eletrônica de Potência da FEELT-UFG, como um estudo de caso, em que todas as particularidades das etapas de implementação e seus respectivos desafios são apresentados. Foi adotado um exemplo de aplicação pesquisado na literatura, com a preocupação de focar o uso da FPGA na realização de cálculos, e não somente na implementação de circuitos lógicos.

### 1.3 Objetivo

A pesquisa foi realizada com o objetivo de usar o controle digital em FPGA na área de Eletrônica de Potência. Para isso, usou-se como base principal a reprodução dos resultados do controle repetitivo da tese de Leandro Michells [8]. Desta forma, via mera comparação de resultados, foi possível a validação da implementação do controlador em FPGA.

Vale a pena ressaltar que, além das funções de controle em si, outros elementos do sistema são também embarcados em FPGA, como a geração de sinais de referência, o bloco PWM (*Pulse Width Modulation*), a comunicação serial com o conversor A/D (Analógico / Digital) e elementos de proteção (desligamento de chaves no caso de sobrecorrente ou sobretensão na tensão de saída). Ressalte-se

ainda que este será o primeiro projeto completamente embarcado em FPGA desenvolvido no Núcleo de Pesquisa em Eletrônica de Potência (NUPEP) da FEELT-UFU.

## 2 FPGA

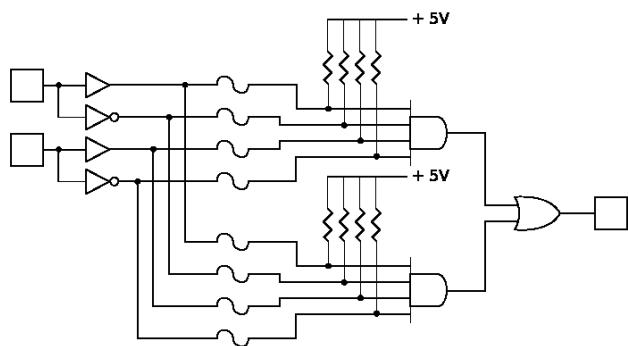

A origem das FPGAs (*Field Programmable Gate Array*) está diretamente associada à evolução da eletrônica em geral, que teve seu início na válvula, depois no transistor, circuitos integrados, processadores e, finalmente, o mais próximo das FPGAs, a PAL (*Programmable Logic Device*). Mas este era um dispositivo que permitia a programação somente uma vez, como se fosse um “fusível”. A Figura 1 [9], abaixo, mostra um exemplo.

Simplified programmable logic device

Figura 1 - Exemplo dos primeiros circuitos programáveis

Fonte: Referência [9]

As PALs disponibilizam somente um conjunto de funções lógicas como portas *AND* e *OR* associadas a um conjunto de “chaves” que permitem configurar apenas funções combinacionais. Esta é uma das diferenças fundamentais em relação às FPGAs, que, além das funções combinacionais, realizam as funções sequenciais, que constituem uma das bases para a realização de qualquer circuito digital.

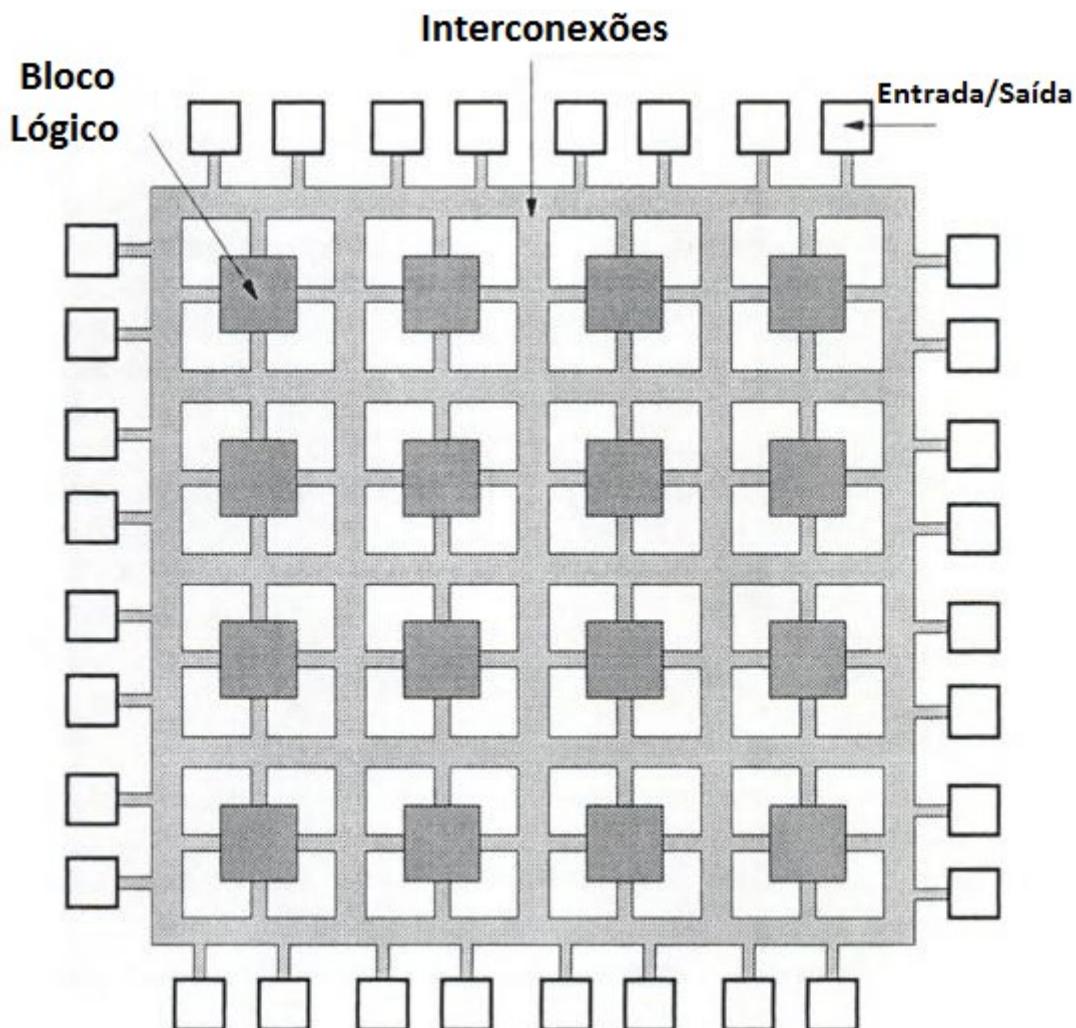

As FPGAs são conjuntos de circuitos digitais, organizados de uma maneira específica, distribuídos dentro de um mesmo encapsulamento, com diversas possibilidades de ligações entre todos os elementos; são formadas por circuitos com maior complexidade como LUTS (*Look-Up Tables*) e Flip Flop, multiplicadores, entre outros. Na Figura 2, a seguir, temos o conceito de FPGA.

Figura 2 - Conceito de FPGA [10]

Fonte: [[https://www.researchgate.net/figure/303773247\\_fig1\\_Figura-1-Arquitetura-basica-de-um-FPGA-FPGAs-utilizam-o-conceito-de-Bloco-Logico](https://www.researchgate.net/figure/303773247_fig1_Figura-1-Arquitetura-basica-de-um-FPGA-FPGAs-utilizam-o-conceito-de-Bloco-Logico)] Acesso em: 15 dez. 2017

Os conjuntos de circuitos que formam as FPGAs são organizados em blocos. As formas de organização destes blocos são determinadas pelos fabricantes. No caso da Xilinx, o bloco mais elementar é constituído por células lógicas (*Logic Cell* ou LC) formadas por: uma *LUT* de quatro entradas e um *Flip Flop* tipo D; além disso, a LC contém um circuito de transporte (*carry*) para ser utilizado em operações aritméticas; funções lógicas; circuitos de multiplexação para gerenciar o acesso e troca de informações entre as células lógicas [10].

Para aumentar a flexibilidade e melhorar o desempenho, estas células lógicas são combinadas, no caso da Xilinx, em duas e recebem o nome de *slice* (fatia em português), e quatro fatias são agrupadas para formar um Bloco Lógico

Programável (CLB – *Configurable Logic Block*). Junta-se neste processo as estruturas de multiplexação [10].

As FPGAs são formadas também por macro células (*Macro Cell*), além dos elementos citados acima. As macro células são circuitos com funções específicas, colocados junto com os elementos básicos da FPGA para completar, aumentar o desempenho e facilitar a formação dos mais diversos circuitos como: blocos de memórias; gerenciador de clock (DCM); blocos de multiplicadores; blocos de multiplexação da FPGA para entradas e saídas e, por fim, blocos de núcleos de processadores [10].

A primeira FPGA foi a XC2064, construída pela Xilinx em 1985. Era formada por apenas 64 blocos lógicos e cada bloco com duas LUTs e um registrador e um total de 800 portas. Foi produzida com um custo de 55 dólares e com tecnologia  $2.0\mu$ . Atualmente, as FPGAs da Xilinx estão sendo feitas com tecnologia de 16nm e 862K de células lógicas [11].

A grande vantagem da FPGA advém da possibilidade de implementar a maioria dos projetos digitais juntando tanto a lógica combinacional quanto a sequencial, combinando os diversos circuitos que fazem parte do conjunto da sua formação. Este fato traz grande liberdade para a implementação de projetos. Por exemplo, se um projeto precisar de somador de 32 bits e a FPGA for formada com blocos somadores de 16 bits, o software responsável pela alocação dos circuitos vai selecionar dois blocos somadores de 16 bits para obter um somador de 32bits. E se precisar de somador de 48 bits, então serão ligados três blocos de somadores de 16 bits para resultar no somador de 48 bits. O importante é que este processo pode ser repetido para todos os componentes da FPGA, registradores, memórias, LUTs, multiplicadores, etc. Vale lembrar que nos processadores atuais, não é possível alterar nenhuma característica de hardware. Isso é uma vantagem das FPGAs [10].

A capacidade de processamento paralelo das FPGAs é outra especificação que faz delas uma referência em processamento. As FPGAs são capazes de realizar o processamento em paralelo de grandes quantidades de multiplicações, somas, deslocamentos de bits, inversão de bits, etc. Essa característica faz das FPGAs um elemento fundamental para aplicações de elevado nível de processamento paralelo e alto grau de confiabilidade [10], já que tudo é realizado em hardware, sem a gerência de nenhum sistema operacional. Neste caso não há ciclo de busca de instrução, nem *Pipeline*, ou *threads*.

Outra vantagem é a facilidade de protipagem de projetos. Fazer um projeto e testar leva muito pouco tempo, se comparado ao desenvolvimento de um chip específico com técnica ASIC (*Application Specific Integrated Circuit*). Os custos dos projetos diminuem muito, tem-se uma redução da duração do ciclo de projeto, ou seja, a reconfiguração. Além do custo em constante queda, há o aumento da velocidade de processamento e da quantidade de componentes [12].

## 2.1 Linguagem de Descrição de Hardware (HDL)

A implementação de circuitos digitais em FPGA possui, por base, uma linguagem que descreve os componentes que serão implementados. A partir dessa linguagem é possível modelar os circuitos de implementação para uma determinada FPGA (*chip*). Existem várias linguagens para descrição de hardware: VHDL, VERILOG, AHDL (Linguagem desenvolvida pela Altera), Handel-C, SDL, ISP e ABEL [10].

As linguagens para descrição de hardware que mais se destacaram ao longo da história foram VHDL e VERILOG. Para o projeto desenvolvido, utilizou-se o VHDL (*Very Speed Integrated Circuit, Hardware Description Language*). Esta escolha tem por base o fabricante do Kit Spartan3an Xilinx, que usa esta linguagem para a síntese de projeto, e também pela padronização realizada pelo IEEE (Instituto de Engenheiros Eletricistas e Eletrônicos) em 1987 criando o padrão 1076, que se tornou um padrão internacional. Atualmente, a maioria dos ambientes de programação para HDL tem a opção de síntese utilizando o VHDL.

A VHDL possui uma grande quantidade de elementos que permitem modelar circuitos com alto nível de abstração. Abaixo são apresentadas algumas propriedades que justifica sua importância:

- Documentação: a descrição dos componentes por si já constitui uma forma de documentação para o projetista;

- Simulação: permite realizar a simulação funcional e temporal do projeto para verificar o seu correto funcionamento. Simulações que podem ser realizadas por blocos estruturais e comportamentais;

- Simplifica a migração tecnológica: o sistema pode ser facilmente sintetizado em outras tecnologias;

- Reutilização de recursos: permite a construção de bibliotecas (componentes) e módulos (circuitos) para serem reutilizados, o que permite reduzir o tempo de projeto. [10]

A linguagem VHDL possui uma estrutura básica e fundamental para o seu entendimento e utilização. A primeira é a entidade (*entity*), parte do código em que são definidas as conexões do componente com o mundo externo, as portas e os seus tipos de dados. A segunda é arquitetura (*architecture*), onde os dados que chegaram da entidade serão alterados conforme o código existente. A seguir tem-se um exemplo de código na linguagem VHDL com os dois elementos básicos e fundamentais:

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity AOI is

port (

A, B, C, D: in STD_LOGIC;

F : out STD_LOGIC

);

end AOI;

architecture V1 of AOI is

begin

F <= not ((A and B) or (C and D));

end V1;

```

## 2.2 Fase de síntese para projeto utilizando FPGA

A geração de código para ser executado em FPGA possui várias fases, que serão apresentadas de forma resumida. Essas fases são códigos que definirão o comportamento da FPGA, a geração do *Netlist*, o processo de roteamento, a validação do mapeamento, geração do arquivo binário e configuração da FPGA.

O comportamento da FPGA é definido através da criação de um projeto, que pode ser gráfico (esquemático) ou código em HDL.

Para se conseguir o *Netlist* a partir do projeto em HDL, normalmente, usa-se uma ferramenta EDA (*Electronic Design Automation*). Esta fase descreve a conectividade entre os circuitos, pinos, portas e componentes.

O processo de roteamento é o ajuste do *Netlist* para uma determinada arquitetura FPGA.

O mapeamento é a validação do *Netlist* roteado, através de uma análise temporal e simulação.

A partir do mapeamento é gerado o arquivo de *bitstream* e, finalmente, será transferido para a FPGA para sua configuração. Normalmente, esta transferência é realizada através do protocolo JTAG [13].

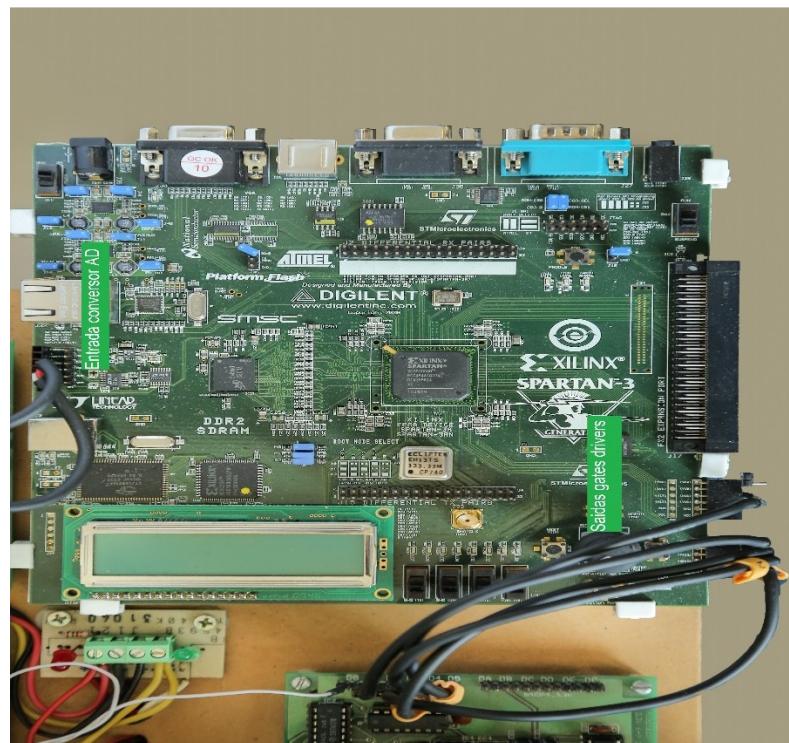

### 2.3 Sobre a placa de desenvolvimento utilizada no projeto

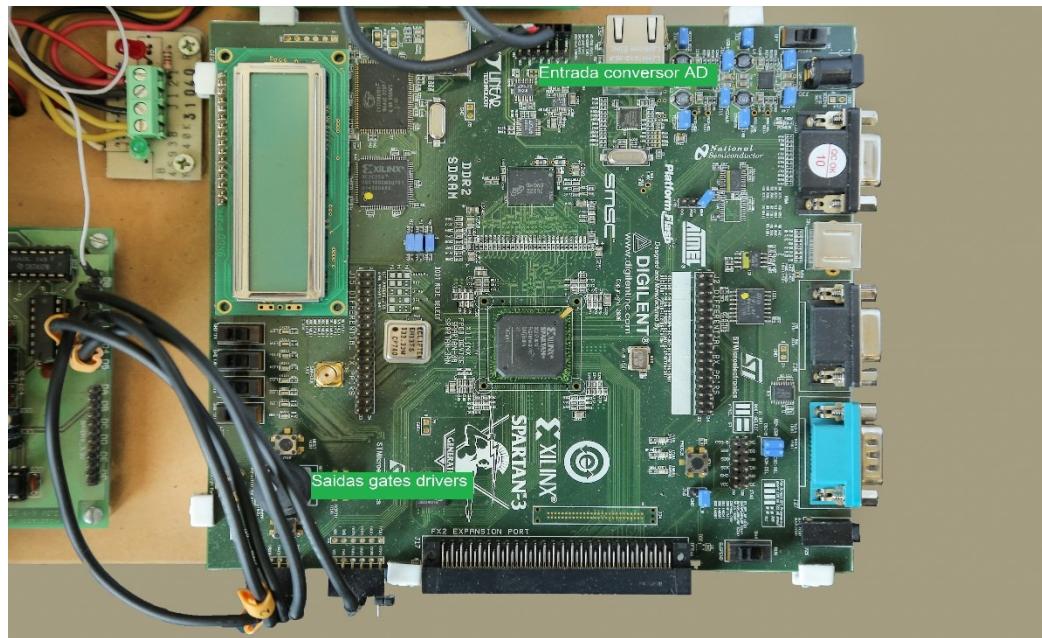

A placa utilizada para o desenvolvimento deste projeto foi a Spartan3an da Xilinx. Este kit contém várias interfaces de comunicação – chaves, botões, várias opções de boot e display [14].

Figura 3 – Placa FPGA utilizada

Algumas características deste kit são mostradas abaixo:

## FPGA

- \* Spartan-3AN (XC3S700AN-FG484)

## Clocks

- \* Cristal oscilador de 50 MHz na placa;

- \* Slot para inserção de cristal de clock opcional.

## Memórias

- \* 4 Mbit *Platform Flash PROM*;

- \* 32M x 16bit DDR2 SDRAM;

- \* 32 Mbit Flash paralela;

- \* 2 dispositivos Flash SPI de 16 Mbit.

## Dispositivos de interface analógica

- \* Conversor D/A de quatro canais;

- \* Conversor A/D de dois canais;

- \* Amplificador de sinal.

## Conectores e Interfaces

- \* *Ethernet 10/100 PHY*;

- \* Porta *JTAG USB download*;

- \* Duas portas seriais RS-232 de 9 pinos;

- \* Porta OS/2-style para mouse e teclado;

- \* Conector VGA de 15 pinos, capaz de produzir 4096 cores;

- \* Um conector de expansão FX2 de 100 pinos e dois conectores de 6 pinos;

- \* 20 Entradas/saídas disponíveis em conectores padrão;

- \* Stereo mini-jack para PWM áudio;

- \* Chave com função rotativa e *push-button*;

- \* Oito saídas LED individuais;

- \* Quatro chaves *slider*, quatro chaves *push-button*.

## Display

- \* LCD de 16 caracteres, 2 linhas.

Para a realização do projeto foi importante o conversor AD que faz parte do kit. O conversor AD é o circuito LTC1407A-1. Este conversor possui dois canais de 14bits com saída em complemento de 2, o que proporciona uma faixa de representação que vai de -8192 a +8191, condicionado por uma faixa de tensão de entrada que abrange de 0.4V até 2.9V com o zero igual 1.65V (tensão de *offset*). A resolução para esta faixa de tensão é de aproximadamente  $152 \times 10^{-6}$  V. Para o projeto, um dos canais foi usado para realizar a conversão da tensão de saída analógica da planta para digital.

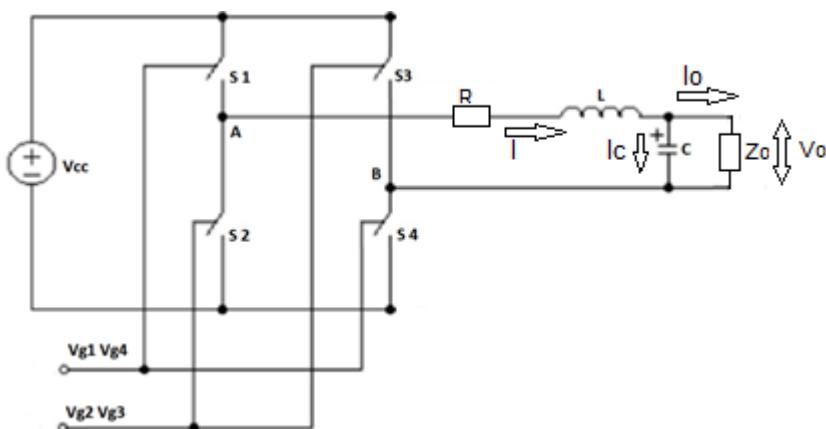

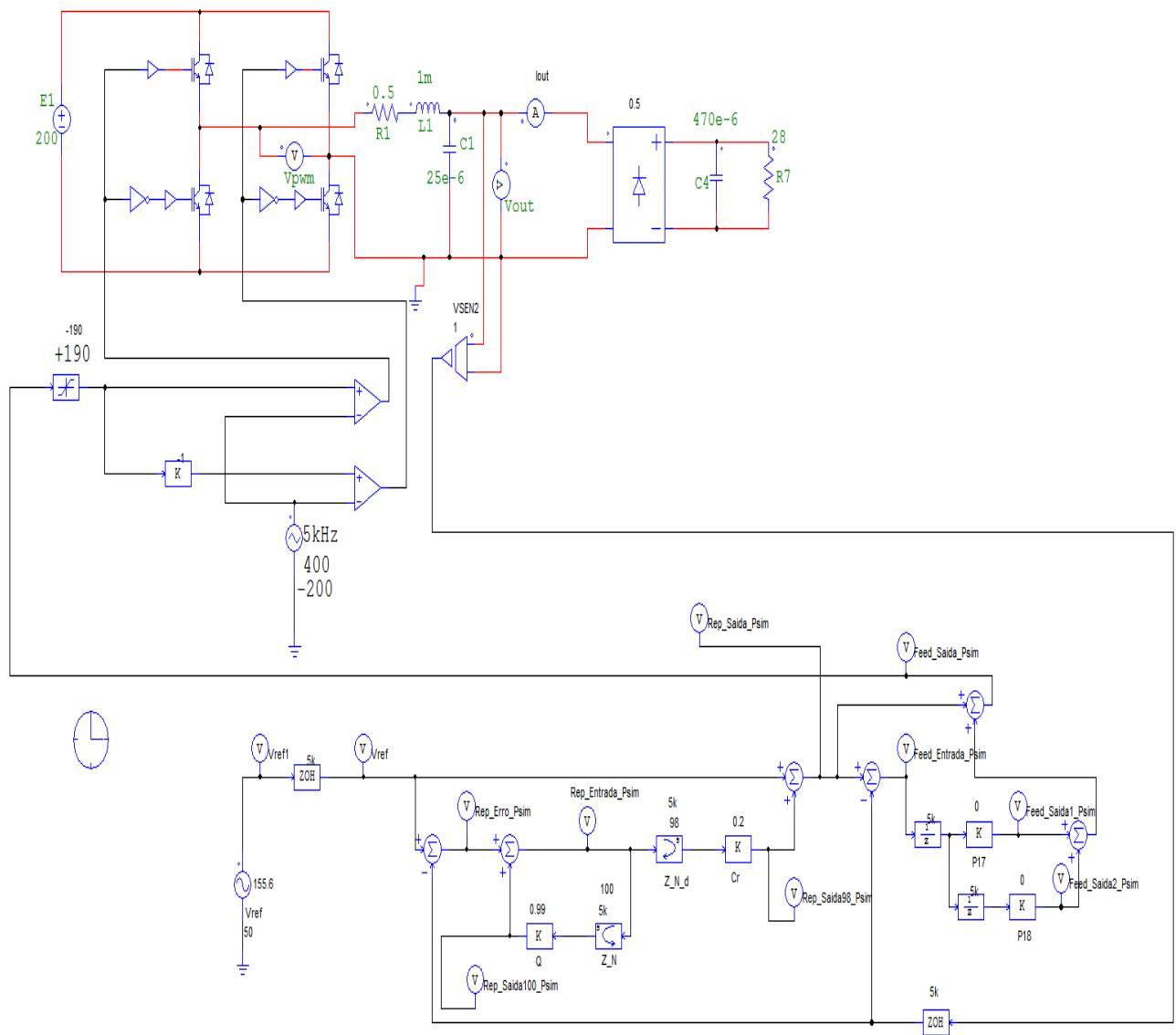

### 3 PRINCÍPIOS DOS INVERSORES DE TENSÃO

Os dispositivos que realizam a conversão de tensão contínua para tensão alternada são conhecidos como inversores de tensão. Possuem a capacidade de converter a tensão contínua para alternada, podendo gerar uma tensão de saída alternada com frequência e amplitude variáveis para diversas aplicações industriais [15] como: acionamento de máquinas elétricas de corrente alternada em velocidade variável; sistema de alimentação ininterrupta, em tensão alternada, a partir de bateria; aquecimento indutivo; UPS (*Uninterruptible Power Supplies*). Tendo como tensão de entrada fontes CC que podem ser: célula combustível; bateria; células fotovoltaicas; ou outra fonte CC.

O inversor de tensão utilizado na pesquisa é um conversor monofásico em ponte completa. O princípio de funcionamento é baseado no comando de quatro chaves (S1, S2, S3, S4), que são transistores bipolares com porta de entrada isolada (IGBT) acionadas, normalmente, por uma estratégia de controle PWM (Figura 4). A modulação utilizada será apresentada na seção 3.1 Técnica de modulação.

Figura 4 – Topologia ponte completa

As equações 1, 2 e 3 descrevem o comportamento do sistema do inversor, sendo que neste trabalho será considerado que a estratégia PWM apresenta um ganho unitário puro.

$$V_{ab} = RI(s) + LsI(s) + Vo(s) \quad (1)$$

$$I(s) - Io(s) = Cs \cdot V_0(s) \quad (2)$$

$$Vo(s) = Z_o(s) \cdot Io(s) \quad (3)$$

### 3.1 Técnica de modulação

A modulação dos sinais que controlam os IGBT (Insulated Gate Bipolar Transistor) tem como objetivo controlar a tensão de saída dos inversores para alguma aplicação. A técnica de modulação mais aplicada e eficiente é o PWM [16]. A técnica de PWM possui vários modos: modulação por largura de pulso único; modulação por largura de pulsos múltiplos; modulação por largura de pulso senoidal e modulação por largura de pulso senoidal modificada. Na pesquisa em questão foi realizada a técnica de modulação SPWM (Sinusoidal Pulse Width Modulation).

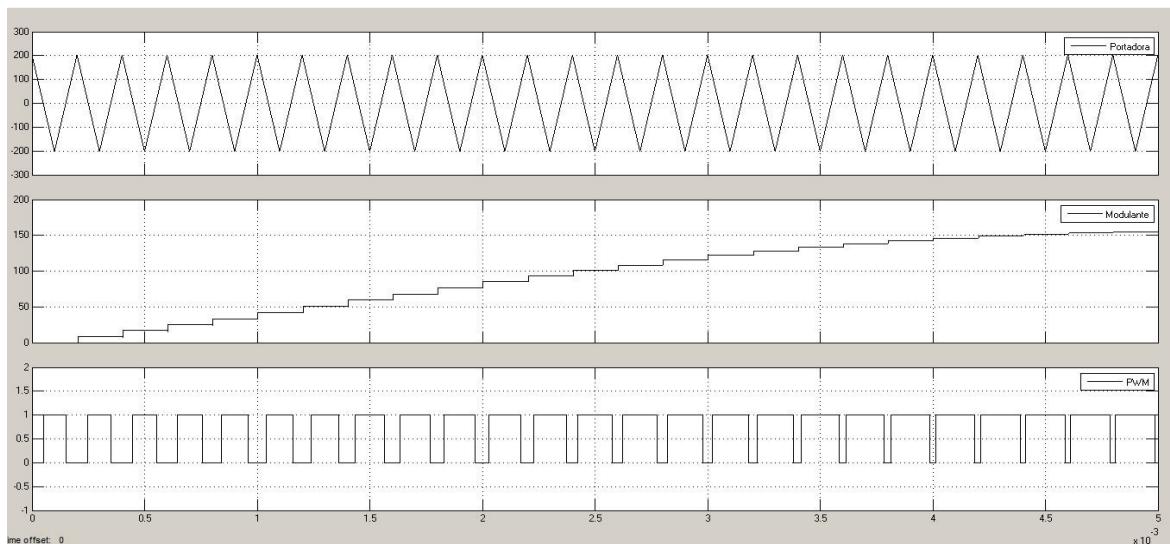

A modulação SPWM é sintetizada a partir de duas ondas, sendo uma senoidal e uma triangular. A onda triangular, a qual recebe o nome de portadora, determina a frequência de chaveamento dos IGBTs. A onda senoidal, que recebe o nome de moduladora, determina a frequência de saída e, através do índice de modulação, determina a amplitude da tensão de saída. O SPWM funciona comparando a forma de onda senoidal moduladora com a forma de onda triangular, gerando as larguras de pulsos que serão aplicados nas chaves IGBTs. As três formas de ondas necessárias ao controle dos IGBTs podem ser vistas na Figura 5.

Figura 5 – Formas de ondas da modulação senoidal PWM

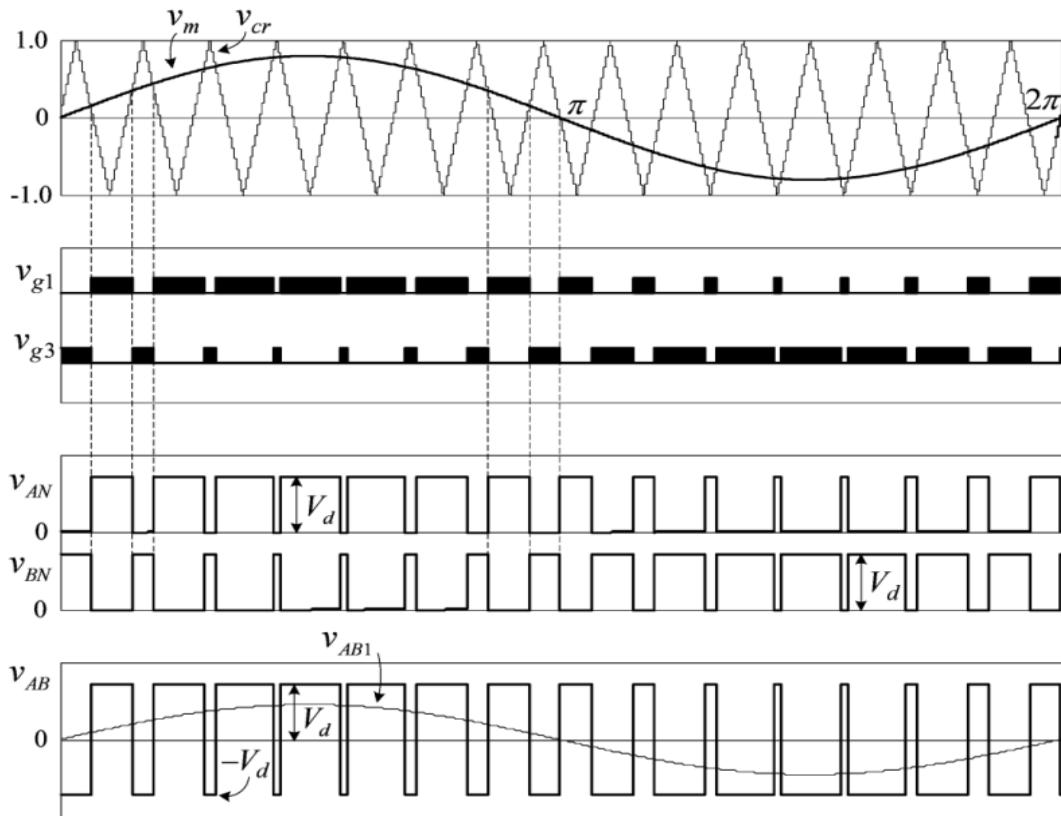

A estratégia de modulação PWM para inversores monofásicos pode ser Bipolar e Unipolar. Na Bipolar as chaves S1 e S3, operam de forma complementar às chaves S2 e S4. Assim, para o seu funcionamento são necessários apenas dois sinais complementares que acionam ora a chave S1, ora a chave S3. Estes sinais vêm da comparação de uma onda moduladora senoidal com uma onda triangular portadora. A tensão que será submetida ao filtro de saída será  $+V_{CC}$  quando S1 estiver fechada e  $-V_{CC}$  quando S3 estiver fechada. Portanto, este esquema de ligação é bipolar e caracteriza-se como estratégia Bipolar, cujos sinais são apresentados na Figura 6.

Figura 6 – Formas de ondas de um SPWM Bipolar

Fonte: Referência [17]

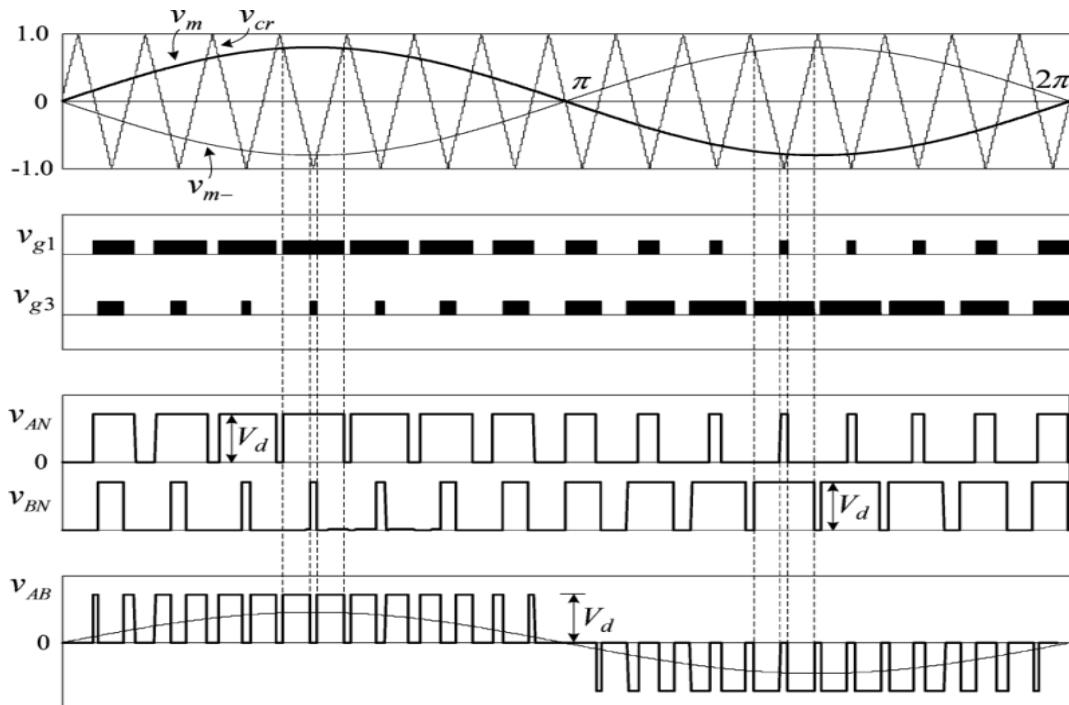

A estratégia Unipolar diferencia-se da Bipolar pelo fato de necessitar de duas ondas moduladoras senoidais  $V_m$  e  $-V_m$  com defasagem de 180 graus para realizar o acionamento das chaves, de mesma frequência e amplitude. As duas formas de ondas são comparadas com a portadora triangular  $V_{cr}$ , gerando os sinais de controle das chaves S1 e S3 da Figura 4. Pode-se observar pela Figura 7, que

os sinais  $V_{g1}$  e  $V_{g3}$  que controlam as chaves não se alternam simultaneamente. Esta é a diferença entre o PWM Unipolar e o Bipolar, onde todas as chaves são acionadas no mesmo instante. Neste caso, a tensão de saída  $V_{ab}$  (Figura 7) alterna entre zero e  $+V_{cc}$  para o semiciclo positivo e de zero e  $-V_{cc}$  para o semiciclo negativo da frequência fundamental ou moduladora. Por isso, esta topologia recebe o nome de Unipolar.

Figura 7 - Formas de ondas de um SPWM Unipolar

Fonte: Referência [17]

O SPWM Unipolar oferece vantagens como perdas de comutação reduzidas, gera menos Interferências Eletromagnéticas (EMI), redução no número de acionamento, o que diminui a geração de harmônicos maiores [17; 18]. Devido às vantagens da modulação unipolar, este tipo foi adotado no desenvolvimento da pesquisa.

### 3.2 Técnicas de controle

As técnicas de controle são as leis que determinam como e quando as chaves conectadas ao barramento CC irão abrir ou fechar para determinar a tensão de saída do filtro LC, especificamente a tensão no capacitor, em malha fechada.

Existem diversas técnicas para controlar as chaves, e aqui serão apresentadas algumas delas: PID, Repetitivo e Feedforward.

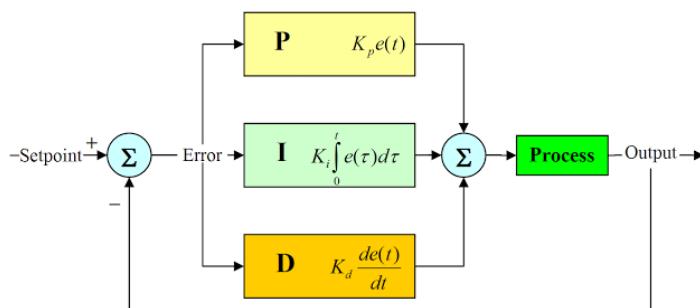

### 3.2.1 Controle PID

O controlador de ação PID é composto por três ações de controle, sendo uma proporcional, outra integral e uma última derivativa (Figura 8). A função de transferência de um controlador PID é representada pela seguinte equação:

$$H(s) = kp + \frac{Ki}{s} + kds \quad (4)$$

Onde os ganhos proporcional, integral e derivativo são representados por  $K_p$ ,  $K_i$  e  $K_d$ , respectivamente. Na prática, a ação derivativa é pouco utilizada, visto que os ruídos presentes na tensão de realimentação são amplificados, dificultando a operação em regime permanente [19, p. 22].

Figura 8 - Topologia do controle PID

Fonte: <https://stm32f4-discovery.net/2014/11/project-03-stm32f4xx-pid-controller/pid-controller-diagram/> em 26/01/2018

O controlador PID funciona bem para sistema com referência constante, no entanto não é capaz de produzir erro de regime nulo para referência senoidal. Mas existem autores que propõem modificações para melhorar o seu desempenho para regimes de referências periódicos, com erro nulo em regime permanente, características transitórias satisfatórias e rapidez de resposta [20; 21; 22; 23] de motores CC [24]. Contudo, para sistema de UPS, referências periódicas, controle CA, o controlador PID apresenta resultados insuficientes.

### 3.2.2 O controlador de Ação Repetitiva

Em razão da necessidade de gerar energia com qualidade para equipamentos que trabalham com cargas críticas (não linear), várias técnicas de controle foram propostas para atender às normas de qualidade de energia e, principalmente, para diminuir a THD (Total Harmônica de Distorção) na tensão de saída em regime permanente. Uma aplicação comum para os inversores de tensão com malha de realimentação da tensão de saída encontra-se nos sistemas UPS (*Uninterruptible Power Supply*). Estes sistemas sofrem influência da qualidade da energia fornecida pela concessionária, ficando sujeitos a todo tipo de distúrbios (variações de tipos de cargas, variações de tensão, sub-tensão e sobre-tensão, falta de rede, variação de frequência, surto de tensão ruídos, distorção harmônica). Em 1988, uma proposta para melhorar a qualidade da energia gerada pelas UPS foi apresentada pelos autores Haneyoshi, Kawamura e Hoft: O controle de Ação Repetitiva [8, p. 53].

O fundamento básico do funcionamento do controle de Ação Repetitiva é a utilização de informações dos ciclos passados para conseguir melhorar a saída atual. Este controle foi concebido a partir da necessidade de eliminação de distúrbio de carga e do rastreamento de referências periódicas. Assim, qualquer sistema que apresente distúrbios periódicos pode se beneficiar deste controle.

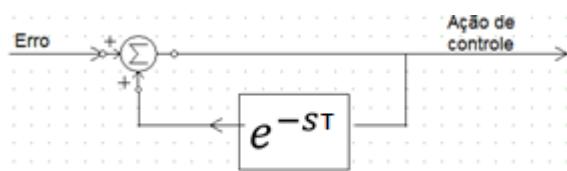

O controle de Ação Repetitiva tem como base o princípio do Modelo Interno [25], ou seja, “para que um sistema possua erro nulo em regime permanente na presença de qualquer referência ou distúrbio de carga, os modelos desses sinais devem estar presentes na malha fechada estável do sistema de controle” [26, p. 33]. No controle de ação repetitiva, o princípio do Modelo Interno é realizado através da realimentação positiva de um período com um atraso referente a um período  $T$ , como se vê na Figura 9.

Figura 9 - Princípio do controle Repetitivo

Existe a versão do modelo externo de controle com a ação repetitiva. Para esta situação, a ação do controle Repetitivo é posicionada fora da malha de controle. Entretanto, nesta pesquisa foi realizada a implementação do modelo interno.

A versão do controle de Ação Repetitiva com o princípio do modelo interno apresenta algumas vantagens: o comportamento do algoritmo é linear e a sua taxa de convergência é mais rápida que a dos demais. Já o controle de Ação Repetitiva externo possui como vantagem o fato de que o ganho em malha fechada da planta não é significativamente modificado [8].

Ambos os modelos apresentam também algumas desvantagens. No caso do modelo externo de Ação de controle Repetitiva, sua aplicação requer um modelo paramétrico (ou matemático) da planta e possui algoritmos mais complexos que os outros controladores. No modelo da Ação de controle Repetitiva, a resposta em frequência do sistema é modificada e “a robustez ao ruído e dinâmica não modelada é normalmente reduzida” [8].

O controle Repetitivo discreto foi proposto por Tomizuka [27] e motivou o interesse de diversos pesquisadores, o que resultou em uma grande quantidade de publicações [27; 28; 29; 30; 31; 32; 33; 34; 35]. A partir de diversas publicações, este controle também ganhou espaço na área de eletrônica, passando a ser aplicado nos controles de inversores PWM.

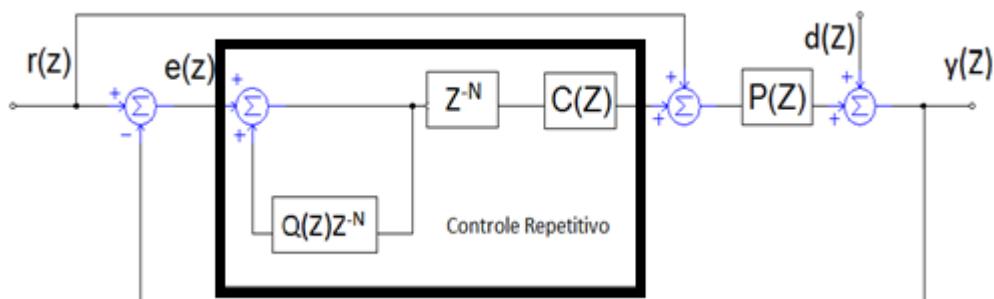

A partir da evolução histórica do controle Repetitivo, surgiram várias versões tendo como base o controle Repetitivo que ficou conhecido como tradicional. Apresenta-se, a seguir, a descrição do controle Repetitivo tradicional [36], mostrado na Figura 10.

Figura 10 - Controle Repetitivo Tradicional

A saída da planta  $y(z)$ , sob influência do distúrbio  $d(z)$ , é realimentada e comparada com a referência  $r(z)$ , gerando o erro  $e(z)$ ; o erro vai ser somado ao integrador  $Q(z)z^{-N}$  com um ciclo de atraso, multiplicado pelo  $Z^{-N}$  com um ciclo de atraso. Para  $Z^{-N}$  o valor de  $-N$  leva em conta o atraso da planta. Chegando no compensador  $C(z)$  que, somado com  $r(z)$ , atua na planta  $P(z)$ .

O compensador  $C(z)$  depende da planta  $P(z)$  e a sua equação fica definida completamente da seguinte forma:

$$C(z) = C_r Z^{-k} S(z) \quad (5)$$

Os termos empregados na equação de  $C(z)$  representam os atrasos da planta e do filtro LC e o ganho. O ganho é definido pelo  $C_r$ ;  $Z^k$  é o compensador total de fase do atraso resultante da planta  $P(z)$  e de  $S(z)$ . E por último  $S(z)$ , que corresponde ao filtro de segunda ordem passa baixo, utilizado nos inversores PWM, que modifica a resposta de frequência do sistema.

### 3.2.3 Controle *Feedforward*

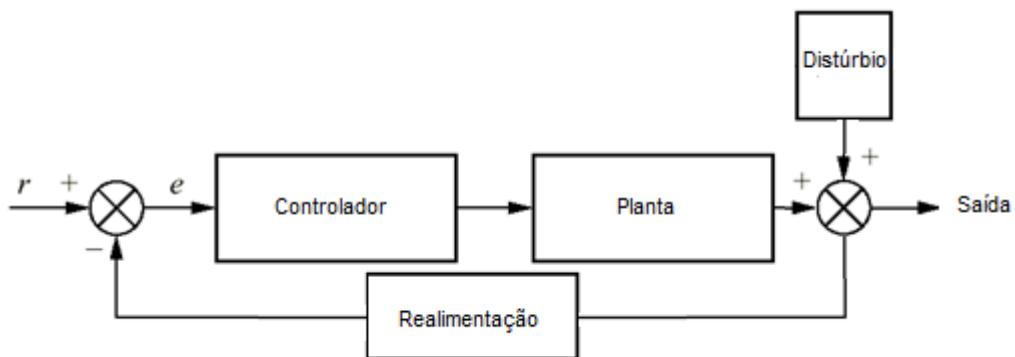

O controle *Feedforward* tem como característica principal a sua capacidade de antecipar a ação de resposta a algum distúrbio. Por isto o seu nome de *Feedforward*, alimentação adiantada, antecipatório ou método de alimentação direta. O controle *Feedforward* realiza esta antecipação de atuação na planta como apenas o sinal de referência e conhecendo o distúrbio. Para outras formas de controle ação de controle realizada passa por uma malha de realimentação, causando um atraso na resposta. A Figura 11 mostra um sistema realimentado.

Figura 11 - Sistema realimentado

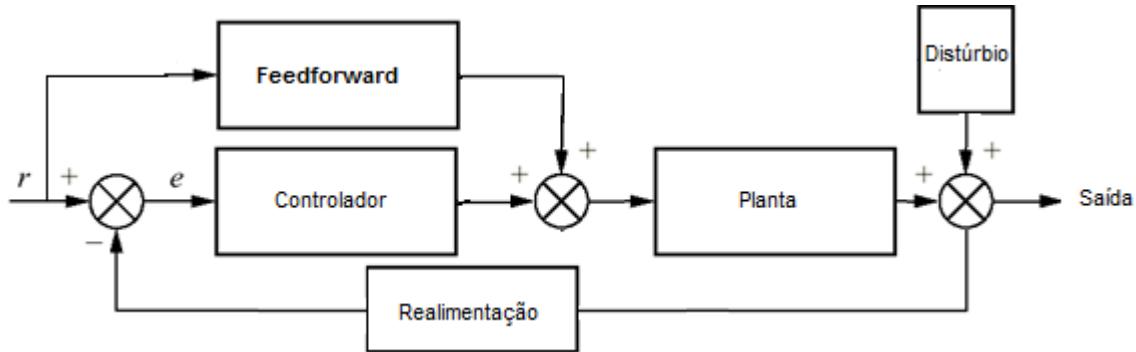

Para um sistema com o controle *Feedforward*, o sinal de referência modificado pela função de transferência do *Feedforward* é diretamente na planta, para realizar a compensação do distúrbio (Figura 12).

Figura 12 - Controlador Feedforward

O controle *Feedforward* não é implementado independente; para a sua atuação é necessária a existência de outro controlador para rastrear o sinal de referência. O controle que vai atuar junto com o *Feedforward* depende da planta e opções de projeto [37]. Está evidente nas Figuras 11 e 12 a existência de um controlador além do *Feedforward*.

O controle *Feedforward* implementado foi o mesmo usado em [8]:  $G_p(z^1) = k_1 z^{-1} + k_1 z^{-2}$ ,  $G_{ff}(z^{-1}) = 1$ ,  $G_h(z^{-1}) = 1$ , para  $K_1=-0,175$  e  $k_2=-0,011$ . Este controlador Feedforward tem como coadjuvante o controle proporcional derivativo, PD-feedforward. O sistema de controle é formado pelas ações de controle Repetitiva, Proporcional Derivativa e *Feedforward*. Conforme apresentado no controle PID, tem-se três ações de controle que, por analogia, estão representadas na implementação. Os controles de ação Proporcional Derivativa e *Feedforward* representam analogicamente a ação proporcional e derivativa semelhante ao PID e a ação integral é representada pela ação repetitiva.

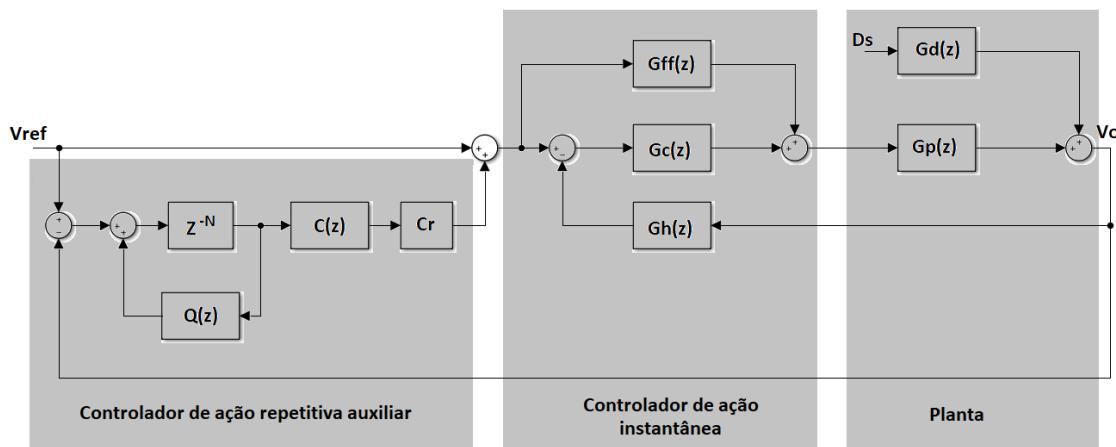

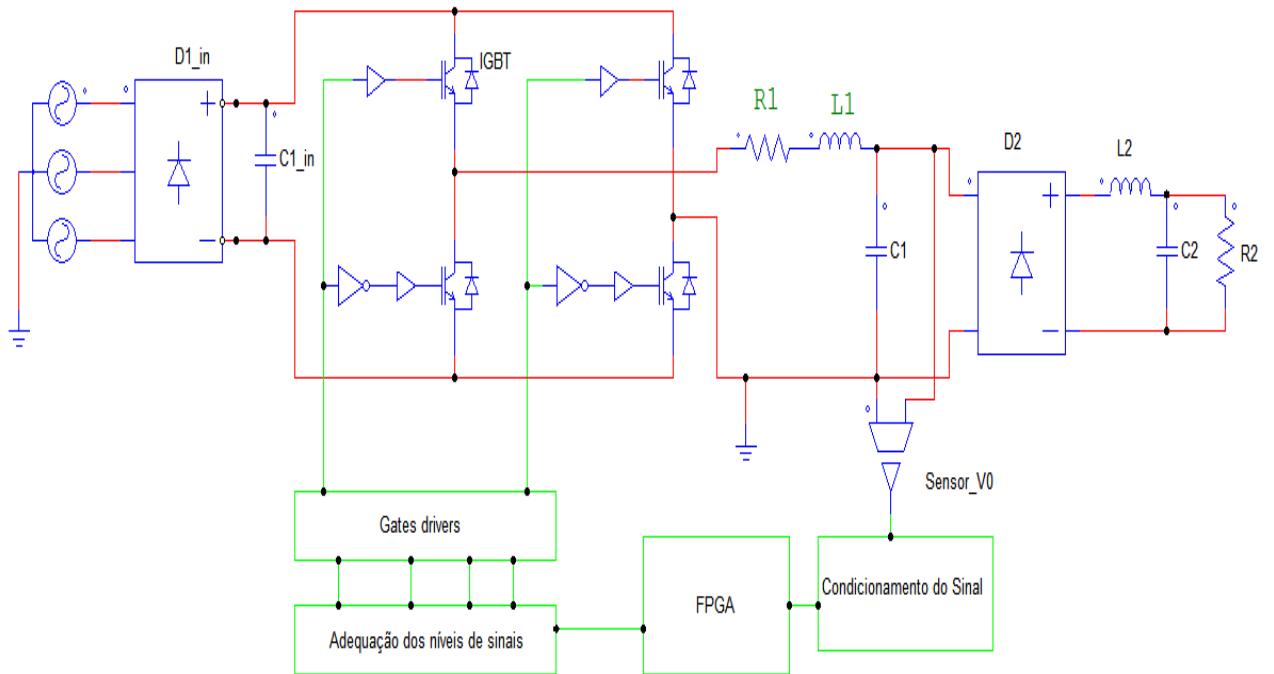

### 3.3 Técnicas de controle aplicadas ao Sistema Inversor de tensão

O controle da tensão de saída do inversor é realizado por dois controladores digitais, o primeiro de ação instantânea, e o segundo de ação repetitiva auxiliar, como mostrado na Figura 13. O objetivo do controle é fazer com que a tensão de

saída  $V_o$  acompanha a referência  $V_{ref}$ , rejeitando a ação do distúrbio  $D_s$  existente na saída da planta. É importante frisar que o controlador de ação instantânea é o elemento principal do controle, o qual tem a função de rejeitar quaisquer distúrbios provocados pela carga ou elo CC do inversor, de forma a seguir a referência. O controlador de ação repetitiva é um coadjuvante, que auxilia o controlador principal seguir a referência rejeitando distúrbios repetitivos como, por exemplo, aqueles gerados por um retificar com filtro capacitivo utilizado como carga.

Figura 13 - Diagrama de controle do inversor com ação de controle instantânea e repetitiva [8]

Como o objetivo principal do presente trabalho foi a implementação do controle embarcado em FPGA, não foi considerado o desenvolvimento ou mesmo o aperfeiçoamento do controlador visando a uma melhor performance do sistema. Assim, as funções e parâmetros dos controladores utilizados foram os mesmos apresentados em [8]:  $G_p(z^1) = k_1 z^{-1} + k_2 z^{-2}$ ,  $G_{ff}(z^{-1}) = 1$ ,  $G_h(z^{-1}) = 1$ , para  $k_1=-0,175$  e  $k_2=-0,011$ , buffer 100 e  $C_r = 0,2$ .

### 3.3.1 Controlador de Ação Instantânea

Existem vários tipos de funções que podem ser aplicadas aos controladores de ação instantânea. Como observado na Figura 13, o controlador de ação instantânea apresenta uma função de realimentação do erro  $G_h(z)$ , uma função de compensação  $G_c(z)$  e uma ação de controle *feedforward* representada pela função

$G_{ff}(z)$ . Conforme dito anteriormente, foram adotadas as funções apresentadas em [8] para o controlador de ação instantânea:

$$G_c(z^{-1}) = K_1 z^{-1} + K_2 z^{-2} \quad (6)$$

$$G_{ff}(z^{-1}) = 1 \quad (7)$$

$$G_h(z^{-1}) = 1 \quad (8)$$

O ganho do sistema de condicionamento de sinais e do sensor de tensão aplicados na aquisição do sinal da tensão de saída do inversor foi compensado por um ganho interno à FPGA, de modo que a função de realimentação  $G_h(z)$  apresentasse ganho unitário. O controlador *Feedforward* também foi configurado com um ganho unitário puro.

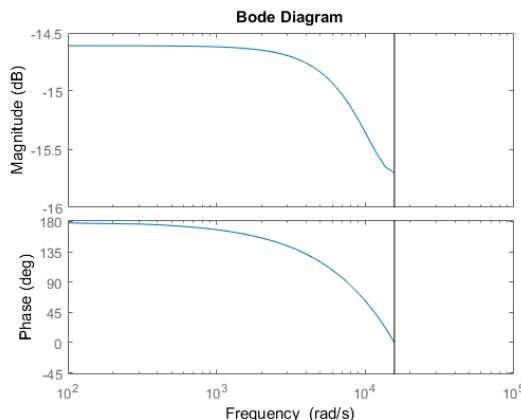

O diagrama de Bode da função  $G_c(z)$ , considerando  $K_1=-0,175$  e  $K_2=-0,011$  [8] e  $fs=5000\text{Hz}$ , pode ser visto na Figura 14, onde observa-se que a função apresenta um avanço de fase para componentes de baixa frequência. Desta forma, o controlador de ação instantânea é dito proporcional-derivativo “*Feedforward*” (PD-feedforward) [8].

Figura 14 - Diagrama de Bode da função  $G_c(z)$  para  $K_1=-0,175$  e  $K_2=-0,011$  e  $fs=5000\text{Hz}$

O controlador PD-feedforward é responsável por rejeitar os distúrbios de carga, mantendo a tensão de saída do inversor atracada com a referência. Para avaliar o desempenho do controlador PD-feedforward, foram realizadas algumas simulações, cujos parâmetros estão na Tabela 1.

Tabela 1 - Parâmetros da simulação Feedforward

| <b>Parâmetros da Planta</b>   |                                    |

|-------------------------------|------------------------------------|

| Barramento CC                 | VCC=200V                           |

| Tensão de referência          | Vref =110 Vrms, f = 50 Hz          |

| Indutor do filtro de saída    | L=1mH                              |

| Capacitor do filtro de saída  | C=30µF                             |

| Frequência de amostragem      | 5000 Hz                            |

|                               |                                    |

| <b>Carga linear</b>           |                                    |

| Carga linear 1                | 40Ω                                |

| Carga linear 2                | 20Ω                                |

|                               |                                    |

| <b>Carga não-linear</b>       |                                    |

| Retificador não controlado    | Ponte de diodos<br>RL=94Ω CL=470µF |

|                               |                                    |

| <b>Parâmetros do controle</b> |                                    |

| fs                            | 5000hz                             |

| K1                            | -0,175                             |

| K2                            | -0.011                             |

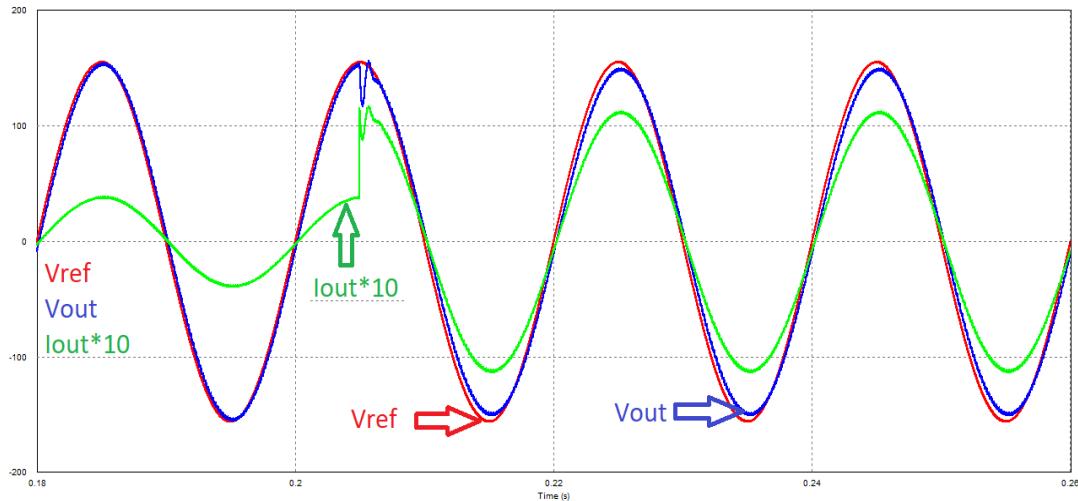

A Figura 15 apresenta a tensão de referência, a tensão de saída e a corrente de saída do inversor para um transitório de carga, onde a carga linear 1 está conectada ao inversor e em  $t=205$  segundos a carga linear 2 é adicionada. Nota-se que a elevação de carga provoca uma queda significativa da tensão de saída no instante de conexão, no entanto o controlador PD-feedforward realiza a regulação da tensão de forma significativa, resultando em um pequeno desvio de amplitude e fase em relação à referência.

Figura 15 - Transitório de elevação de carga linear

Um transitório de redução de carga é mostrado na Figura 16, onde a carga linear 2 é desconectada do inversor. A retirada a carga linear 2 em  $t=0.285$  segundos provoca uma elevação súbita da tensão de saída do inversor, a qual é corrigida prontamente pelo controlador PD-feedforward.

Figura 16 - Transitório de redução de carga linear

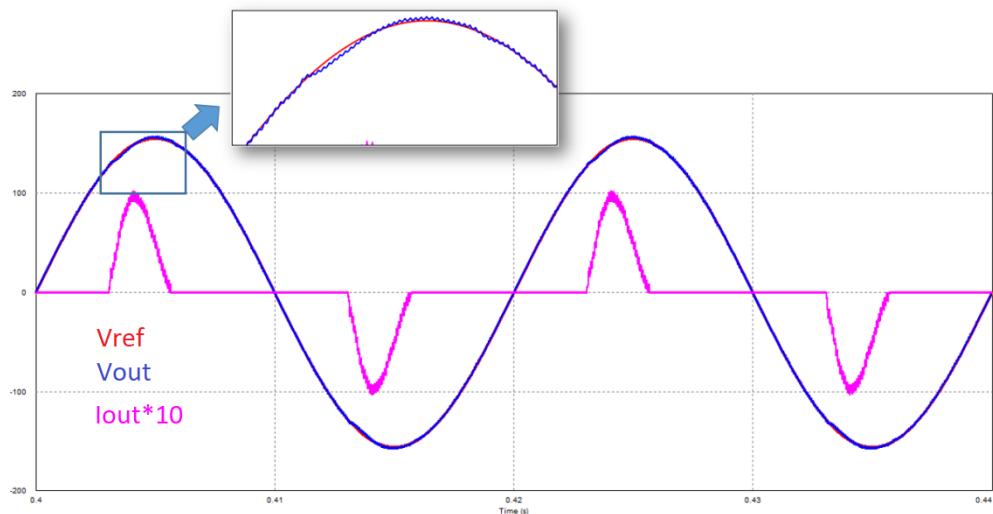

Apesar dos resultados satisfatórios para os transitórios mostrados nas Figuras 15 e 16, o controlador PD-feedforward não é capaz de seguir a tensão de referência para determinados tipos de carga, principalmente para as cargas não lineares. A Figura 17 mostra o desempenho do controlador PD-feedforward para a carga não linear apresentada na Tabela 1. A corrente pulsada requisitada pelo

retificador monofásico não controlado representa uma situação transitória que se repete a cada ciclo de operação da tensão. Nesta situação, a tensão resultante na saída do inversor apresenta uma THD de 7% para uma corrente de carga com 74% de distorção harmônica total. Desta forma, o inversor não atende à norma IEC 62040-3, onde, por exemplo, tem-se os limites de 5%, 6%, 5% e 3,5% para os harmônicos de ordem 3, 5, 7 e 11, respectivamente. É justamente para resolver este problema que recorre-se ao controlador de ação repetitiva, o qual trabalhará em auxílio ao controlador PD-feedforward rejeitando estes distúrbios da carga, os quais são repetitivos. O controlador de ação repetitiva será apresentado na próxima seção.

Figura 17 - Desempenho do controlador PD-feedforward para uma carga não linear

### 3.3.2 Controlador de Ação Repetitiva

O controlador de Ação Repetitiva apresentado na seção 2.2.2, que foi incluído na Figura 13 do diagrama de controle, está na forma tradicional. Trata-se de um compensador formado por conjunto de integradores, descritos como  $(1/[1 - Q(z^{-1})z^{-N}])$  [8]. A integração corresponde à amostragem de um período da frequência de referência do sinal de erro. Os integradores operam em uma sequência formada por um atraso ( $z^{-N}$ ), um ganho  $c_r$  e o filtro  $C(z^{-1})$ , conforme pode ser visto nas Figuras 9 e 10. A função de transferência para o controlador Repetitivo para a versão Filtro Q é:

$$G_{rp}(z^{-1}) = \frac{1}{1 - Q(z^{-1})z^{-N}} z^{-N} c_r C(z^{-1}) \quad (9)$$

O valor de N na função de transferência refere-se à quantidade de amostras por um período do sinal de referência, sendo definida por:

$$N = \frac{T_1}{T_s}, N \in N^+ \quad (10)$$

Sendo  $T_1$  o período da referência.

Em relação ao compensador  $C(z^{-1})$ , deve-se destacar que, conforme [8, p. 73],

é empregado para compensar os atrasos de fase entre os geradores de sinais periódicos e a saída da planta, inserindo, desta forma, a ação de compensação aos distúrbios na planta com fase adequada. Como esta compensação de atraso de fase da planta só pode ser feita por um filtro com ação não-causal, é incluída a estrutura  $z^{-N}$  para tornar  $C(z^{-1})$  causal. Desta forma, se atrasa a atuação da ação de controle em um período do sinal de referência. O ganho  $c_r$  pode ser considerado como sendo uma parte do filtro  $C(z^{-1})$ , que é adequadamente ajustado para se garantir a estabilidade da lei de controle.

Os parâmetros de configuração para esta função de transferência implementada estão na Tabela 2.

Tabela 2 - Parâmetros dos controles Repetitivos

| <b>Parâmetros dos controles Repetitivos</b> |      |

|---------------------------------------------|------|

| $z^{-Nd}$                                   | 98   |

| $z^{-N}$                                    | 100  |

| N                                           | 100  |

| Q                                           | 0.99 |

| $C_r$                                       | 0.2  |

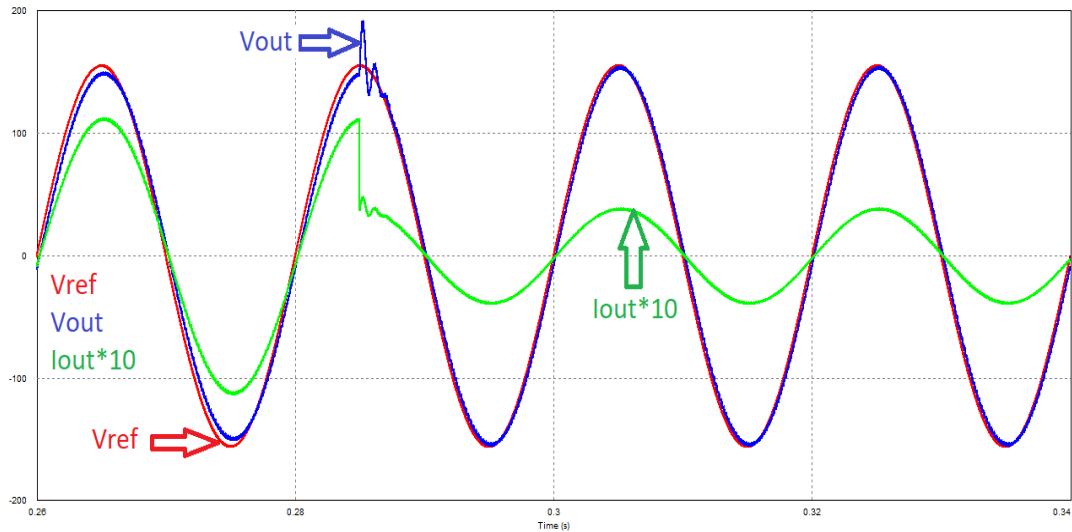

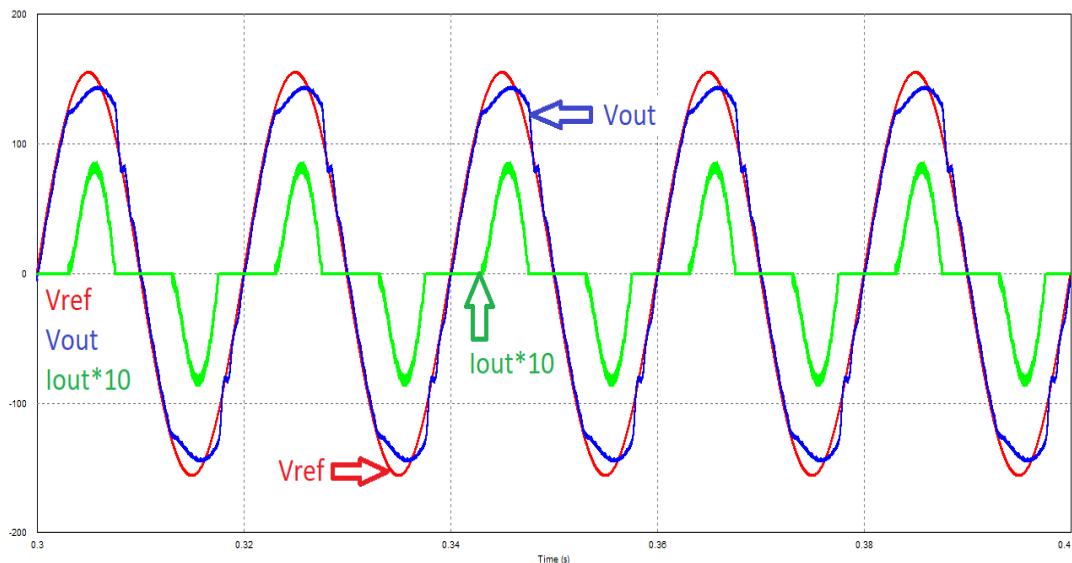

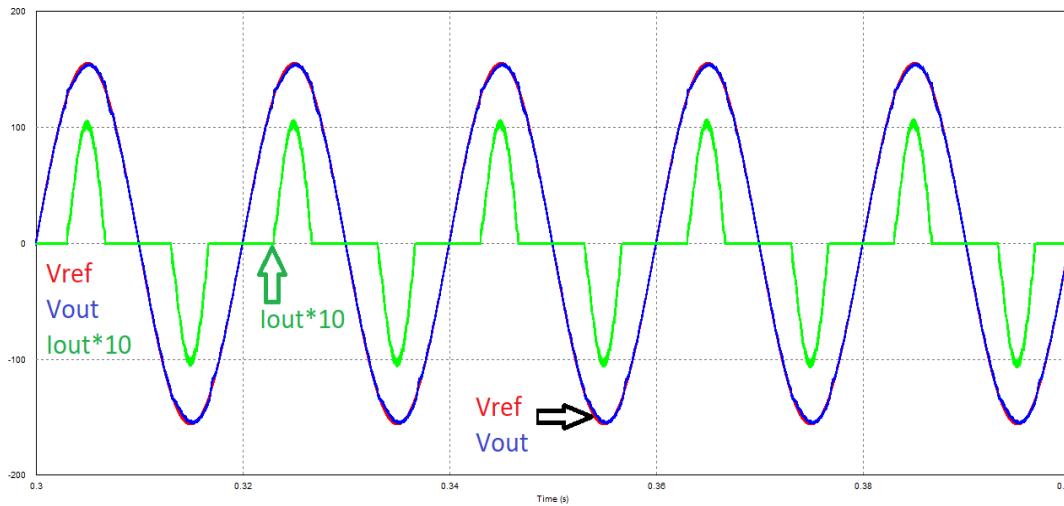

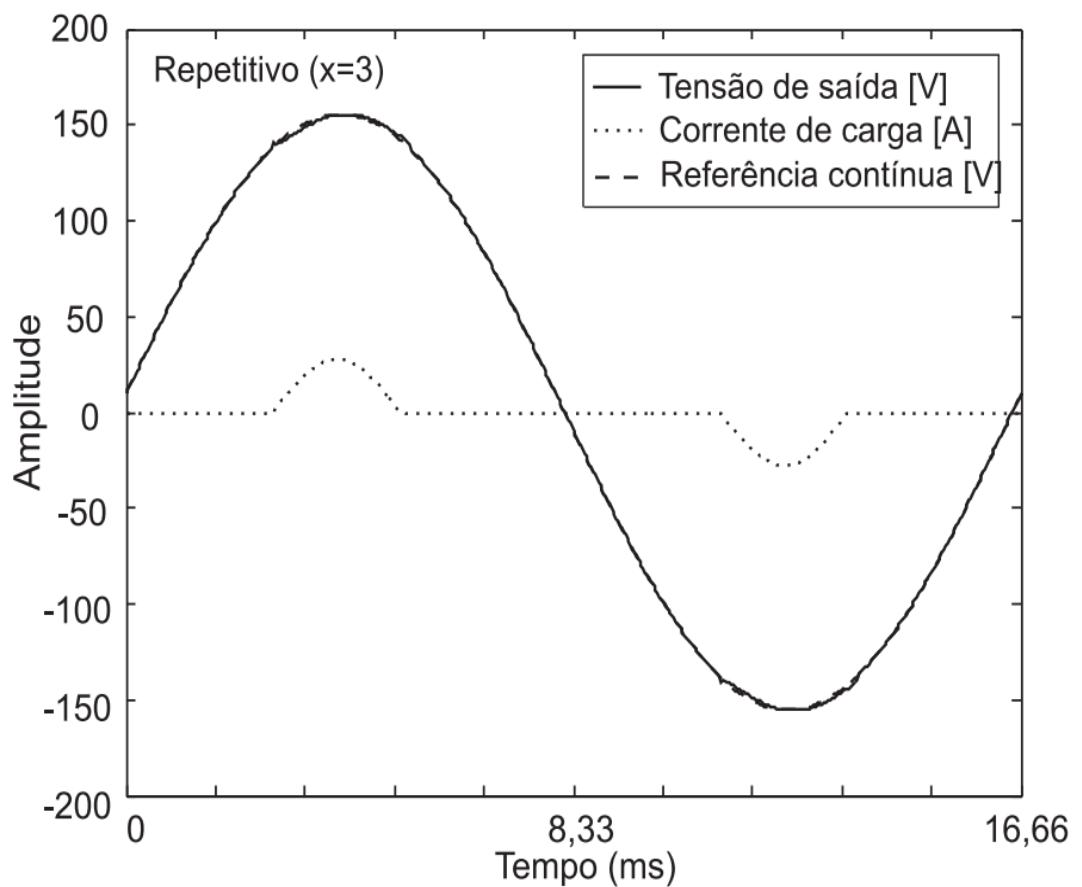

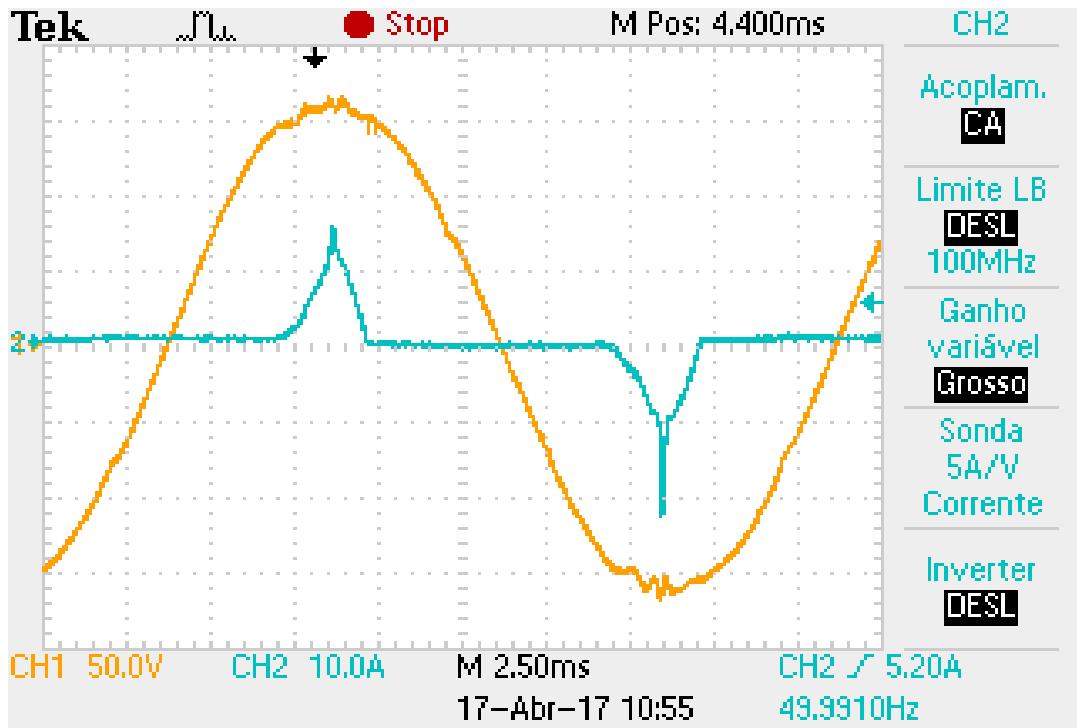

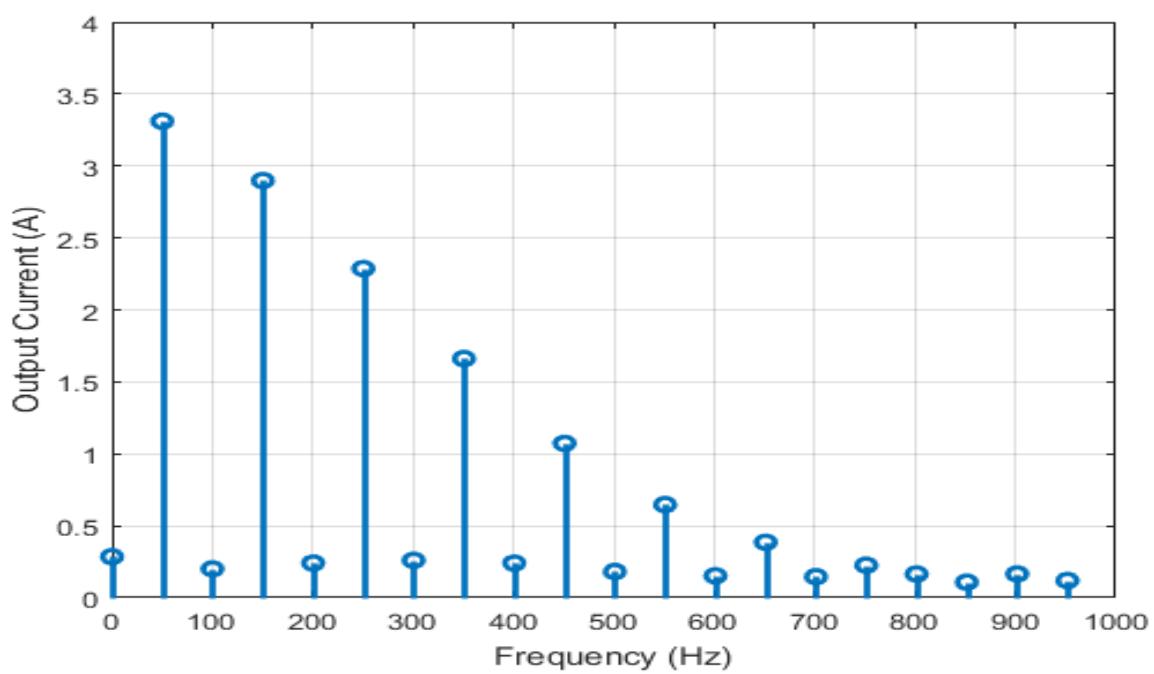

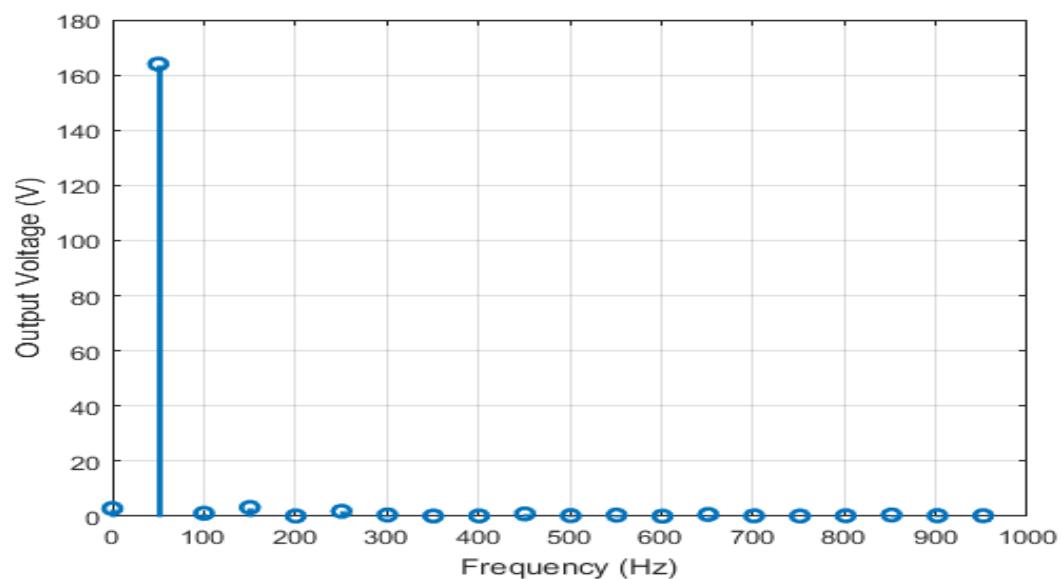

A Figura 18 mostra o desempenho do sistema para a mesma carga não linear mostrada na Figura 16, mas agora com a inclusão do controlador de ação repetitiva. Observa-se uma melhora significativa na forma de onda da tensão de

saída, a qual apresenta uma THD de 1.2% para uma THD da corrente de saída de 90%.

Figura 18 - Desempenho do controlador PD-feedforward + Repetitivo para uma carga não linear

#### 4 METODOLOGIA

Durante o desenvolvimento da pesquisa houve uma série de correções de rota no que diz respeito à metodologia para a implementação do controle embarcado em FPGA. Em um primeiro momento, pensou-se em usar a geração do código a partir da linguagem VHDL (*VHSI Hardware Description Language*) e fez-se um estudo da mesma. A partir desse estudo, ficou evidente o potencial que esta linguagem oferece para implementar circuitos eletrônicos, mas também foi revelada a dificuldade de gerenciar circuitos maiores como o pretendido. Problemas como ter que controlar todos os sinais, gerar o controle de tempo para a sincronização dos sinais e a incalculável quantidade de entidades que deveriam ser implementadas levaram à conclusão de que, para este projeto, seria muito trabalho e o tempo de projeto seria aumentado drasticamente, sem contar o gerenciamento de problemas intrínsecos da FPGA. Por isso, para o desenvolvimento de todo o controle embarcado em FPGA, não seria viável usar o VHDL para sua implementação. A dificuldade de desenvolver todo o projeto diretamente em VHDL é destacado em [38], onde o autor relata não ter conseguido implementar por exemplo um controlador PWM.

## 4.1 System Generator

Devido à constatação da dificuldade de uso da linguagem VHDL, foi pesquisada outra solução de “programação” com maior nível de abstração [38]. Entrou em cena o *System Generator*. O *System Generator* apresentou de imediato vários benefícios: linguagem gráfica, o gerenciamento de sinais e tempos, facilidade de trabalhar com ponto fixo, interação com o ambiente Simulink do Matlab. A partir das vantagens apresentadas, definiu-se a opção pelo *System Generator*.

A primeira vantagem foi com relação à geração do código bitstream. O *System Generator* gera o código a partir do projeto em modo gráfico até alcançar o bitstream em apenas um comando. Com isso, ficam ocultas todas as fases de geração de código para a FPGA. Isso significa um ganho de tempo muito importante quando se tem que realizar este procedimento diversas vezes [39].

O *System Generator* destaca-se pela sua interface de interação com o usuário, realizada junto com o Simulink do Matlab. Nesta interface, o *System Generator* é uma *toolbox*, instalada no Simulink. Dessa forma, todo o ambiente do Simulink fica disponível para ser usado junto com o *System Generator*.

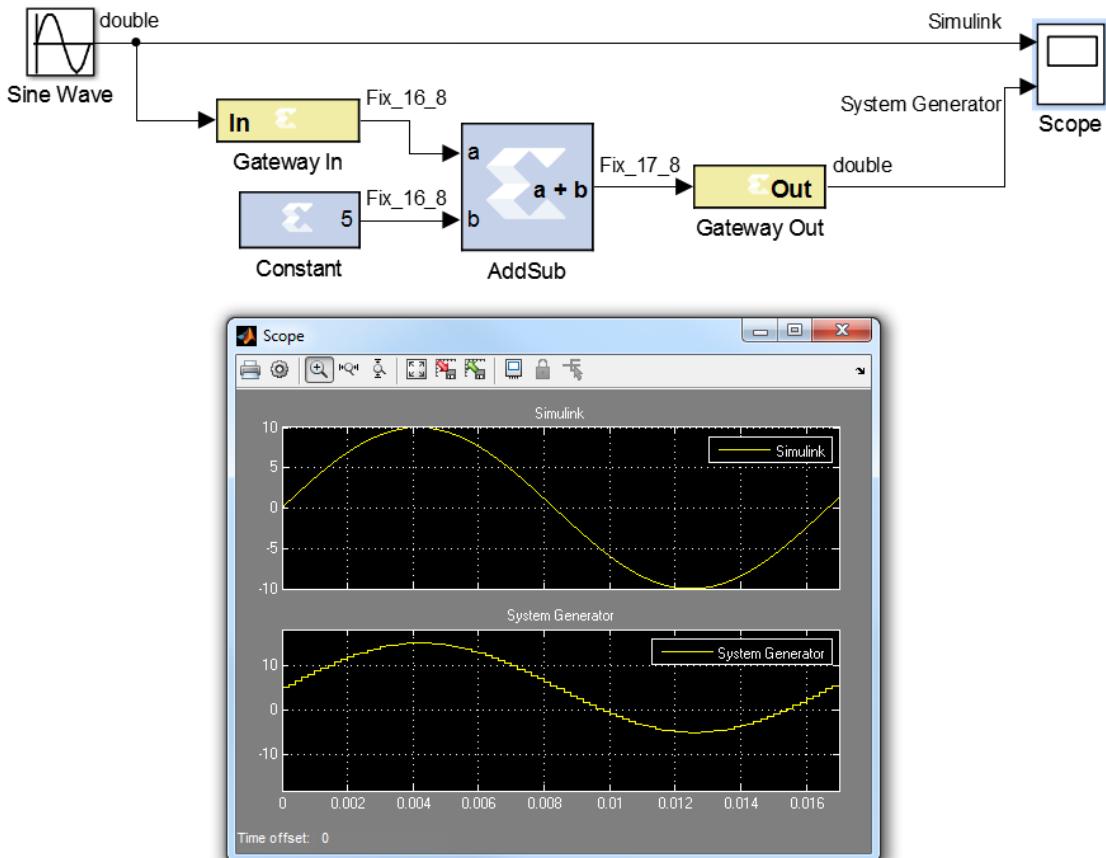

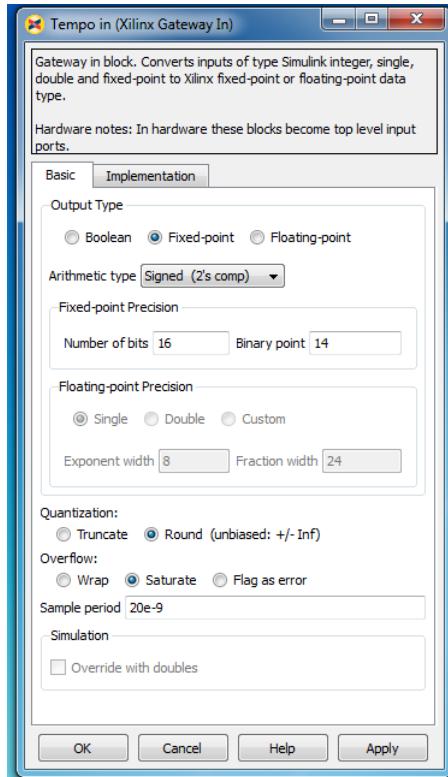

O *System Generator* oferece dois componentes que permitem fazer a interação entre estes dois ambientes: o *gateway out* e o *gateway in*. O *gateway out* devolve para o ambiente do Simulink os sinais da FPGA no formato de precisão dupla (*Double-Precision Floating Point*), ou seja, ponto flutuante com 64bits. Por outro lado, tem-se o *gateway in*, que realiza a operação inversa, ou seja, converte um sinal de saída do Simulink em ponto flutuante de precisão dupla para sinal de entrada da FPGA no formato ponto fixo, de acordo com a configuração preestabelecida. Este componente pode ser configurado para gerar a resolução de ponto fixo desejada. Com isso, a interação do *System Generator* com o Simulink fica muito “forte”, permitindo interagir com todas as bibliotecas do Simulink. A Figura 19 apresenta os blocos *Gateway in* e *out* de forma didática.

Figura 19 - Gateways

O bloco *Gateway* revela uma das facilidades de converter a representação dos números de ponto flutuante para ponto fixo (o número, para ser representado em ponto fixo, é dividido em duas partes: uma para representar a parte inteira e outra para a parte fracionária, e cada qual pode ter um determinado número de bits, de acordo com a precisão desejada). Este processo é transparente para o usuário. É suficiente colocar o formato desejado (número de bits para a parte inteira e fracionária). Na Figura 20 tem-se a interface de configuração do *Gateway In*, com a representação de S.1.14 (16 bits total, divididos da seguinte forma: 1 bit de sinal, 1 para parte inteira e 14 para a parte fracionária). Além dessa representação, também temos booleana e ponto flutuante.

Figura 20 - Gateway In

Outro aspecto importante, visto que a aplicação envolve um controlador no domínio do tempo discreto, é que a forma de amostragem pode ser facilmente determinada através da divisão do clock base disponível na placa da FPGA. Este fato torna possível a aquisição de qualquer sinal do Simulink para FPGA. Nesse sentido, pode-se trabalhar com qualquer sistema analógico no Simulink cujo sinal vai ser diretamente amostrado para FPGA.

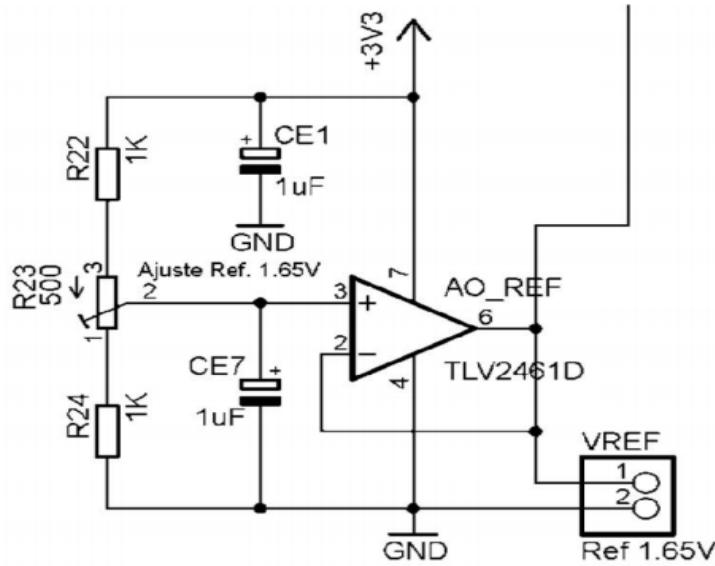

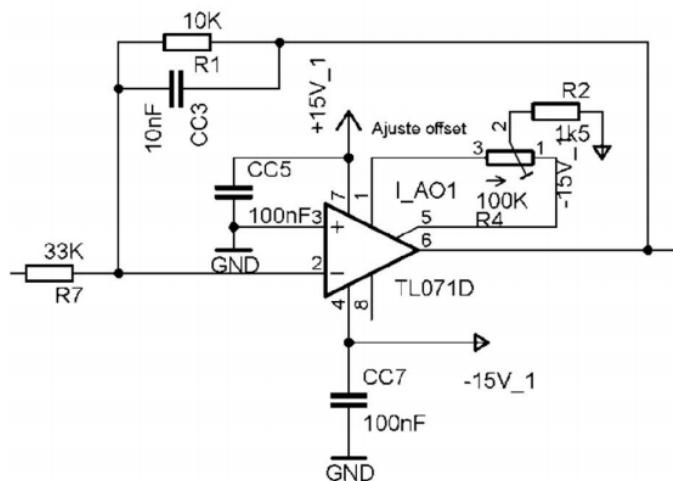

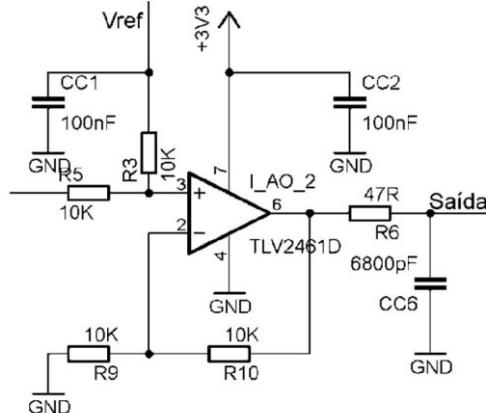

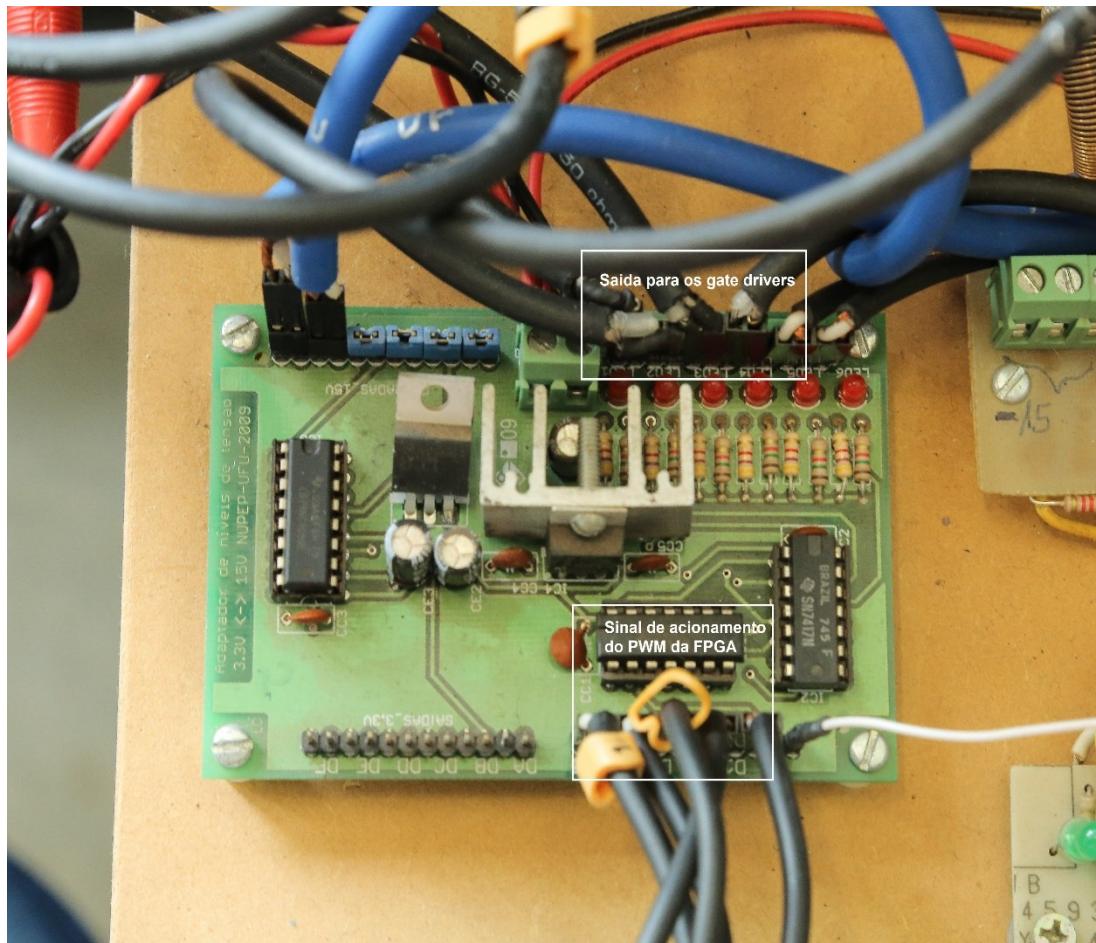

As simulações envolvendo o *System Generator* são *bit-True and Cycle-True Modeling*. *Bit-True* significa que os dados na fronteira, *Gateway in* e *Gateway out*, entre o *System Generator* e demais blocos do Simulink são correspondentes bit a bit. *Cycle-true* que dizer que os dados são apresentados na fronteira na taxa de amostragem definida pelo passo de simulação [39]. Em suma, isto quer dizer que o comportamento das variáveis é exatamente aquele realizado em *hardware* pela FPGA. Os ciclos de tempo das interfaces de *Gateway in* e *Gateway out* serão os mesmos da simulação e do hardware, fato que foi constatado em vários testes(comparação de períodos e resultados de operações) preliminares realizados para uso no desenvolvimento inicial dos controladores estudados neste trabalho.