# **Capítulo 4**

## **Implementação da Estratégia de Controle Utilizando DSP**

### **4.1 Considerações Iniciais**

Neste capítulo é apresentado o fluxograma do código de controle desenvolvido para execução da estratégia de controle do RHT utilizando um Processador Digital de Sinais. O DSP escolhido foi o *TMS320F28335* da *Texas Instruments*<sup>®</sup>, devido à sua alta capacidade de processamento e também por apresentar suporte à arquitetura de ponto flutuante, conforme mencionando no Capítulo 2.

São detalhadas também as características das principais variáveis e constantes utilizadas no código de controle, bem como a forma de configuração dos principais registros responsáveis pelo funcionamento do DSP para a implementação da estratégia de controle proposta.

### **4.2 Fluxograma do Código de Controle**

A Fig. 4.1 ilustra o fluxograma baseado nas ações realizadas pelo algoritmo de controle<sup>2</sup> desenvolvido em linguagem ‘C’ para o processador digital *TMS320F28335* da *Texas Instruments*<sup>®</sup>, utilizado no controle do RHT.

---

<sup>2</sup> Ver Apêndice B – Algoritmo de Controle

Início

Declaração de Variáveis

Configuração do Sistema de Controle

Configuração dos Pinos de Propósito Geral

Configuração do Conversor Analógico Digital (ADC)

Configuração dos Registros ePWM

Amostragem dos Sinais pelo ADC

Amostras Completas?

Chamada da Rotina de Interrupção do ADC

Armazenamento das Amostras em Variáveis

Retificação de  $I_{inA}$ ,  $I_{inB}$  e  $I_{inC}$

Módulo de Sincronismo

Geração das Referências Senoidais  $I_{RefA}$ ,  $I_{RefB}$  e  $I_{RefC}$

Módulo de Geração de Pulso

Incremento de  $cont$

Cálculo do Valor Médio de  $Io$  ( $Io\_med$ )

Início

Sim  $cont \leq BUFSIZE?$  Não

$cont = 0$

Configura os Pinos 12, 13 e 33 do DSP com nível baixo

Fim

(a)

(b)

Início

$V_{inA\_pass}$  recebe o valor de  $V_{inA}$

$V_{inA}$  recebe o valor de  $AdcRegs.ADCRESULT1$

$Produto = V_{inA} * V_{inA\_pass}$

$Produto \leq 0?$

Sim

$cont = 0$

Reinicia o cálculo de  $Io\_med$

Fim

(c)

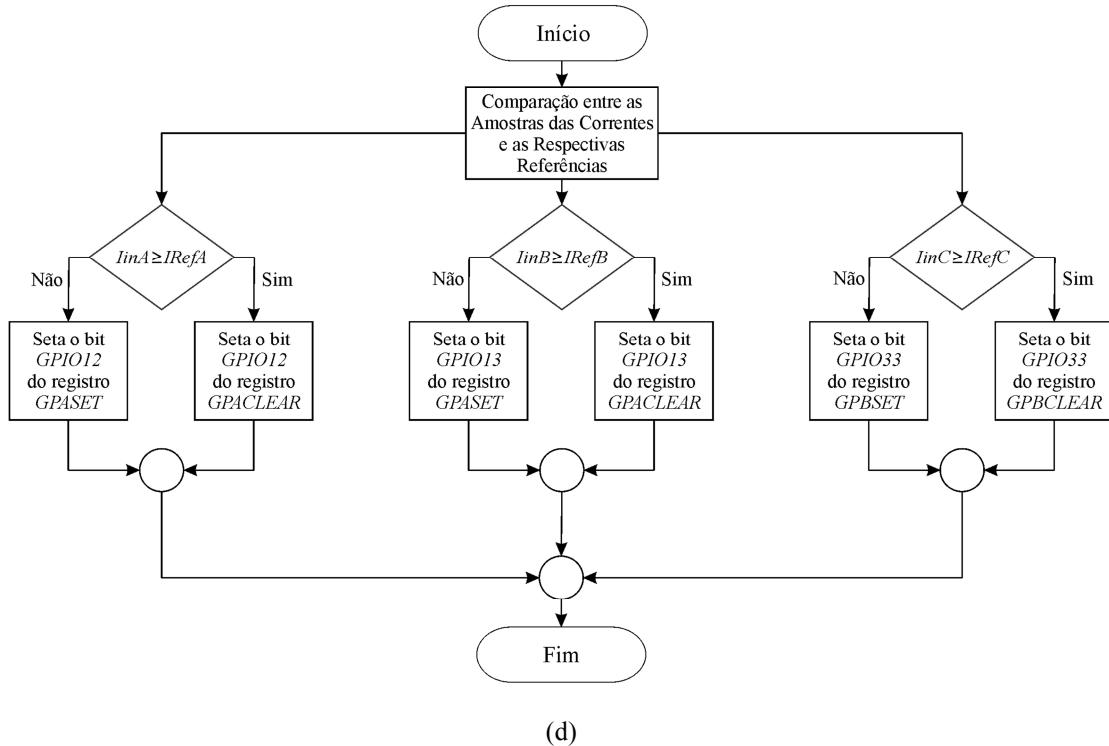

Fig. 4.1 – Fluxograma (a) do algoritmo de controle, (b) da rotina de interrupção do ADC, (c) do módulo de sincronismo e (d) do módulo de geração de pulsos.

## 4.3 Etapas de Execução do Código de Controle

A explicação do código de controle foi dividida em seis etapas que são detalhadas nas subseções que se seguem.

### 4.3.1 Criação das Variáveis e Constantes

Nesta etapa todas as variáveis e constantes criadas para a implementação do controle do retificador híbrido trifásico são declaradas. A Tab. 4.1 descreve as variáveis e constantes mais importantes para a execução do algoritmo de controle.

Vale comentar que o vetor  $I_{sen}$  contém todos os pontos de uma senóide pura retificada de amplitude unitária e frequência de 60 Hz gerada no software *Matlab*<sup>®</sup>. Seguindo o teorema de *Nyquist* que estabelece que a frequência de amostragem seja pelo menos duas vezes maior que o valor da frequência de chaveamento, adotou-se uma frequência de amostragem de 100 kHz (período de amostragem de 10  $\mu$ s) para as aquisições realizadas pelo conversor Analógico-Digital do DSP, uma vez que, conforme mencionado no Capítulo 2, a frequência de chaveamento é limitada em 20 kHz pela dinâmica do sistema, onde os capacitores e indutores são projetados para esta frequência.

Tab. 4.1 – Variáveis criadas para a execução do código de controle.

| Variável                                   | Descrição                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>BUFSIZE</i>                             | Número de amostras realizadas durante a aquisição dos sinais sensoriados. Para uma janela de 16.67 ms (frequência de 60 Hz) e uma frequência de amostragem de 100 kHz, são realizadas 1667 amostras por ciclo de onda.                                                                                      |

| <i>k</i>                                   | Ganho fixo a ser multiplicado ao vetor <i>IRef</i> a fim de se manter o nível de DHT <sub>1</sub> das correntes de linha de entrada necessário e determinar que o percentual de processamento de potência por parte dos conversores chaveados seja de 40% em relação a potência ativa média total de saída. |

| <i>cont</i>                                | Contador que é incrementado à cada chamada da rotina de interrupção.                                                                                                                                                                                                                                        |

| <i>Io</i>                                  | Variável onde são armazenadas as amostras provenientes da aquisição da corrente na carga ( <i>I<sub>o</sub></i> ).                                                                                                                                                                                          |

| <i>Io_med</i>                              | Ganho variável a ser multiplicado ao vetor <i>Isen</i> , proporcional à corrente de carga, representado pela média dos valores de <i>I<sub>o</sub></i> calculada a cada amostragem. Este ganho determina que a amplitude da referência varie conforme as alterações de carga.                               |

| <i>InA</i> , <i>InB</i> e <i>InC</i>       | Variáveis onde são armazenadas as amostras provenientes da aquisição das correntes de linha de entrada das fases A, B e C do retificador híbrido trifásico ( <i>i<sub>a(in)</sub></i> , <i>i<sub>b(in)</sub></i> e <i>i<sub>c(in)</sub></i> ).                                                              |

| <i>VinA</i>                                | Variável onde são armazenadas as amostras provenientes da aquisição da tensão de alimentação da fase A ( <i>v<sub>an</sub></i> ). Destaca-se que a aquisição da tensão de fase <i>v<sub>an</sub></i> é utilizada exclusivamente para fins de sincronismo.                                                   |

| <i>VinA_pass</i>                           | Variável onde são armazenadas as amostras de um período de amostragem passado provenientes da aquisição da tensão de alimentação <i>v<sub>an</sub></i> .                                                                                                                                                    |

| <i>Produto</i>                             | Produto entre as variáveis <i>VinA</i> e <i>VinA_pass</i> , utilizado para a identificação da passagem por zero da tensão de alimentação <i>v<sub>an</sub></i> .                                                                                                                                            |

| <i>IRefA</i> , <i>IRefB</i> e <i>IRefC</i> | Variáveis onde são armazenados os valores do vetor <i>Isen</i> nas posições <i>cont</i> , <i>cont+555</i> e <i>cont+278</i> , respectivamente, multiplicados por <i>Io_med</i> e <i>k</i> .                                                                                                                 |

| <i>Isen</i>                                | Vetor de <i>BUFSIZE</i> posições, onde são armazenados os valores de uma senóide pura retificada criada digitalmente.                                                                                                                                                                                       |

Uma vez que a frequência de amostragem (*f<sub>a</sub>*) foi estabelecida em 100 kHz e os sinais aquisicionados pelo conversor A/D do DSP apresentam-se na frequência da rede (60 Hz), o número de amostras geradas para um ciclo completo de onda é determinado pela Eq. (4.1).

$$BUFSIZE = \frac{T}{T_a} = \frac{\frac{1}{f}}{\frac{1}{f_a}}$$

$$BUFSIZE = \frac{\frac{1}{60}}{\frac{1}{100 \cdot 10^3}} = 1667 \quad (4.1)$$

Portanto é possível realizar a aquisição de um ciclo de onda completo dos sinais das correntes de linha de entrada e da tensão da fase A em 1667 amostras, o que

determina que vetor de referência *Isen* seja gerado com o número de posições igual a *BUFSIZE*.

### 4.3.2 Configuração do Sistema de Controle do DSP

Uma vez declaradas as variáveis, inicia-se então a configuração do Sistema de Controle do DSP. Essa parte do código de controle tem por objetivo ajustar o funcionamento básico do DSP. O principal registro para configuração do Sistema de Controle é o *HISPCP* (*High-Speed Peripheral Clock Prescaler*). Este registro, uma vez configurado, determina o *clock* de operação do processador, habilitando a utilização deste em alguns periféricos, tal como o conversor A/D. A Tab. 4.2 demonstra a representação da configuração dos bits do *HISPCP*.

Tab. 4.2 – Configuração do *HISPCP* (*High-Speed Peripheral Clock Prescaler*).

| Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Reserv. |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  |

|---------|---------|---------|---------|---------|--------|--------|--------|

| Reserv. | Reserv. | Reserv. | Reserv. | Reserv. | HSPCLK | HSPCLK | HSPCLK |

| 0       | 0       | 0       | 0       | 0       | 0      | 0      | 1      |

A configuração dos bits 2-0 do *HISPCP* estabelece a frequência de *clock* utilizada nos processos realizados pelo DSP (*HSPCLK* – *High-Speed Peripheral Clock*) em relação a divisores da frequência nominal de saída (*SYSCLKOUT*) do *TMS320F28335*. Se a configuração dos bits do *HSPCLK* for estabelecido com valor 000b, tem-se que a frequência de *clock* é igual frequência nominal de saída do DSP:

$$HSPCLK = SYSCLKOUT = 150 \text{ MHz} \quad (4.2)$$

Caso o valor dos bits do *HSPCLK* for configurado entre 001b (1h) e 111b (7h), a frequência de *clock* pode se determinada pela Eq. (4.3).

$$HSPCLK = \frac{SYSCLKOUT}{2 \cdot n} \quad (4.3)$$

Onde *n* é o valor em decimal configurado nos bits 2-0 do *HISPCP*.

Como foi utilizado um valor de *HISPCP* igual a 1h, logo o valor configurado para *HSPCLK* é 001b (*n* igual a 1), e, portanto a frequência de *clock* é determinada através de (4.3) como sendo igual a:

$$HSPCLK = \frac{150 \cdot 10^6}{2 \cdot I} = 75 \text{ MHz}$$

### 4.3.3 Configuração dos Pinos de Propósito Geral

Configurados os registros do Sistema de Controle do DSP, dá-se início à configuração dos pinos de propósito geral. O *TMS320F28335* possui diversos pinos de entrada e saída digital (*GPIO*). Como muitos destes pinos são compartilhados com funções periféricas, os mesmos devem ser configurados para que possam operar adequadamente para uma função específica. Os registros *GPAMUX1* (*GPIO A Register Bit to I/O Mapping*) e o *GPBMUX1* (*GPIO B Register Bit to I/O Mapping*) são dois destes registros de configuração que determinam, por exemplo, se o pino GPIO 1 operará como pino de I/O digital, PWM ou *Capture*. As Tab. 4.3 e 4.4 demonstram a configuração dos bits destes registros.

Configurando-se os bits 25-24 e 27-26 do *GPAMUX1* e os bits 3-2 do *GPBMUX1* com o valor 00b, determinam-se os pinos de propósito gerais 12, 13 e 33 do DSP para operarem como pinos de I/O (entrada/saída).

Tab. 4.3 – Configuração do *GPAMUX* (*GPIO A Register Bit to I/O Mapping*).

| Bits  | GPAMUX1 bits = 00 | GPAMUX1 bits = 01     | GPAMUX1 bits = 10 | GPAMUX1 bits = 11   |

|-------|-------------------|-----------------------|-------------------|---------------------|

| 1-0   | GPIO0             | EPWM1A (O)            | Reserved          | Reserved            |

| 3-2   | GPIO1             | EPWM1B (O)            | ECAP6 (I/O)       | MFSRB (I/O)         |

| 5-4   | GPIO2             | EPWM2A (O)            | Reserved          | Reserved            |

| 7-6   | GPIO3             | EPWM2B (O)            | ECAP5 (I/O)       | MCLKRB (I/O)        |

| 9-8   | GPIO4             | EPWM3A (O)            | Reserved          | Reserved            |

| 11-10 | GPIO5             | EPWM3B (O)            | MFSRA (I/O)       | ECAP1 (I/O)         |

| 13-12 | GPIO6             | EPWM4A (O)            | EPWMSYNCO (I)     | (O)                 |

| 15-14 | GPIO7             | EPWM4B (O)            | MCLKRA (I/O)      | ECAP2 (I/O)         |

| 17-16 | GPIO8             | EPWM5A (O)            | CANTXB (O)        | <u>ADCSOCAO</u> (O) |

| 19-18 | GPIO9             | EPWM5B (O)            | SCITXDB (O)       | ECAP3 (I/O)         |

| 21-20 | GPIO10            | EPWM6A (O)            | CANRXB (I)        | <u>ADCSOCBO</u> (O) |

| 23-22 | GPIO11            | EPWM6B (O)            | SCIRXDB (I)       | ECAP4 (I/O)         |

| 25-24 | GPIO12            | <u>TZ1</u> (I)        | CANTXB (O)        | MDXB (O)            |

| 27-26 | GPIO13            | <u>TZ2</u> (I)        | CANRXB (I)        | MDRB (I)            |

| 29-28 | GPIO14            | <u>TZ3/XHOLD</u> (I)  | SCITXDB (O)       | MCLKXB (I/O)        |

| 31-30 | GPIO15            | <u>TZ4/XHOLDA</u> (O) | SCIRXDB (I)       | MFSXB (I/O)         |

Tab. 4.4 – Configuração do *GPBMUX* (*GPIO B Register Bit to I/O Mapping*).

| Bits  | GPAMUX1 bits = 00 | GPAMUX1 bits = 01 | GPAMUX1 bits = 10                 | GPAMUX1 bits = 11                 |

|-------|-------------------|-------------------|-----------------------------------|-----------------------------------|

| 1-0   | GPIO32 (I/O)      | SDAA (I/OC)       | EPWMSYNCI (I)                     | $\overline{\text{ADCSOCAO}}$ (O)  |

| 3-2   | GPIO33 (I/O)      | SCLA (I/OC)       | EPWMSYNC0 (O)                     | $\overline{\text{ADCSOCBO}}$ (O)  |

| 5-4   | GPIO34 (I/O)      | ECAP1 (I/O)       | XREADY (I)                        | XREADY (I)                        |

| 7-6   | GPIO35 (I/O)      | SCITXDA (O)       | $\overline{\text{XR/W}}$ (O)      | $\overline{\text{XR/W}}$ (O)      |

| 9-8   | GPIO36 (I/O)      | SCIRXDA (I)       | $\overline{\text{XZCS0}}$ (O)     | $\overline{\text{XZCS0}}$ (O)     |

| 11-10 | GPIO37 (I/O)      | ECAP2 (I/O)       | $\overline{\text{XZCS7}}$ (O)     | $\overline{\text{XZCS7}}$ (O)     |

| 13-12 | GPIO38 (I/O)      | Reserved          | $\overline{\text{XWE0}}$ (O)      | $\overline{\text{XWE0}}$ (O)      |

| 15-14 | GPIO39 (I/O)      | Reserved          | XA16 (O)                          | XA16 (O)                          |

| 17-16 | GPIO40 (I/O)      | Reserved          | XA0/ $\overline{\text{XWE1}}$ (O) | XA0/ $\overline{\text{XWE1}}$ (O) |

| 19-18 | GPIO41 (I/O)      | Reserved          | XA1 (O)                           | XA1 (O)                           |

| 21-20 | GPIO42 (I/O)      | Reserved          | XA2 (O)                           | XA2 (O)                           |

| 23-22 | GPIO43 (I/O)      | Reserved          | XA3 (O)                           | XA3 (O)                           |

| 25-24 | GPIO44 (I/O)      | Reserved          | XA4 (O)                           | XA4 (O)                           |

| 27-26 | GPIO45 (I/O)      | Reserved          | XA5 (O)                           | XA5 (O)                           |

| 29-28 | GPIO46 (I/O)      | Reserved          | XA6 (O)                           | XA6 (O)                           |

| 31-30 | GPIO47 (I/O)      | Reserved          | XA7 (O)                           | XA7 (O)                           |

Nas Tab. 4.5 e 4.6 são representados os bits dos registros *GPADIR* (*GPIO Port A Direction*) e *GPBDIR* (*GPIO Port B Direction*). Estes registros estabelecem se os pinos de I/O serão definidos como entradas ou saídas, configurando-se seus bits com valores 0 ou 1 respectivamente. Setando-se os bits 12 e 13 do *GPADIR* e o bit 33 do *GPBDIR*, define-se os pinos 12, 13 e 33 do DSP como pinos de saída.

Tab. 4.5 – Configuração dos registros *GPADIR* (*GPIO Port A Direction*), *GPASET* (*GPIO A Data Set Register*) e *GPACLEAR* (*GPIO A Data Clear Register*).

| Bit 31   | Bit 30   | Bit 29   | Bit 28   | Bit 27   | Bit 26   | Bit 15   | Bit 24   |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO31   | GPIO30   | GPIO29   | GPIO28   | GPIO27   | GPIO26   | GPIO25   | GPIO24   |

| <b>0</b> |

| Bit 23   | Bit 22   | Bit 21   | Bit 20   | Bit 19   | Bit 18   | Bit 17   | Bit 16   |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO23   | GPIO22   | GPIO21   | GPIO20   | GPIO19   | GPIO18   | GPIO17   | GPIO16   |

| <b>0</b> |

| Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO15   | GPIO14   | GPIO13   | GPIO12   | GPIO11   | GPIO10   | GPIO9    | GPIO8    |

| <b>0</b> | <b>0</b> | <b>1</b> | <b>1</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> |

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO7    | GPIO6    | GPIO5    | GPIO4    | GPIO3    | GPIO2    | GPIO1    | GPIO0    |

| <b>0</b> |

Tab. 4.6 – Configuração dos registros *GPBDIR* (*GPIO Port B Direction*), *GPBSET* (*GPIO B Data Set Register*) e *GPBCLEAR* (*GPIO B Data Clear Register*).

| Bit 31   | Bit 30   | Bit 29   | Bit 28   | Bit 27   | Bit 26   | Bit 15   | Bit 24   |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO63   | GPIO62   | GPIO61   | GPIO60   | GPIO59   | GPIO58   | GPIO57   | GPIO56   |

| <b>0</b> |

| Bit 23   | Bit 22   | Bit 21   | Bit 20   | Bit 19   | Bit 18   | Bit 17   | Bit 16   |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO55   | GPIO54   | GPIO53   | GPIO52   | GPIO51   | GPIO50   | GPIO49   | GPIO48   |

| <b>0</b> |

| Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO47   | GPIO46   | GPIO45   | GPIO44   | GPIO43   | GPIO42   | GPIO41   | GPIO40   |

| <b>0</b> |

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO39   | GPIO38   | GPIO37   | GPIO36   | GPIO35   | GPIO34   | GPIO33   | GPIO32   |

| <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>0</b> | <b>1</b> | <b>0</b> |

Destaca-se que é a variação dos níveis lógicos dos pinos 12, 13 e 33 que determinam os pulsos enviados para as chaves dos conversores chaveados do RHT. Com base nisto, os registros responsáveis pela variação dos níveis lógicos dos pinos do DSP configurados como pinos de saída são o *GPASET* (*GPIO A Data Set Register*), *GPBSET* (*GPIO B Data Set Register*), *GPACLEAR* (*GPIO A Data Clear Register*) e *GPBCLEAR* (*GPIO B Data Clear Register*), sendo que:

- Setando-se os bits 12 e 13 do *GPASET* são estabelecidos níveis lógicos altos nos pinos de I/O 12 e 13 do DSP;

- Setando-se o bit 1 do *GPBSET* é estabelecido nível lógico alto no pino de I/O 33 do DSP;

- Setando-se os bits 12 e 13 do *GPACLEAR* são estabelecidos níveis lógicos baixos nos pinos de I/O 12 e 13 do DSP;

- Setando-se o bit 1 do *GPBCLEAR* é estabelecido nível lógico baixo no pino de I/O 33 do DSP.

#### 4.3.4 Configuração do Conversor Analógico-Digital (ADC)

Dando sequência à execução do código de controle, é chamada então a estrutura para configuração do *ADC* (*Analogic Digital Converter*). O *ADC* presente no DSP *TMS320F28335* possui dois blocos de conversão, A e B, que podem trabalhar tanto cascataados, permitindo a aquisição de 16 sinais, como trabalhar isoladamente, permitindo a aquisição de 8 sinais cada um.

Cada bloco de conversão possui dois sequenciadores responsáveis pela sequência com as quais as conversões são realizadas, sendo os sequenciadores do bloco de conversão A o SEQ1 e o SEQ2 e os sequenciadores do bloco de conversão B o SEQ3 e o SEQ4.

O registro *ADCMAXCONV* (*ADC Maximum Conversion Channels Register*) define o número de estágios de conversão dos sequenciadores, ou em outras palavras, este registro delimita a quantidade de aquisições realizadas pelo *ADC*.

Em concordância com a estratégia de controle detalhada no Capítulo 2, são realizadas cinco conversões, uma para o sinal da corrente de linha de entrada da fase A ( $i_{a(in)}$ ); uma para o sinal da tensão de entrada da fase A ( $v_{an}$ ); uma para o sinal da corrente de linha de entrada da fase B ( $i_{b(in)}$ ); uma para o sinal da corrente de linha de entrada da fase C ( $i_{c(in)}$ ); e outra para o sinal da corrente na carga ( $I_o$ ), o que torna necessário utilizar somente o bloco de conversão A do *ADC*. Uma vez que cada sequenciador do bloco de conversão A é responsável pela ordem de conversão de quatro sinais, logo foi habilitado que quatro conversões sejam sequenciadas pelo SEQ1 e uma conversão seja sequenciada pelo SEQ2. A descrição do registro *ADCMAXCONV* é apresentada na Tab. 4.7.

Tab. 4.7 – Configuração do *ADCMAXCONV* (*ADC Maximum Conversion Channels Register*).

| Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| Reserv. |

| 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Bit 7   | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         |

|---------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Reserv. | MAX_C<br>ONV2 | MAX_C<br>ONV2 | MAX_C<br>ONV2 | MAX_C<br>ONV1 | MAX_C<br>ONV1 | MAX_C<br>ONV1 | MAX_C<br>ONV1 |

| 0       | 0             | 0             | 0             | 0             | 0             | 1             | 1             |

Os bits 2-0 do *ADCMAXCONV* definem o número de conversões sequenciadas pelo SEQ1. O bit 3, quando setado, determina a operação em modo cascatedo dos dois sequenciadores. Os bits 6-4, por sua vez, definem o número de conversões sequenciadas pelo SEQ2.

Para a aplicação do controle do RHT, foi configurado nos bits 2-0 do *ADCMAXCONV* o valor 011b, o que determina que o SEQ1 sequenciará no máximo quatro conversões. Foi configurado ainda, nos bits 6-4 do *ADCMAXCONV* o valor 000b, o que define para o SEQ2 o sequenciamento de no máximo uma conversão. Como resultado, teve-se que o valor configurado no registro *ADCMAXCONV* foi igual 0003h.

Outro registro importante é o *ADCCHSELQSEQn* (*ADC Input Channel Select Sequencing Control Registers*), que demarca a ordem com as quais as conversões são realizadas. A representação de registro é demonstrada na Tab. 4.8.

Tab. 4.8 – Configuração do *ADCCHSELQSEQn* (*ADC Input Channel Select Sequencing Control Registers*).

|                     | Bits 15-12           | Bits 11-8            | Bits 7-4             | Bits 3-0          |

|---------------------|----------------------|----------------------|----------------------|-------------------|

| <b>ADCCHSELSEQ1</b> | CONV03               | CONV02               | CONV01               | CONV00            |

|                     | <b>3h (0011b)</b>    | <b>2h (0010b)</b>    | <b>1h (0001b)</b>    | <b>0h (0000b)</b> |

| <b>ADCCHSELSEQ2</b> | CONV07               | CONV06               | CONV05               | CONV04            |

|                     | <b>Não utilizado</b> | <b>Não utilizado</b> | <b>Não utilizado</b> | <b>4h (0100b)</b> |

Uma vez que cinco conversões são realizadas pelo bloco de conversão A do *ADC*, pela Tab. 4.8 tem-se que:

- Ao configurar os bits 3-0 do *ADCCHSELQSEQ1* com o valor 0h, define-se que a conversão do sinal proveniente da aquisição de  $i_{a(in)}$ , obtida pelo pino de entrada 0 do ADC, seja realizada em primeira instância;

- Ao configurar os bits 7-4 do *ADCCHSELQSEQ1* com o valor 1h, define-se que a conversão do sinal oriundo da aquisição de  $v_{an}$ , obtida pelo pino de entrada 1 do ADC, seja realizada na segunda posição;

- Ao configurar os bits 11-8 do *ADCCHSELQSEQ1* com o valor 2h, define-se que a conversão do sinal procedente da aquisição de  $i_{b(in)}$ , obtida pelo pino de entrada 2 do ADC, seja realizada na terceira posição;

- Ao configurar os bits 15-12 do *ADCCHSELQSEQ1* com o valor 3h, define-se que a conversão do sinal proveniente da aquisição de  $i_{c(in)}$ , obtida pelo pino de entrada 3 do ADC, seja realizada na quarta posição;

- Ao configurar os bits 3-0 do *ADCCHSELQSEQ2* com o valor 4h, define-se que a conversão do sinal procedente da aquisição de  $I_o$ , obtida pelo pino de entrada 4 do ADC, seja realizada na quinta posição.

### 4.3.5 Configuração dos Registros ePWM

O principal registro ePWM a ser configurado é o *TBPRD* (*Time-Base Period*), cujo valor representa o tempo gasto para a completa amostragem dos sinais sensoriados coletados pelo *ADC*. Com base numa frequência de *clock* utilizada nos processos realizados pelo DSP (*HSPCLK*) definida em 75 MHz, e adotando-se uma frequência de

amostragem de 100 kHz, tem-se que o valor a ser configurado no registro *TBPRD* é calculado através da Eq. (4.4).

$$\begin{aligned} TBPRD &= \frac{HSPCLK}{f_a} \\ TBPRD &= \frac{75 \cdot 10^6}{100 \cdot 10^3} = 750 \end{aligned} \quad (4.4)$$

Portanto, o valor digital 750 configurado no registro *TBPRD* representa o tempo de contagem de zero até o valor do período de amostragem, que para uma frequência de 100 kHz, é de 10  $\mu$ s. Finalizada a contagem deste tempo, o ADC inicia as conversões dos sinais sensoriados.

### 4.3.6 Chamada da Rotina de Interrupção

Durante a execução do algoritmo de controle, uma vez configurados os principais registros do DSP, o programa entra em um laço de repetição infinito, permanecendo nele até que as conversões realizadas pelo *ADC* estejam completamente concluídas. Uma vez finalizadas as amostras, é chamada a rotina de interrupção do ADC.

Quando a interrupção do ADC é acionada, logo na primeira linha de código é verificado se o valor de *cont* é menor ou igual a *BUFSIZE*. Caso essa verificação seja verdadeira, todos os principais cálculos, comparações e linhas de comando são executados de forma a estabelecer o controle do retificador híbrido trifásico. Sendo a verificação falsa, como medida de segurança, a variável *cont* é zerada e os bits *GPIO12* e *GPIO13* do registro *GPACLEAR* e o bit *GPIO33* do registro *GPBCLEAR* são setados (envia nível baixo de pulso para os interruptores dos conversores chaveados), pois, conforme é detalhado na subseção 4.3.6.3, é entendido que ocorreu algum erro na verificação da passagem por zero do sinal resultante da aquisição da tensão de entrada da fase A (variável *VinA*), e consequentemente o controle do RHT encontra-se comprometido.

#### 4.3.6.1 Armazenamento das Amostras em Variáveis

Uma vez confirmado que o valor de *cont* é menor ou igual ao valor de *BUFSIZE*, a rotina de interrupção inicia o armazenamento das amostras geradas em variáveis. As conversões realizadas são armazenadas nos registros de armazenamento *ADCRESULTn* (*ADC Conversion Result Buffer Registers*). Conforme descrito na subseção 4.3.4 são realizadas cinco conversões pelo ADC, onde os valores digitais provenientes das

aquisições de  $i_{a(in)}$ ,  $v_{an}$ ,  $i_{b(in)}$ ,  $i_{c(in)}$  e  $I_o$  são armazenados nos registros  $ADCRESULT0$ ,  $ADCRESULT1$ ,  $ADCRESULT2$ ,  $ADCRESULT3$  e  $ADCRESULT4$  respectivamente, conforme definido pela sequência de conversões estabelecida pelos sequenciadores do bloco de conversão A do  $ADC$ .

Com base nisto, foram criados cinco variáveis de controle, conforme declarado na Tab. 4.1: o  $IinA$ , que é a variável onde são armazenados os valores provenientes do  $ADCRESULT0$ , de modo que é a partir dos valores armazenados nesta variável que são feitas as comparações com a referência para as devidas variações da largura dos pulsos enviados à chave do conversor SEPIC da fase A; o  $VinA$ , que é a variável onde são armazenados os valores resultantes do  $ADCRESULT1$ , de forma que é a partir dos valores armazenados nesta variável que é feita a verificação da passagem por zero, para fins de sincronismo entre a tensão de entrada da Fase A e a referência senoidal  $Isen$ ; o  $IinB$ , que é a variável onde são armazenados os valores oriundos do  $ADCRESULT2$ , onde é a partir dos valores armazenados nesta variável que são feitas as comparações com a referência para as devidas variações da largura dos pulsos enviados à chave do conversor SEPIC da fase B; o  $IinC$ , que é a variável onde são armazenados os valores provenientes do  $ADCRESULT3$ , de forma que é a partir dos valores armazenados nesta variável que são feitas as comparações com a referência para as devidas variações da largura dos pulsos enviados à chave do conversor SEPIC da fase C; e o  $Io$ , que é a variável onde são armazenados os valores oriundos do  $ADCRESULT4$ , de modo que é a partir dos valores armazenados nesta variável que o ganho realimentado da referência é determinado, uma vez que a referência deve acompanhar as variações de carga.

#### 4.3.6.2 Retificação de $IinA$ , $IinB$ e $IinC$

Nesta etapa da rotina de interrupção, os valores armazenados nas variáveis  $IinA$ ,  $IinB$  e  $IinC$  são retificados para comparação com a referência senoidal retificada.

#### 4.3.6.3 Módulo de Sincronismo

A parte de sincronismo entre a referência senoidal retificada criada digitalmente e o sinal proveniente da aquisição da tensão  $v_{an}$  ocorre verificando-se, para cada período de amostragem, se a multiplicação entre os valores armazenados na variável  $VinA$  e os valores armazenados em  $VinA\_pass$  é menor que zero, conforme ilustrado no fluxograma da Fig. 4.1 (c). Uma vez que, se a amostra armazenada em  $VinA$  for representada por um valor encontrado no semicírculo negativo de  $v_{an}$  e a amostra armazenada em  $VinA\_pass$  for representada por um valor encontrado no semicírculo

positivo, ou vice-versa, a multiplicação destes valores é negativa, confirmando que houve a passagem por zero. O valor proveniente desta multiplicação é armazenado na variável *Produto*. Toda vez que o valor de *Produto* for menor que zero, a variável de contagem *cont* é zerada, garantindo que o início de armazenamento de amostras ocorra sempre que houver a passagem por zero, e consequentemente, que a referência senoidal *Isen* esteja sempre em fase com as aquisições da tensão  $v_{an}$ .

Como o valor de *cont* é sempre zerado quando da ocorrência da passagem por zero, a sequência de geração de amostras é sempre reiniciada a cada semiciclo de onda na frequência da rede, o que determina que a variável *cont* nunca seja incrementada até atingir o valor de *BUFSIZE*, a não ser que ocorra algum erro na execução do módulo de sincronismo. Daí a necessidade de se garantir que a variável *cont* seja também zerada caso seu valor de contagem atinja o valor de *BUFSIZE*.

#### 4.3.6.4 Geração das Referências Senoidais *IRefA*, *IRefB* e *IRefC*

Como o vetor *Isen* está sempre em sincronismo com as aquisições da tensão  $v_{an}$ , garante-se que, para cada chamada da rotina de interrupção, o valor da referência senoidal da fase A (*IRefA*) receba o valor armazenado na posição *cont* do vetor *Isen* multiplicado pelo valor da constante *k* e pelo valor médio das *cont* amostras resultantes das aquisições da corrente de carga *Io*.

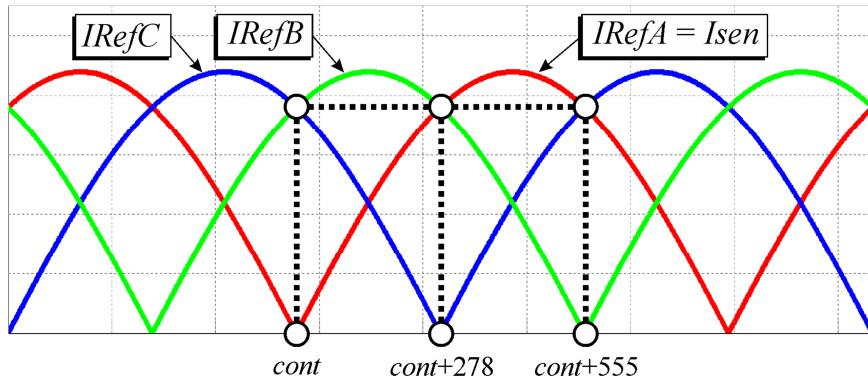

Determinada a referência senoidal *IRefA*, é necessário então gerar as referências senoidais das fases B (*IRefB*) e C (*IRefC*). Como o vetor *Isen* é composto por *BUFSIZE* valores que compõem o ciclo completo de uma onda senoidal na frequência de 60 Hz, um semiciclo desta mesma onda é completamente armazenado em 833 posições. Uma vez que o valor de *Isen* na posição 833 corresponde ao valor de seno de 180°, os valores do seno de 120° e de 240° são encontrados nas posições 555 e 278, respectivamente, do vetor *Isen*, conforme demonstrado por (4.5) e (4.6).

$$P_{120^\circ} = \frac{P_{180^\circ} \cdot 120^\circ}{180^\circ} \quad (4.5)$$

$$P_{120^\circ} = \frac{833 \cdot 120^\circ}{180^\circ} = 555$$

$$P_{240^\circ} = P_{180^\circ} - P_{120^\circ} \quad (4.6)$$

$$P_{240^\circ} = 833 - 555 = 278$$

Onde  $P_{180^\circ}$  é o número de posições do vetor  $I_{sen}$  equivalente a um defasamento de  $180^\circ$ ,  $P_{120^\circ}$  é o número de posições do vetor  $I_{sen}$  equivalente a um defasamento de  $120^\circ$  e  $P_{240^\circ}$  é o número de posições do vetor  $I_{sen}$  equivalente a um defasamento de  $240^\circ$ .

Portanto, quando o valor da variável  $IRefA$  for igual ao valor encontrado na posição  $cont$  do vetor  $I_{sen}$  multiplicado por  $k$  e  $Io\_med$ , os valores de  $IRefB$  e  $IRefC$  serão iguais aos valores encontrados nas posições  $cont+278$  e  $cont+555$ , respectivamente, conforme indicado na Fig. 4.2.

Fig. 4.2 – Geração das referências senoidais defasadas de  $120^\circ$ .

Como pode ser observado, ao invés de se gerar um vetor de referência senoidal para cada fase do RHT, o que resultaria no estouro da memória interna do DSP e na realização da aquisição dos sinais das tensões de entrada das fases B e C para fins de sincronismo, optou-se por gerar apenas um vetor de referência senoidal e estabelecer que os pulsos enviados para os interruptores dos conversores SEPIC sejam defasados de  $120^\circ$ , eliminando-se com isto a necessidade da utilização de mais dois sensores de tensão.

#### 4.3.6.5 Módulo de Geração de Pulses

A variação dos pulsos enviados para os interruptores dos conversores SEPIC ocorre mediante variação do nível lógico das saídas 12, 13 e 33 do DSP, que por sua vez, depende da comparação entre as amostras das correntes de linha de entrada e suas respectivas referências senoidais.

Sendo assim, conforme ilustrado na Fig. 4.1 (d), seguindo o princípio do controle por histerese, o módulo de geração de pulsos estabelece que:

- Quando o valor retificado de  $IinA$  for menor que  $IRefA$ , o bit  $GPIO12$  do registro  $GPASET$  é setado, garantindo nível alto na saída 12 do DSP. Quando o

valor retificado de  $InA$  for maior ou igual a  $IRefA$ , o bit  $GPIO12$  do registro  $GPACLEAR$  é setado, garantindo nível lógico baixo na saída 12 do DSP.

- Se o valor retificado de  $InB$  for menor que  $IRefB$ , o bit  $GPIO13$  do registro  $GPASET$  é setado, garantindo nível alto na saída 13 do DSP. Se o valor retificado de  $InB$  for maior ou igual a  $IRefB$ , o bit  $GPIO13$  do registro  $GPACLEAR$  é setado, garantindo nível lógico baixo na saída 12 do DSP.

- Caso o valor retificado de  $InC$  for menor que  $IRefC$ , o bit  $GPIO33$  do registro  $GPBSET$  é setado, garantindo nível alto na saída 33 do DSP. Caso o valor retificado de  $InC$  for maior ou igual a  $IRefC$ , o bit  $GPIO33$  do registro  $GPBCLEAR$  é setado, garantindo nível lógico baixo na saída 33 do DSP.

#### 4.3.6.6 Incremento de *cont* e Cálculo do Valor Médio de *Io*

Ao final de cada rotina de interrupção o valor da variável *cont* é incrementado e utilizado no cálculo do valor médio das amostras provenientes das aquisições da corrente de carga ( $Io\_med$ ). Conforme descrito na Tab. 4.1, o valor de  $Io\_med$ , ao ser multiplicado ao vetor  $Isen$ , determina que a amplitude das referências senoidais varie conforme as alterações de carga. O valor médio da variável *Io* é calculado a cada rotina de interrupção através da Eq. 4.7.

$$Io\_med = \frac{\sum_{cont=1}^{BUFSIZE} Io_{(cont)}}{cont} \quad (4.7)$$

O cálculo do valor de  $Io\_med$  é reiniciado toda vez que ocorrer a passagem por zero da tensão da fase A, uma vez que o contador *cont* é zerado, conforme foi mencionado na subseção 4.3.6.3.

Concluída a rotina de interrupção, a execução do código de controle retorna para o laço de repetição infinito e ali permanece até que novas conversões realizadas pelo ADC sejam finalizadas e uma nova rotina de interrupção seja solicitada.

## 4.4 Considerações Finais

Neste capítulo foi demonstrada, de forma detalhada, a implementação da estratégia de controle apresentada no Capítulo 2 destacando o algoritmo embarcado no DSP.

Foi possível concluir que a correta configuração de todos os registros do DSP é de primordial importância para o perfeito funcionamento do controle do RHT, principalmente no que diz respeito aos registros responsáveis pelos pinos de propósito geral, pinos estes utilizados para o envio dos pulsos para os interruptores dos conversores SEPIC, e aos registros responsáveis pelo funcionamento do ADC, uma vez que o controle do RHT depende diretamente do correto sensoriamento dos sinais de corrente e de tensão.

Observa-se que o desenvolvimento do controle para imposição das correntes de linha de entrada baseado na técnica por histerese é relativamente simples e fácil de ser implementado digitalmente.

# Capítulo 5

## Análise Experimental

### 5.1 Considerações Iniciais

Neste capítulo é apresentado o protótipo de laboratório desenvolvido para uma potência de saída de 5 kW bem como a disposição de seus componentes, visando facilitar a aquisição de todas as formas de onda necessárias para a validação da estratégia de controle desenvolvida para o RHT.

São apresentados, entre outros resultados experimentais, as formas de onda das correntes de linha de entrada e as correntes drenadas por Ret-1 e Ret-2; o comportamento do RHT mediante um degrau de carga; e comparações entre o nível de DHT das correntes de linha de entrada e a norma IEC 61000-3-2.

### 5.2 Protótipo Experimental de 5 kW

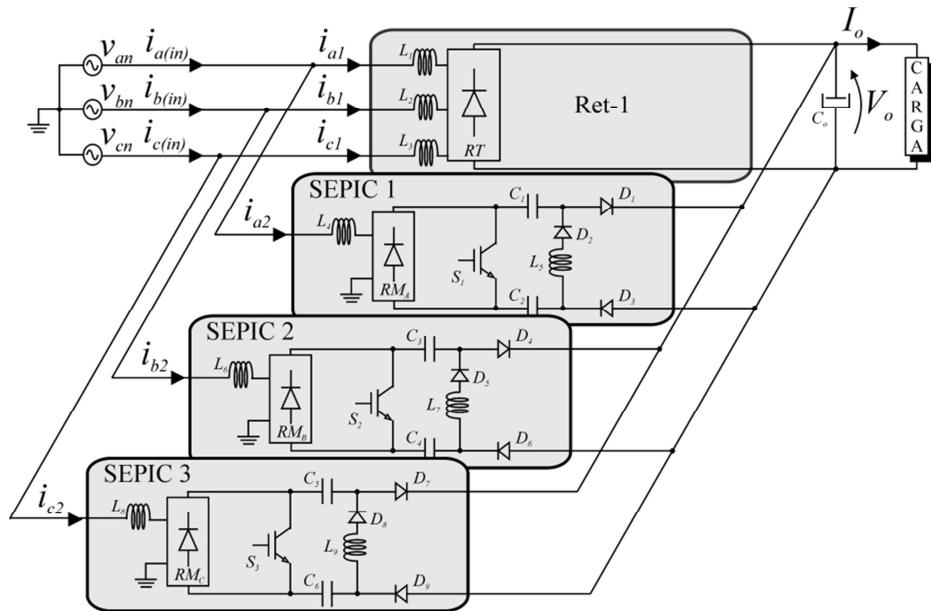

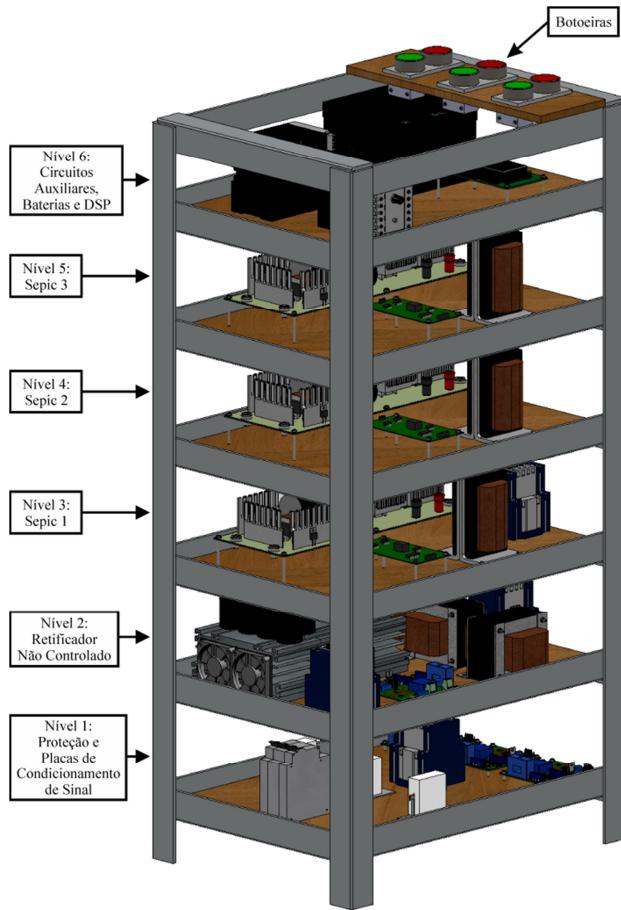

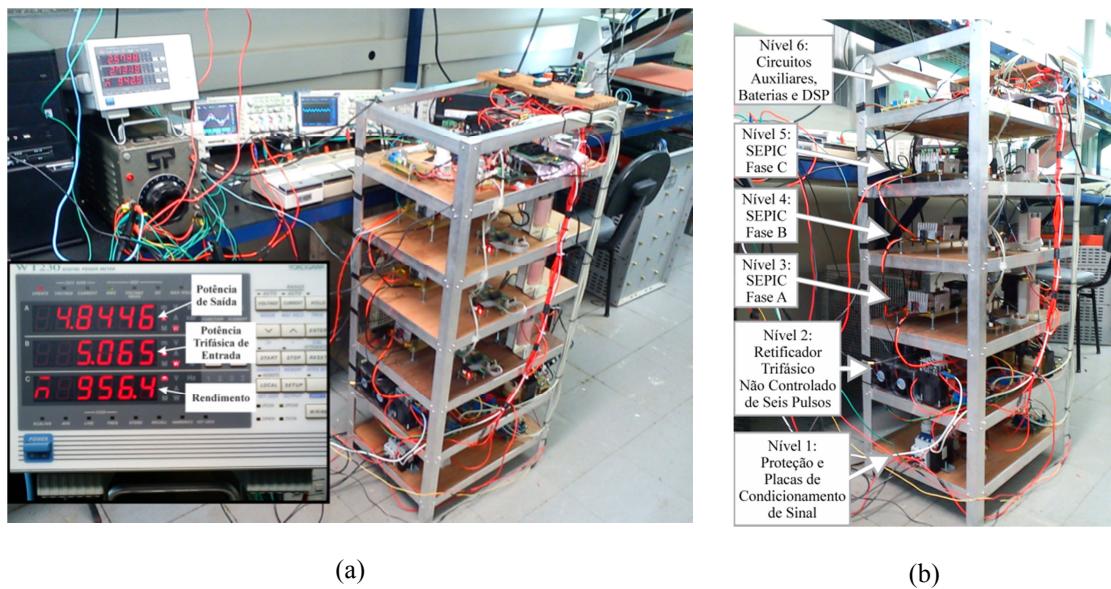

Com base no arranjo topológico apresentado na Fig. 5.1, utilizou-se o *software SolidWorks®* para realizar a previsão das disposição dos componentes do arranjo experimental do RHT a ser implementado em laboratório, conforme ilustrado na Fig. 5.2.

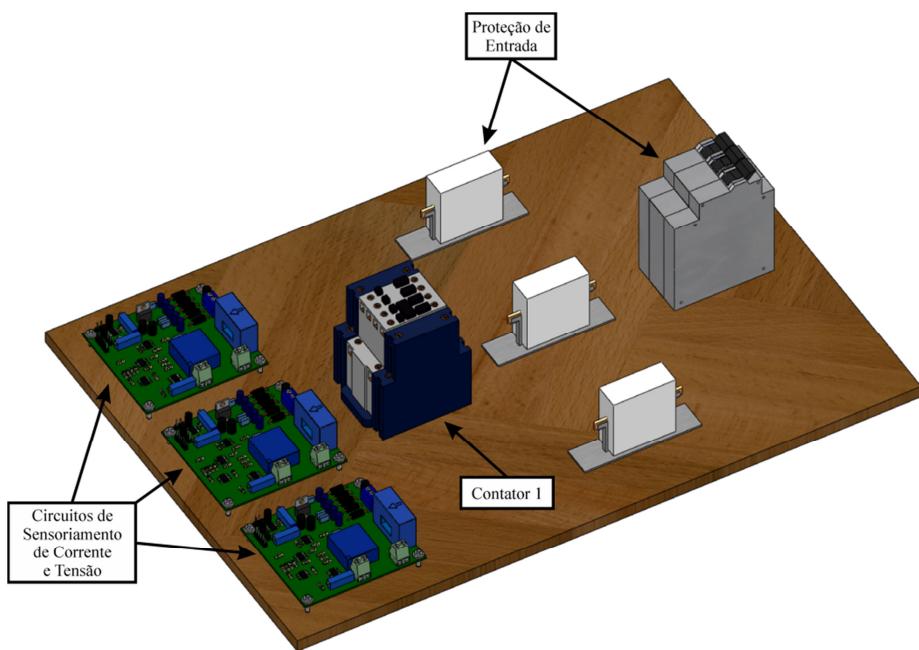

Foi previsto a construção do protótipo em seis níveis, de forma a ser inserido em um *rack* com dimensões de 50 cm de comprimento, 35 cm de largura e 95 cm de altura. O primeiro nível é composto pelos dispositivos de proteção (disjuntor tripolar e fusíveis) e as placas para o condicionamento dos sinais das correntes de linha de entrada e do sinal da tensão de entrada da fase A. O segundo nível consta o retificador trifásico não controlado de seis pulsos (Ret-1) e a placa para o condicionamento do sinal da corrente de carga. Nos terceiro, quarto e quinto níveis estão os conversores SEPIC das fases A, B e C respectivamente. O último nível apresenta as baterias para alimentação das bobinas dos contatores, o DSP e seus circuitos auxiliares.

Fig. 5.1 – Arranjo topológico do circuito de potência do RHT.

Fig. 5.2 – Planejamento do protótipo do retificador híbrido trifásico implementado em laboratório.

A Fig. 5.3 ilustra o primeiro nível da estrutura. O disjuntor tripolar é utilizado para a proteção geral do circuito do RHT contra curto-circuitos e os fusíveis são utilizados para proteção de cada uma das fases.

O contator geral de alimentação (*Contator 1*) é utilizado em conjunto com o *Contator 2*, presente no segundo nível, para a realização da pré-carga dos capacitores de saída. O carregamento inicial destes capacitores é necessário para a proteção da ponte retificadora trifásica presente em Ret-1 contra picos de corrente. Uma vez acionado o *Contator 1*, inicia-se a pré-carga dos capacitores de saída através de uma resistência ligada à cada fase do RHT. Quando é finalizada a pré-carga, estas resistências são curto-circuitadas pelo *Contator 2*.

A partir do *Contator 1*, os cabos de alimentação passam pelas placas de condicionamento de sinal, utilizados para envio dos sinais das correntes de linha de entrada e da tensão de entrada da Fase A para o conversor Analógico-Digital do DSP.

Fig. 5.3 – 1º Nível: Alimentação trifásica, proteção e sensoriamentos de tensão e corrente.

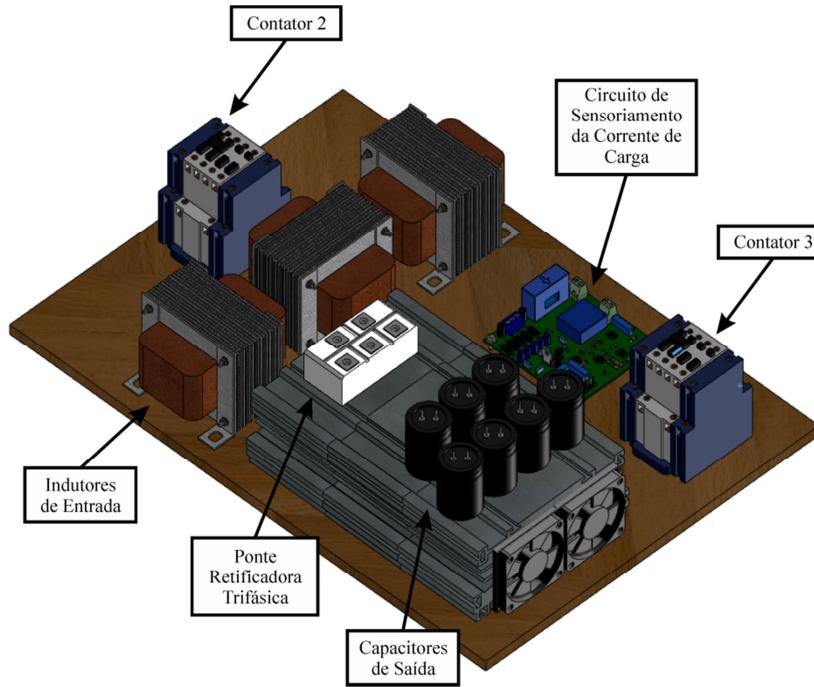

Pela Fig. 5.4 visualiza-se o segundo nível do retificador híbrido trifásico, composto pelo circuito do retificador trifásico não controlado de seis pulsos. É possível observar a disposição dos indutores de entrada, da ponte retificadora, do dissipador, do *Contator 2* utilizado na pré-carga dos capacitores de saída e da placa para sensoriamento da corrente de carga.

No segundo nível há a presença também de um contator (*Contator 3*) utilizado para conectar a carga ao barramento CC fornecido pelo RHT somente após a pré-carga dos capacitores de saída ser completamente realizada.

Fig. 5.4 – 2º Nível: Retificador trifásico não controlado de seis pulsos.

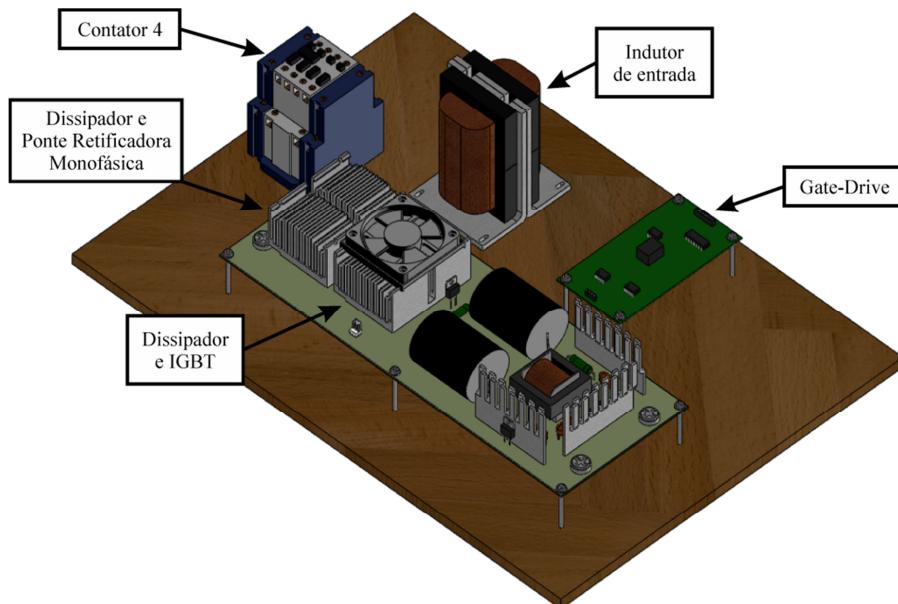

Nos terceiro, quarto e quinto níveis encontram-se instalados os conversores chaveados SEPIC que compõem a estrutura retificadora Ret-2. A Fig. 5.5 ilustra a estrutura do conversor SEPIC, onde é possível visualizar a disposição da ponte retificadora monofásica, da chave IGBT, dos diodos, dos dissipadores, dos indutores e dos capacitores. No quarto nível está presente um contator (*Contator 4*) utilizado para o isolamento dos conversores SEPIC em caso de testes somente no estágio do Ret-1.

Fig. 5.5 – 3º, 4º e 5º Níveis: Conversor SEPIC e Gate-Driver para acionamento da chave-IGBT.

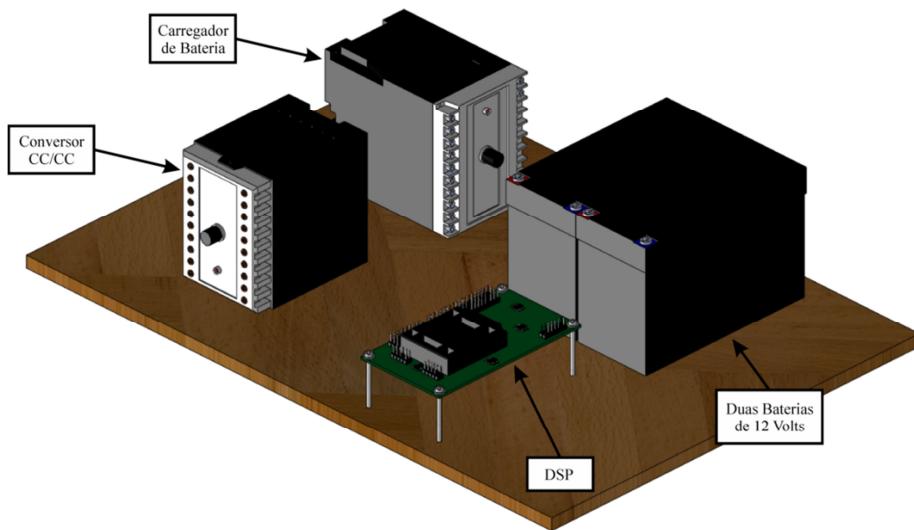

No sexto nível, ilustrado na Fig. 5.6, observa-se a presença do DSP, duas baterias de 12 V ligadas em série, um carregador de baterias e um conversor CC/CC. O conversor CC/CC é utilizado para converter os 24 V provenientes das duas baterias em  $\pm 15$  V e  $\pm 5$  V para alimentação dos circuitos de sensoriamento, dos *gate-drivers* e do DSP. As baterias são utilizadas também para a alimentação das bobinas dos contatores.

Fig. 5.6 – 6º Nível: DSP, conversor CC/CC e carregador de baterias para alimentação de duas baterias de 12 V.

Baseado nos parâmetros determinados pelo equacionamento apresentado no Capítulo 2 e pela solução do modelo matemático mostrada no Capítulo 3, as Tab. 5.1 a 5.9 trazem as características dos indutores, capacitores, diodos e chaves que compõem o circuito de potência do retificador híbrido trifásico.

Tab. 5.1 – Indutores  $L_1$ ,  $L_2$  e  $L_3$ .

|  |                                  |                      |

|--|----------------------------------|----------------------|

|  | Indutância                       | 1 mH                 |

|  | Corrente de Pico Máxima          | 14,7 A               |

|  | Corrente Eficaz Máxima           | 12,57 A              |

|  | Número de Espiras                | 64                   |

|  | Bitola do Fio                    | AWG 13               |

|  | Número de Condutores em Paralelo | 2                    |

|  | Núcleo                           | Chapa de Aço Silício |

Tab. 5.2 – Ponte retificadora trifásica: SKD 62/12 da SEMIKRON®.

|  |                               |        |

|--|-------------------------------|--------|

|  | Corrente Máxima a 85° C       | 86 A   |

|  | Corrente de Pico              | 500 A  |

|  | Máxima Tensão de Pico Reverso | 1200 V |

|  | Máxima Queda de Tensão Direta | 1.8 V  |

Tab. 5.3 – Capacitor de saída  $C_o$ .

|  |                                       |                    |

|--|---------------------------------------|--------------------|

|  | Quantidade de Capacitores em Paralelo | 7                  |

|  | Capacitância Unitária                 | 470 $\mu\text{F}$  |

|  | Capacitância Total                    | 3290 $\mu\text{F}$ |

|  | Tensão de Pico Máxima                 | 400 V              |

|  | Tensão Média Máxima                   | 500 V              |

Tab. 5.4 – Indutores  $L_4$ ,  $L_6$  e  $L_8$ .

|  |                                  |                     |

|--|----------------------------------|---------------------|

|  | Indutância                       | 1 mH                |

|  | Corrente de Pico Máxima          | 13,25 A             |

|  | Corrente Eficaz Máxima           | 8,82 A              |

|  | Número de Espiras                | 56                  |

|  | Bitola do Fio                    | AWG 14              |

|  | Número de Condutores em Paralelo | 2                   |

|  | Núcleo                           | Ferrite EE-65/33/36 |

Tab. 5.5 – Ponte retificadora monofásica: *TB358* da *TAITRON*<sup>®</sup>.

|  |                               |        |

|--|-------------------------------|--------|

|  | Máxima Tensão de Pico Reverso | 800 V  |

|  | Máxima Tensão RMS             | 560 V  |

|  | Máxima Corrente Média a 50°C  | 35 A   |

|  | Pico de Corrente              | 400 A  |

|  | Capacitância da Junção        | 300 pF |

Tab. 5.6 – Chaves  $S_1$ ,  $S_2$  e  $S_3$ : IGBT *SK60GAR125* da *SEMITOP*<sup>®</sup> 2.

|  |                                          |        |

|--|------------------------------------------|--------|

|  | Tensão entre Coletor e Emissor           | 1200 V |

|  | Corrente do Coletor a 25 °C              | 51 A   |

|  | Corrente do Coletor a 80 °C              | 35 A   |

|  | Pico de Corrente no Coletor              | 100 A  |

|  | Tensão entre <i>Gate</i> e <i>Source</i> | ±20V   |

Tab. 5.7 – Capacitores  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ,  $C_5$ ,  $C_6$ ,  $C_7$ ,  $C_8$  e  $C_9$ .

|  |                         |       |

|--|-------------------------|-------|

|  | Capacitância            | 22 μF |

|  | Tensão de Pico Máxima   | 800 V |

|  | Tensão Média Máxima     | 500 V |

|  | Corrente Máxima         | 30 A  |

|  | Corrente de Pico Máxima | 100 A |

Tab. 5.8 – Indutores  $L_5$ ,  $L_7$  e  $L_9$ .

|  |                                  |                     |

|--|----------------------------------|---------------------|

|  | Indutância                       | 500 μH              |

|  | Corrente de Pico Máxima          | 20,5 A              |

|  | Corrente Eficaz Máxima           | 5,2 A               |

|  | Número de Espiras                | 96                  |

|  | Bitola do Fio                    | AWG 17              |

|  | Número de Condutores em Paralelo | 2                   |

|  | Núcleo                           | Ferrite EE-55/28/21 |

Tab. 5.9 – Diodos  $D_1, D_2, D_3, D_4, D_5, D_6, D_7, D_8$  e  $D_9$ : APT15D100K da ADVANCED POWER TECHNOLOGY®.

|  |                               |        |

|--|-------------------------------|--------|

|  | Máxima Tensão Reversa         | 1000 V |

|  | Máxima Queda de Tensão Direta | 2.3 V  |

|  | Máxima Corrente Média         | 15 A   |

|  | Máxima Corrente RMS           | 31 A   |

|  | Capacitância da Junção        | 17 pF  |

As Tab. 5.10 e 5.11 trazem as características do *gate-driver* utilizado para o chaveamento dos interruptores dos conversores SEPIC e do DSP utilizado no controle digital do RHT, respectivamente.

Tab. 5.10 – Gate-Driver SKHI 10/12 da SEMIKRON®.

|  |                                                                                    |        |

|--|------------------------------------------------------------------------------------|--------|

|  | Mínima tensão de alimentação                                                       | 14.4 V |

|  | Máxima tensão de alimentação                                                       | 15.6 V |

|  | Máxima corrente de alimentação                                                     | 0.3 A  |

|  | Tensão de <i>gate</i> fornecida para acionamento da chave                          | + 15 V |

|  | Tensão de <i>gate</i> fornecida para desligamento da chave                         | - 8 V  |

|  | Resistência de entrada                                                             | 10 kΩ  |

|  | Tensão de referência para monitoramento da tensão entre coletor e emissor da chave | 5.2 V  |

Tab. 5.11 – DSP TMS320F28335® da TEXAS INSTRUMENTS®.

|  |                                                                        |

|--|------------------------------------------------------------------------|

|  | Arquitetura de ponto flutuante de 32 bits                              |

|  | Conversor analógico/digital (A/D) ultra-rápido, na faixa de 80 ns      |

|  | 512 KB de memória flash                                                |

|  | 68 KB de memória RAM                                                   |

|  | Frequência de <i>clock</i> de 150 MHz                                  |

|  | 176 pinos conectores para possível comunicação com outros dispositivos |

A Tab. 5.12 demonstra as características do módulo de aquisição e condicionamento de sinais de corrente e de tensão. O Módulo tem por função a leitura e

tratamento de sinais de tensão e corrente para que estes possam ser interpretados pelo DSP.

Tab. 5.12 – Módulo para aquisição e condicionamento de sinais de corrente e de tensão.

|                                                                                   |                                                 |                 |

|-----------------------------------------------------------------------------------|-------------------------------------------------|-----------------|

|  | Máxima alimentação +15 (relação ao <i>gnd</i> ) | 14.8 V          |

|                                                                                   | Máxima alimentação -15 (relação ao <i>gnd</i> ) | -14.8 V         |

|                                                                                   | Mínima alimentação +15 (relação ao <i>gnd</i> ) | 15.2 V          |

|                                                                                   | Mínima alimentação -15 (relação ao <i>gnd</i> ) | -15.2 V         |

|                                                                                   | Máxima corrente eficaz nominal de medição       | 50 A            |

|                                                                                   | Faixa de medição de corrente                    | -70 A a +70 A   |

|                                                                                   | Máxima tensão eficaz nominal de medição         | 500 V           |

|                                                                                   | Faixa de medição de tensão                      | -500 V a +500 V |

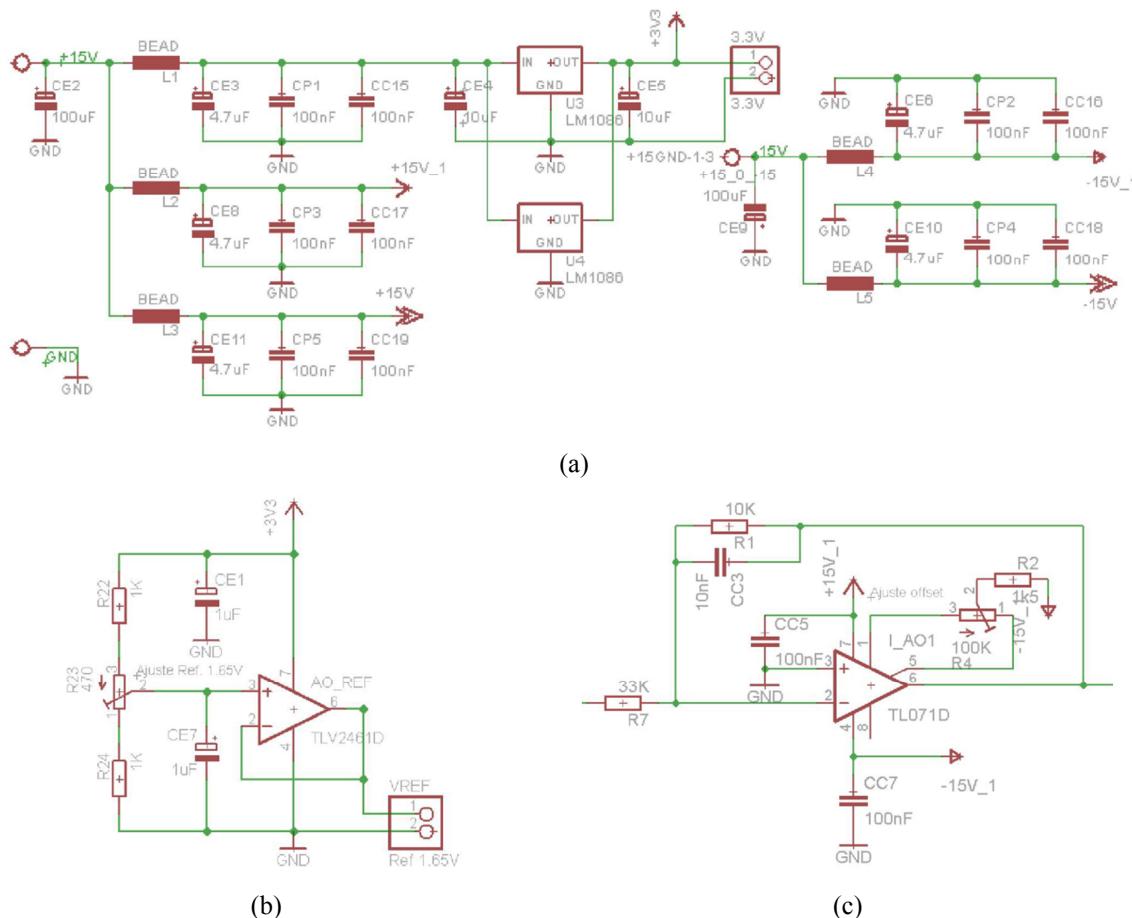

O módulo de aquisição e condicionamento de sinais de corrente e de tensão pode ter seu circuito dividido em três estágios, conforme visualizado pela Fig. 5.7.

Fig. 5.7 – Módulo de aquisição e condicionamento de sinais de corrente e de tensão: (a) primeiro, (b) segundo e (c) terceiro estágios.

O primeiro estágio, visualizado na Fig. 5.7 (a) é um estágio de filtro e regulação da alimentação, sendo este composto por capacitores, *beads*, um regulador de tensão e um amplificador operacional usado como *buffer* para dar o nível CC considerado como zero pelo DSP. Já neste estágio há uma separação entre as alimentações dos amplificadores operacionais do estágio de filtro de tensão com o de corrente, assim havendo um desacoplamento para evitar interferência entre sinais. Ainda como uma parte anexa a este estágio, há um divisor de tensão, responsável por dar um nível de tensão que posteriormente será somado ao sinal para criar um *offset* e elevar o sinal ao “zero” do DSP.

O segundo estágio, demonstrado na Fig. 5.7 (b), é efetivamente responsável pelo tratamento inicial do sinal, sendo que existem dois estágios idênticos, um para o sinal de tensão outro para o de corrente, sendo este circuito um filtro *anti-aliasing* responsável por limitar a frequência de sinal amostrado, devendo este ter seus valores redimensionados de acordo com a frequência do sinal de interesse.

O terceiro estágio do circuito é por final um circuito somador que soma o sinal vindo do estágio anterior a um nível CC de aproximadamente 1,5V (sendo 1,5V para o TMS320F28335) de forma que o sinal agora possui o nível zero neste valor, forma usada pelo DSP para aquisição do sinal.

Uma vez previsto a melhor disposição dos componentes do RHT, um protótipo para uma potência de saída de 5 kW foi construído em laboratório, conforme demonstrado pela Fig. 5.8. O resumo dos parâmetros do protótipo construído é apresentado na Tab. 5.13.

Tab. 5.13 – Resumo dos parâmetros do protótipo do retificador híbrido trifásico implementado.

| Componentes                     | Ret-1                          | Ret-2                                                         |

|---------------------------------|--------------------------------|---------------------------------------------------------------|

| Ponte Retificadora              | RT: SKD 62/12                  | $RM_A, RM_B$ e $RM_C$ : TB358                                 |

| Indutor                         | $L_1, L_2$ e $L_3 = 1$ mH      | $L_4, L_6$ e $L_8 = 1$ mH<br>$L_5, L_7$ e $L_9 = 500$ $\mu$ H |

| Capacitor                       | $C_o = 3290\mu F$              | $C_1, C_2, C_3, C_4, C_5$ e $C_6 = 22\mu F$                   |

| Chave                           | -                              | $S_1, S_2$ e $S_3$ : IGBT SK60GAR125                          |

| Diodo                           | -                              | $D_{1...9}$ : APT15D100K                                      |

| Potência Ativa Média Processada | $P_{Ret-1(med)} = 3$ kW (60 %) | $P_{Ret-2(med)} = 2$ kW (40 %)                                |

Fig. 5.8 – (a) Protótipo do retificador híbrido trifásico desenvolvido em laboratório e equipamentos de medição; e (b) apresentação dos níveis do protótipo.

## 5.2 Resultados Experimentais

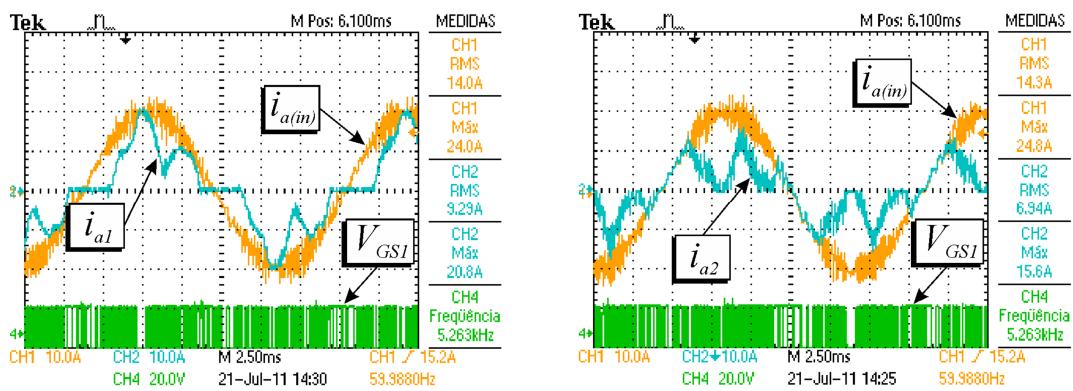

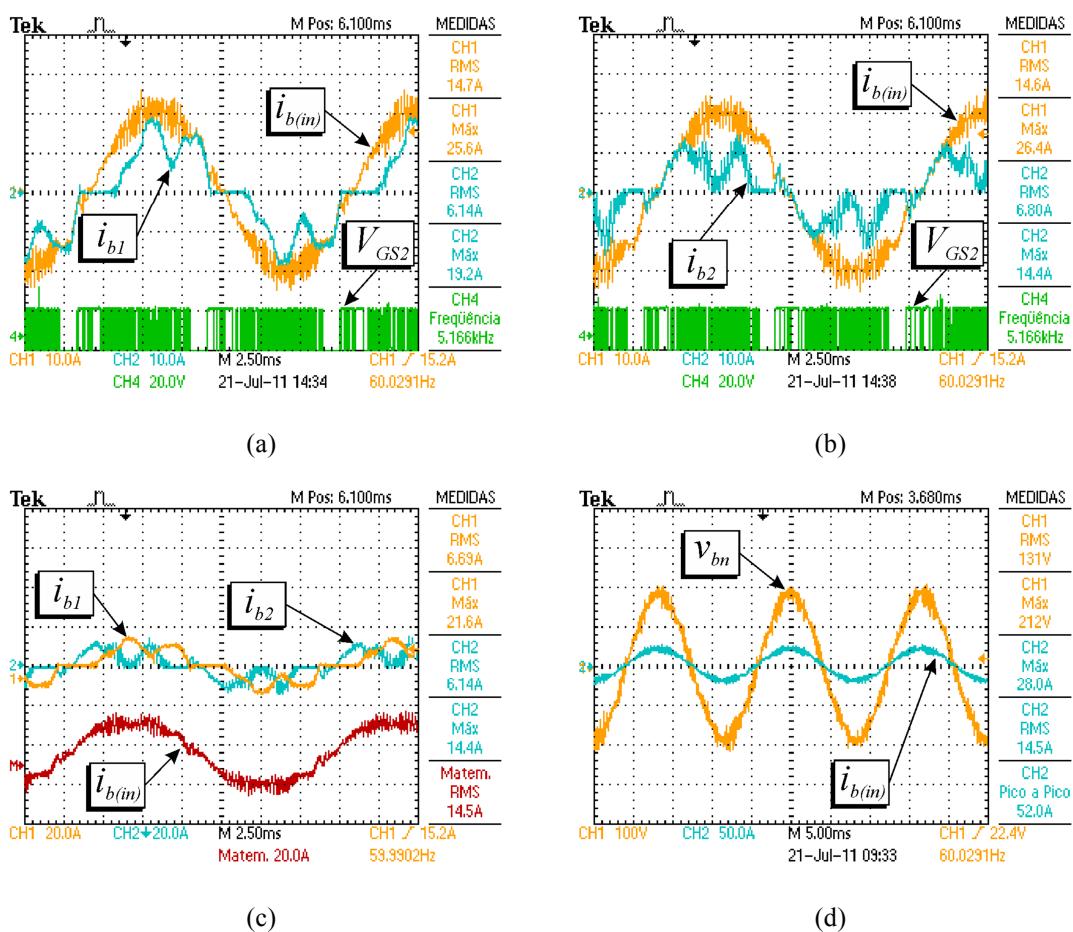

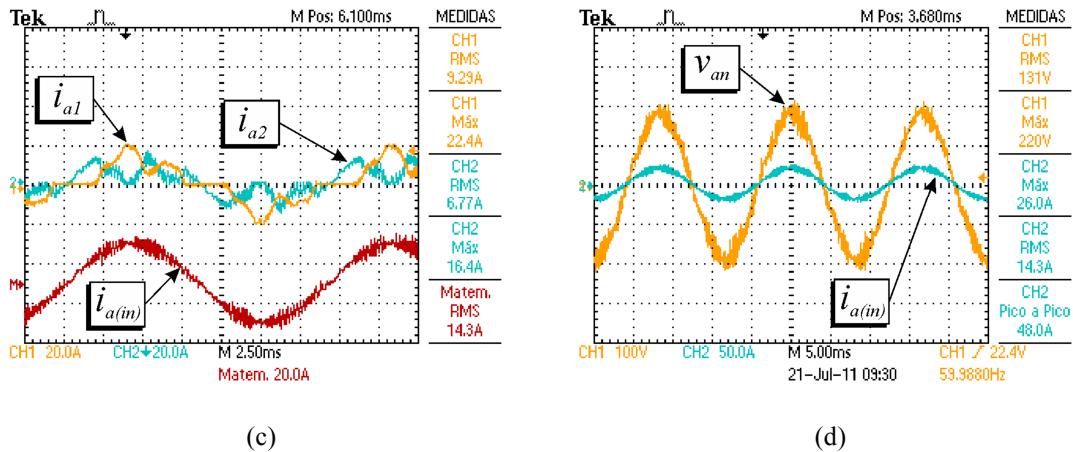

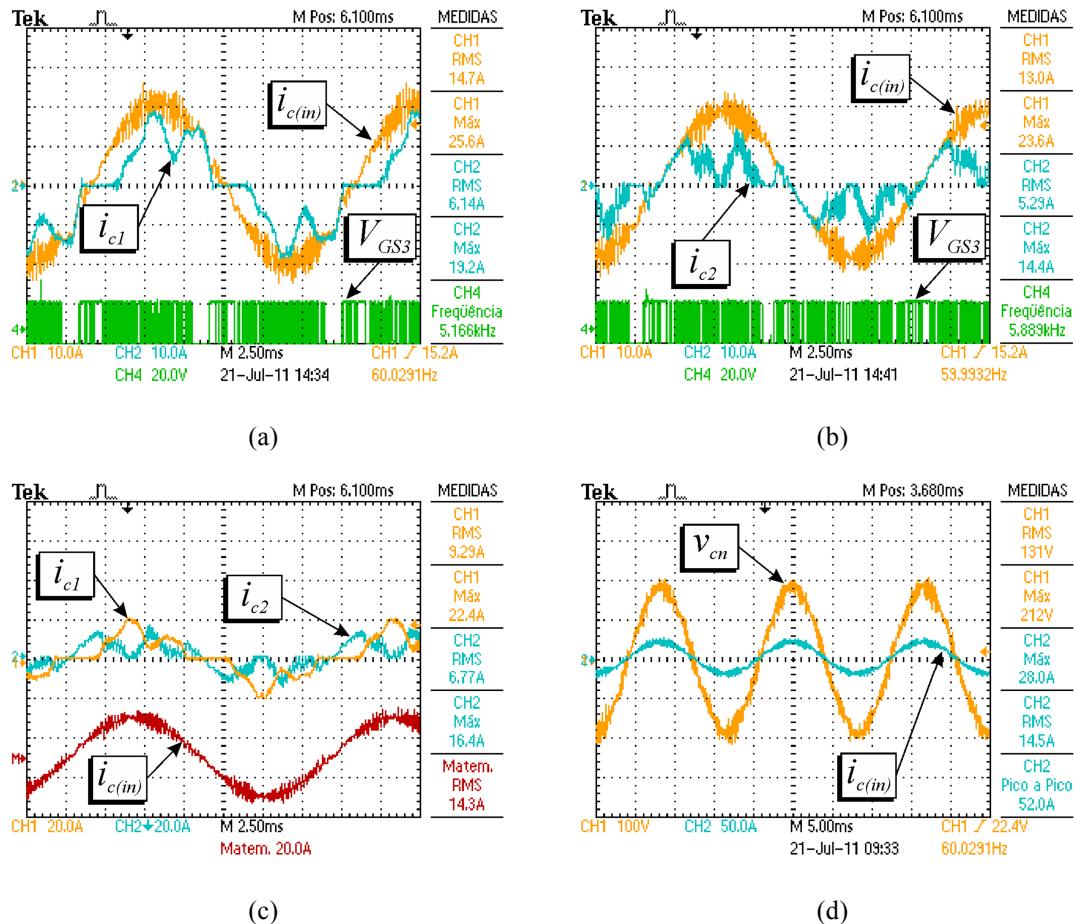

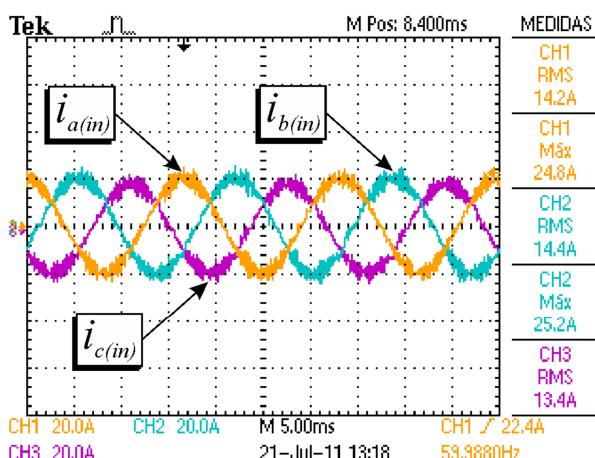

As Fig. 5.9 a 5.11 demonstram como são realizadas as composições das correntes de linha de entrada das fases A, B e C. Observa-se que as correntes de entrada são os resultados das combinações das correntes drenadas por cada fase de Ret-1 e de Ret-2. Percebe-se que a forma de onda da corrente é senoidal e em fase com a tensão de entrada, assegurando um elevado fator de potência.

Observa-se ainda, que são justamente as correntes de linha impostas por Ret-2 que determinam a forma de onda próxima da senoidal das correntes resultantes. Vale comentar que a frequência de chaveamento registrado pelo osciloscópio foi variável, não ultrapassando a 20 kHz, uma vez que, essa frequência depende da dinâmica do sistema e dos intervalos que ocorrem ou não o chaveamento.

(a)

(b)

Fig. 5.9 – Fase A: (a) Correntes  $i_{a(in)}$  e  $i_{a1}$ ; (b) correntes  $i_{a(in)}$  e  $i_{a2}$ ; (c) somatório das correntes  $i_{a1}$  e  $i_{a2}$ , resultando em  $i_{a(in)}$ ; e (d) corrente  $i_{a(in)}$  em fase com a tensão  $v_{an}$ .

Fig. 5.11 – Fase C: (a) Correntes  $i_{c(in)}$  e  $i_{c1}$ ; (b) correntes  $i_{c(in)}$  e  $i_{c2}$ ; (c) somatório das correntes  $i_{c1}$  e  $i_{c2}$ , resultando em  $i_{c(in)}$ ; e (d) corrente  $i_{c(in)}$  em fase com a tensão  $v_{cn}$ .

A Fig. 5.12 ilustra as correntes de linha de entrada das três fases, comprovando a eficácia da solução proposta no que diz respeito à imposição de correntes de alimentação senoidais e à mitigação do conteúdo harmônico destas correntes de acordo com norma IEC 61000-3-2.

Fig. 5.12 – Correntes de linha de alimentação das fases A, B e C.