UNIVERSIDADE FEDERAL DE UBERLÂNDIA

FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA

ELÉTRICA

ANÁLISE E DESENVOLVIMENTO DE UM NOVO

CONVERSOR CA-CC HÍBRIDO MONOFÁSICO COM

CONTROLE DIGITAL BASEADO EM DSP

GUSTAVO BRITO DE LIMA

JULHO

2011

**UNIVERSIDADE FEDERAL DE UBERLÂNDIA

FACULDADE DE ENGENHARIA ELÉTRICA

PÓS-GRADUAÇÃO EM ENGENHARIA

ELÉTRICA**

**ANÁLISE E DESENVOLVIMENTO DE UM NOVO CONVERSOR

CA-CC HÍBRIDO MONOFÁSICO COM CONTROLE DIGITAL

BASEADO EM DSP**

**Gustavo Brito de Lima<sup>1</sup>**

Dissertação de mestrado submetida à Universidade Federal de Uberlândia – Núcleo de Pesquisas em Eletrônica de Potência (NUPEP), perante a banca de examinadores abaixo, como parte dos requisitos necessários para obtenção do título de Mestre em Ciências.

Banca Examinadora:

Luiz Carlos Gomes de Freitas, Dr. – Orientador (UFU)

Falcondes J. Mendes de Seixas, Dr. (FEIS-UNESP)

João Batista Vieira Júnior, Dr. (UFU)

Luiz Carlos de Freitas, Dr. (UFU)

<sup>1</sup> A Bolsa de Estudos, para esta pesquisa, foi concedida pela CAPES, Brasil.

*“O único lugar onde o sucesso vem antes do trabalho é no dicionário”*

*Albert Einstein*

# Dedicatória

*Aos meus pais Antônio e Inês,

À minha irmã Gabriela,

Aos meus avós Antônio, Placídia, Raimundo e Francisca,

À minha namorada Camila,

À toda minha família por sempre acreditar na minha capacidade.*

# Agradecimentos

Primeiramente quero agradecer a Deus por ter abençoado cada um dos meus dias, por sempre me iluminar, por sempre estar presente.

Ao professor orientador e amigo Luiz Carlos Gomes de Freitas pelo apoio, paciência, bons conselhos e principalmente pela confiança maciça que me impulsionou para chegar até aqui.

Ao professor Luiz Carlos de Freitas, o Pratinha, pelos conselhos sempre oportunos que, com toda certeza, foram ímpares para o desenvolvimento deste trabalho.

Ao meu pai, Antônio, minha mãe, Inês, minha irmã, Gabriela e meus avós que são o alicerce de tudo e, simplesmente, indispensáveis.

À minha namorada, Camila Mendonça, pela paciência, confiança e por estar sempre ao meu lado, em todos os momentos, e por fazer destes os melhores da minha vida.

À Vó Dalva, Osvaldo, Luisa, Mariana e Isabella por me acolher sempre e me dar a oportunidade de, mesmo longe de casa, me sentir em casa.

Aos meus amigos de trabalho Lucas, Willian, Vilefort, Paulo Henrique, Rafael Martins, Fabrício, Diógenes, Danillo, Admarço, Rafael Lodo, Natalia, Alexandre, Lucio, Fernando, Pedro, Vinicius, Marcelo, Leandro, Renato e todos os outros amigos de graduação.

Enfim, agradeço a todos aqueles que de forma direta ou indireta contribuíram o desenvolvimento deste trabalho.

# **Resumo**

Este trabalho apresenta o desenvolvimento e análise experimental de uma nova estrutura de retificador híbrido monofásico, com elevado fator de potência (FP) e reduzida distorção harmônica de corrente ( $DHT_I$ ) para aplicação como estágio pré-regulador de sistemas de alta potência. A estrutura proposta é composta por um retificador monofásico de onda completa não controlado convencional, associado em paralelo a um conversor chaveado não isolado. Destaca-se que o conversor monofásico chaveado é capaz de compor a corrente de entrada, proporcionando elevado FP e reduzida  $DHT_I$ , tal como nos pré-reguladores convencionais, porém, o conversor chaveado processa menos de 50% da potência total de saída, garantindo robustez e confiabilidade para a estrutura. Foram desenvolvidos dois protótipos de 1 kW e 10 kW com controle digital para imposição na rede CA de alimentação, em qualquer condição de carga. A técnica de controle PWM utilizada é capaz de limitar a contribuição do conversor chaveado e, ao mesmo tempo, impor uma corrente de entrada cujo espectro harmônico está em conformidade com os limites impostos pelas normas internacionais IEC61000-3-2 e IEC61000-3-4. Todo o estudo teórico, a análise matemática e os resultados experimentais obtidos são apresentados neste trabalho.

## **Palavras-chave**

Correção do Fator de Potência, DSP, Distorção Harmônica Total, Retificadores Híbridos Monofásicos.

# **Abstract**

This work presents the development and the experimental analysis of a new single-phase hybrid rectifier with high power factor (PF) and low harmonic distortion of current (THD<sub>I</sub>), suitable for high power application. The proposed structure is composed by an ordinary single-phase diode rectifier with parallel connection of a switched converter. It is outlined that the switched converter is capable of composing the input line current waveform assuring high PF and low THD<sub>I</sub>. However, the power rating of the switched converter is lesser than 50% of the total output power, assuring robustness and reliability for the proposed hybrid rectifier. Two prototypes rated at 1 kW and 10 kW were developed and analyzed in laboratory, using digital control technique. A PWM control strategy was implemented imposing quasi-sinusoidal line input current waveform and limiting the switched converter power contribution. It was found that the line input current harmonic spectrum is in accordance with the harmonic limits imposed by IEC61000-3-2 and IEC61000-3-4. The principle of operation, the mathematical analysis, and experimental results from a 1 kW and 10 kW prototypes are also presented in this work.

## **Key-words**

**Power Factor Correction, DSP, Total Harmonic Distortion, Single-Phase Hybrid Rectifiers.**

# SUMÁRIO

|                                                               |           |

|---------------------------------------------------------------|-----------|

| <b>1. Introdução.....</b>                                     | <b>20</b> |

| 1.1 Introdução Geral .....                                    | 20        |

| 1.2 Considerações iniciais .....                              | 22        |

| 1.3 Estrutura da Dissertação .....                            | 23        |

| 1.3.1 – Capítulo 2 .....                                      | 23        |

| 1.3.2 – Capítulo 3 .....                                      | 23        |

| 1.3.3 – Capítulo 4 .....                                      | 23        |

| 1.3.4 – Capítulo 5 .....                                      | 24        |

| 1.3.5 – Conclusões .....                                      | 24        |

| 1.3.6 – Anexos .....                                          | 24        |

| <b>2. Estado da Arte.....</b>                                 | <b>25</b> |

| 2.1 Introdução Geral .....                                    | 25        |

| 2.2 Conversores CC-CC Básicos .....                           | 25        |

| 2.3 Topologias Modificadas de Conversores PFC .....           | 27        |

| 2.3.1 – Conversor Boost Modificado .....                      | 27        |

| 2.3.3 – Conversor Buck Modificado .....                       | 32        |

| 2.4 Conversores PFC Operando em Paralelo .....                | 33        |

| 2.4.1 Conversores Flyback e Forward Operando em Paralelo..... | 34        |

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| 2.4.2 Retificador Híbrido Monofásico Proposto.....                             | 35        |

| 2.5 Conclusão .....                                                            | 38        |

| <b>3. Operação do Retificador Híbrido Monofásico Proposto....</b>              | <b>39</b> |

| 3.1 Introdução Geral .....                                                     | 39        |

| 3.2 Operação do Retificador Híbrido Monofásico .....                           | 39        |

| 3.2.1 Etapas de Operação .....                                                 | 41        |

| 3.3 Projeto do Retificador Não Controlado (Ret-1) .....                        | 43        |

| 3.3.1 Dimensionamento Retificador não Controlado do<br>Protótipo de 1 kW ..... | 46        |

| 3.3.2 Dimensionamento Retificador não Controlado do<br>Protótipo de 10 kW..... | 47        |

| 3.4 Projeto do Conversor Chaveado (Ret-2).....                                 | 48        |

| 3.4.1 Dimensionamento do Protótipo de 1 kW.....                                | 48        |

| 3.4.2 Dimensionamento do Protótipo de 10 kW.....                               | 49        |

| 3.5 Estratégia de Controle.....                                                | 50        |

| 3.6 Implementação da Estratégia de Controle.....                               | 52        |

| 3.6.1 Processador de Sinais Digitais-DSP.....                                  | 53        |

| 3.6.2 DSP TMS320F28335 – Características Gerais.....                           | 56        |

| 3.7 Fluxograma da Estratégia de Controle.....                                  | 59        |

| 3.7.1 Declaração das Variáveis .....                                           | 59        |

| 3.7.2 Configuração dos Registros do Sistema .....                              | 62        |

|                                  |    |

|----------------------------------|----|

| 3.7.3 Rotina de Interrupção..... | 63 |

| 3.8 Conclusão .....              | 75 |

## **4. Modelagem Matemática e Resultados de Simulação**

### **Computacional..... 77**

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| 4.1 Introdução Geral .....                                                          | 77 |

| 4.2 Modelagem do Circuito de Potência do RHM Utilizando Variáveis de Estado.....    | 78 |

| 4.2.1 Circuito Equivalente para Interruptor Fechado .....                           | 80 |

| 4.2.2 Circuito Equivalente para Interruptor Aberto .....                            | 82 |

| 4.2.3 Vetor Resposta .....                                                          | 83 |

| 4.3 Representação da Lógica de Controle Aplicada no Modelo Matemático .....         | 84 |

| 4.4 Solução do Modelo Matemático.....                                               | 86 |

| 4.5 Resultados de Simulação Utilizando o Modelo Matemático ....                     | 88 |

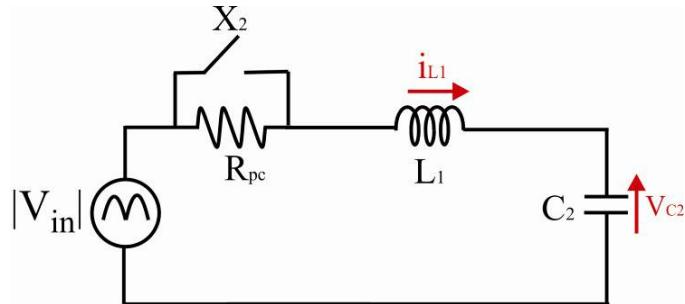

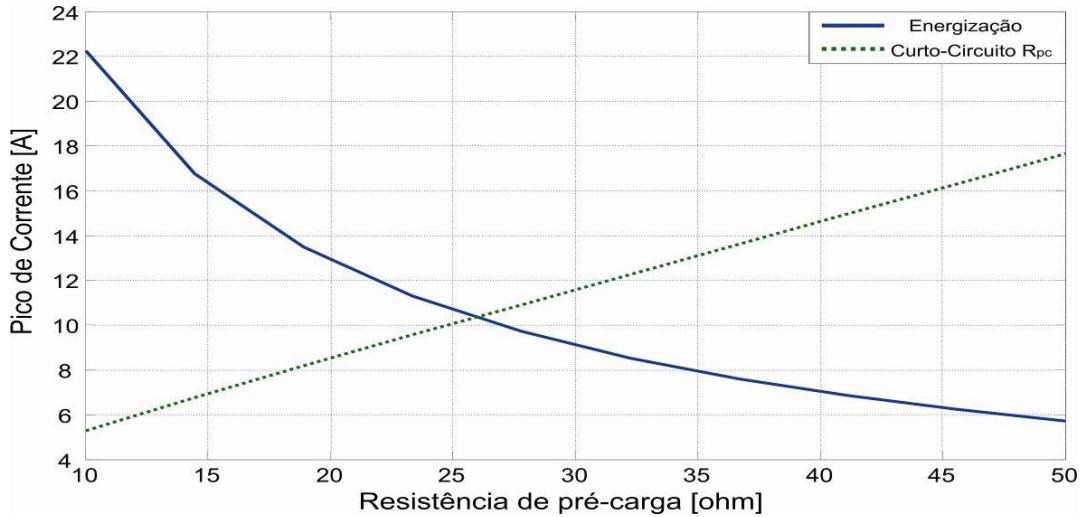

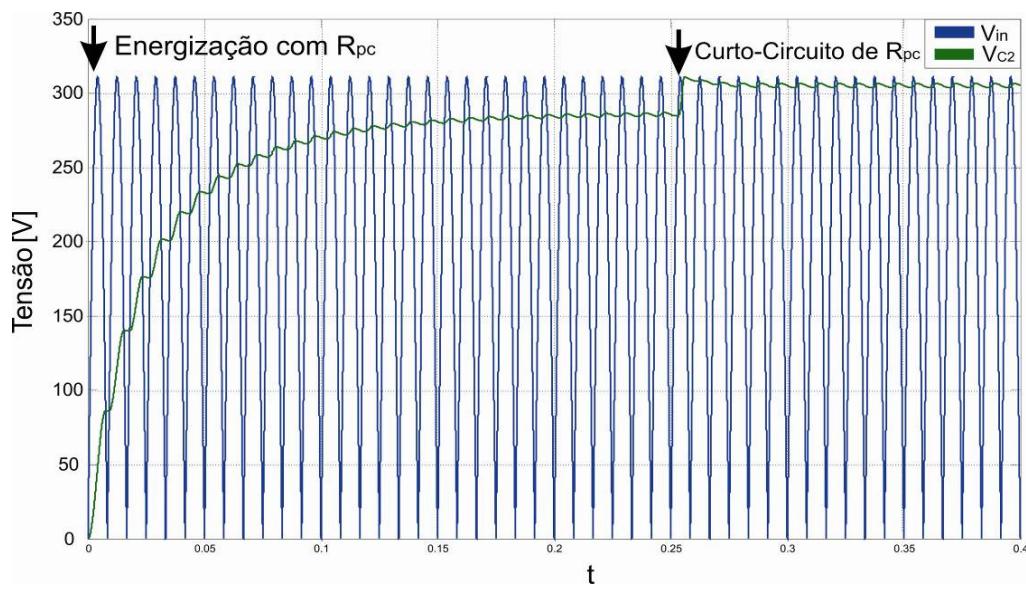

| 4.6 Cálculo de Resistência de Pré-Carga .....                                       | 93 |

| 4.6.1 Matrizes características do circuito de pré-carga do capacitor de saída ..... | 94 |

| 4.6.2 Solução do Modelo Matemático.....                                             | 94 |

| 4.7 Resultados de Simulação Utilizando o Orcad <sup>®</sup> .....                   | 96 |

| 4.8 Aplicação do Modelo Matemático na Implementação do Controle Digital .....       | 99 |

|                                                               |            |

|---------------------------------------------------------------|------------|

| 4.9 Conclusão.....                                            | 102        |

| <b>5. Resultados Experimentais.....</b>                       | <b>104</b> |

| 5.1 Introdução Geral .....                                    | 104        |

| 5.2 Diagrama Esquemático dos Protótipos de 1 kW e 10 kW ..... | 104        |

| 5.2.1 Placas de Aquisição de Sinal .....                      | 105        |

| 5.2.2 Sensor de Temperatura .....                             | 106        |

| 5.2.3 Conversão de Sinal.....                                 | 107        |

| 5.2.4 <i>Gate-Driver SKHI 10/12</i> .....                     | 107        |

| 5.2.5 Circuito de Controle dos Contatores.....                | 108        |

| 5.3 Construção do Protótipo de 1 kW.....                      | 112        |

| 5.3.1 Resultados Experimentais do Protótipo de 1 kW .....     | 117        |

| 5.4 Construção do Protótipo de 10 kW.....                     | 121        |

| 5.4.1 Resultados Experimentais do Protótipo de 10 kW .....    | 126        |

| 5.5 Conclusão .....                                           | 132        |

| <b>6. Conclusões Gerais.....</b>                              | <b>133</b> |

| <b>Referências Bibliográficas .....</b>                       | <b>136</b> |

| <b>Apêndices .....</b>                                        | <b>142</b> |

# **Lista de Figuras**

|     |                                                                                                                                       |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Conversor boost <i>bridgeless</i> (a) simétrico e (b) assimétrico.....                                                                | 29 |

| 2.2 | Conversor boost com três níveis.....                                                                                                  | 30 |

| 2.3 | Conversor boost PFC com célula de chaveamento com 3 estados..                                                                         | 31 |

| 2.4 | Conversor SEPIC modificado.....                                                                                                       | 32 |

| 2.5 | Conversor Buck modificado.....                                                                                                        | 33 |

| 2.6 | Fluxo de potencia de conversores operando em modo (a) cascateado<br>e (b) paralelo.....                                               | 34 |

| 2.7 | Conversores chaveados operando em paralelo.....                                                                                       | 35 |

| 2.8 | Arranjo topológico do retificador híbrido monofásico.....                                                                             | 36 |

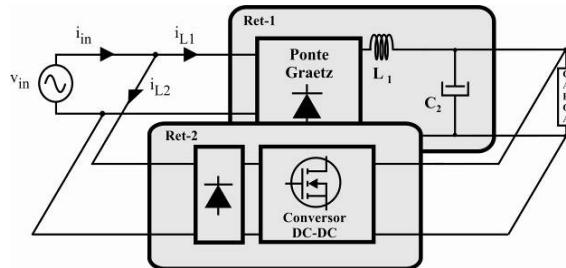

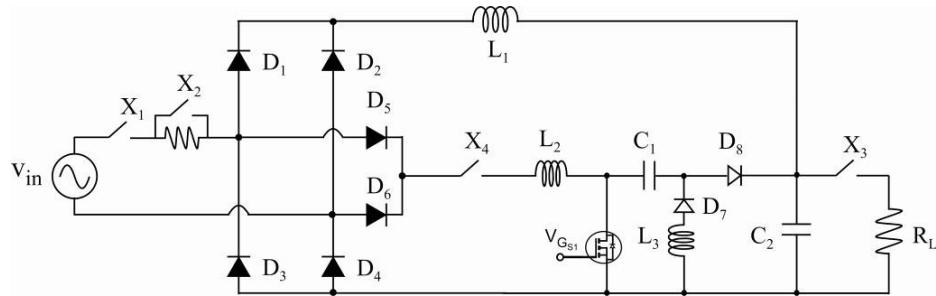

| 3.1 | Arranjo topológico do retificador híbrido monofásico.....                                                                             | 40 |

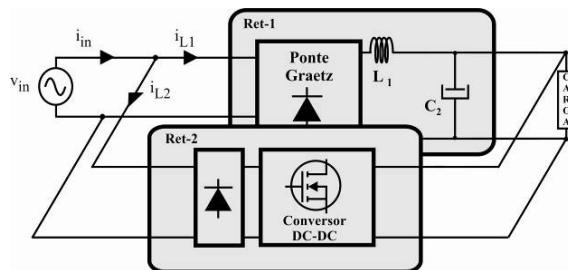

| 3.2 | Formas de onda teóricas de corrente $i_{L1}$ , $i_{L2}$ , $i_{in}$ .<br>A forma de onda tracejada representa a tensão de entrada..... | 41 |

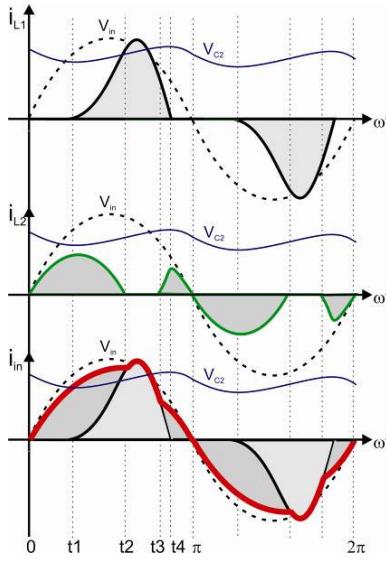

| 3.3 | Conversor SEPIC.....                                                                                                                  | 48 |

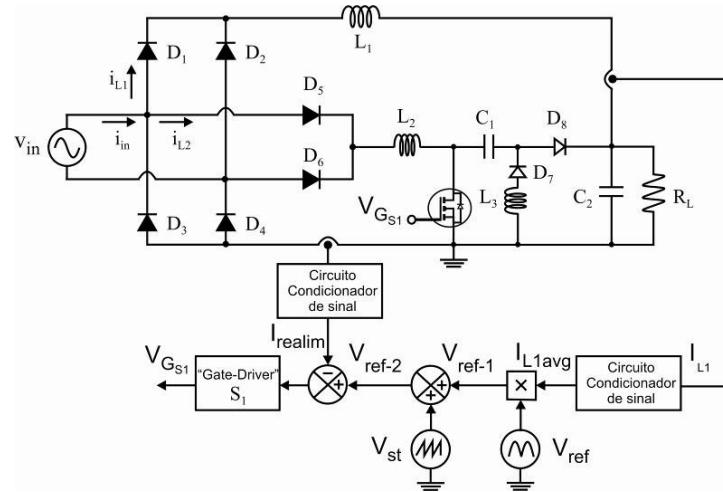

| 3.4 | Diagrama esquemático do circuito de controle.....                                                                                     | 51 |

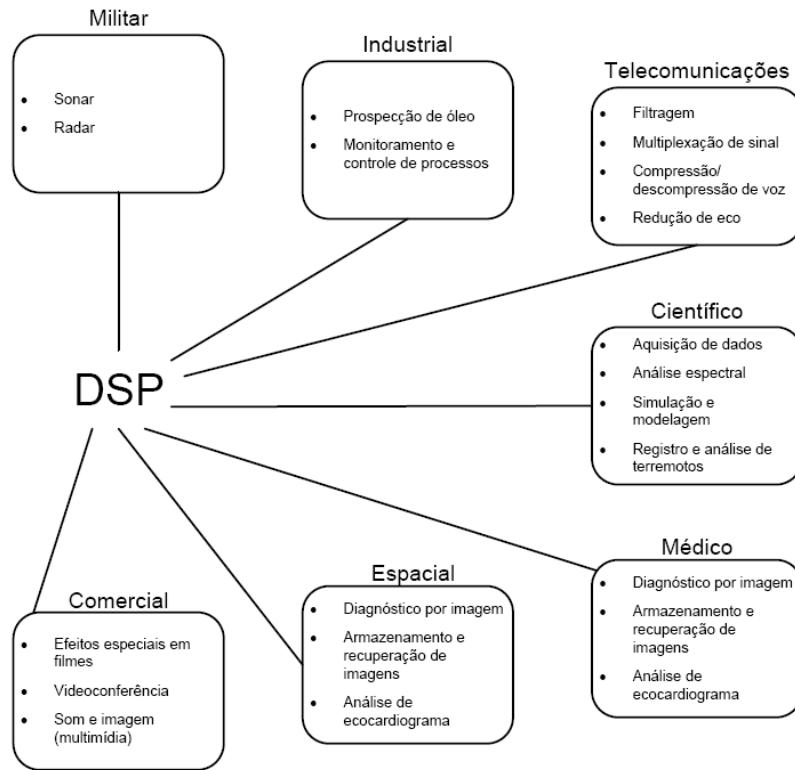

| 3.5 | Aplicações do DSP.....                                                                                                                | 54 |

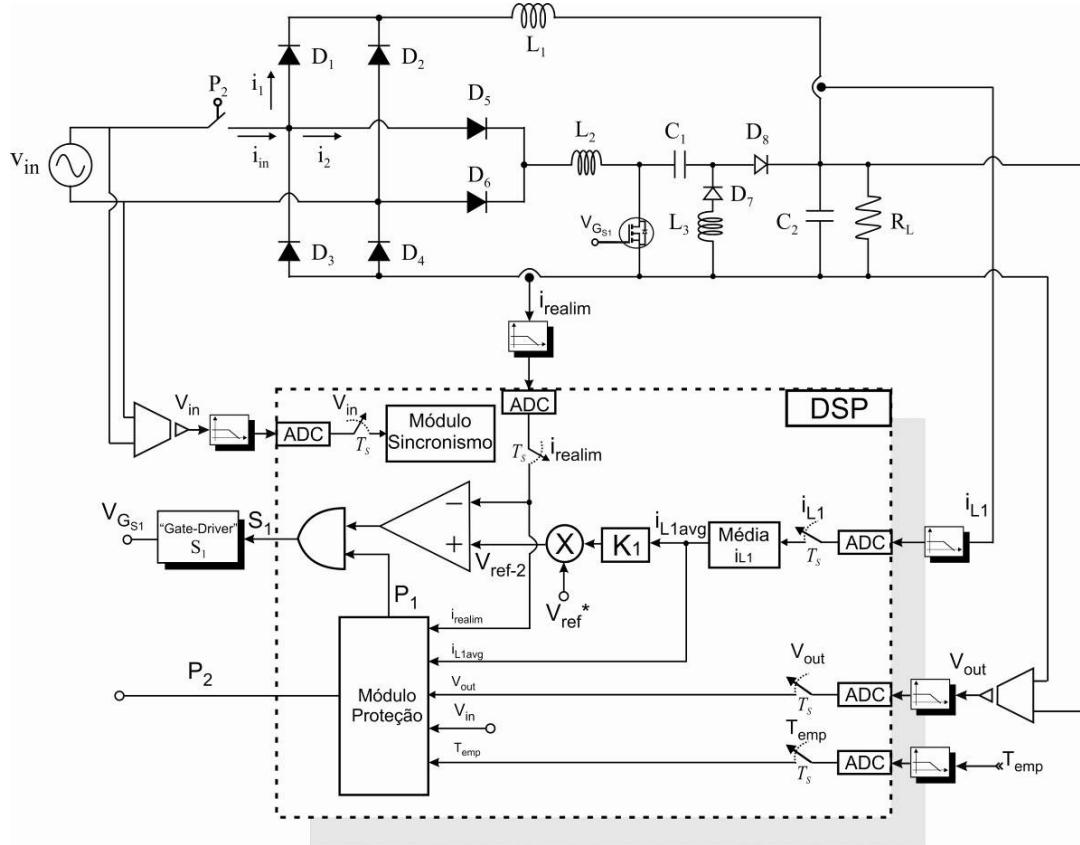

| 3.6 | Diagrama de blocos digital.....                                                                                                       | 57 |

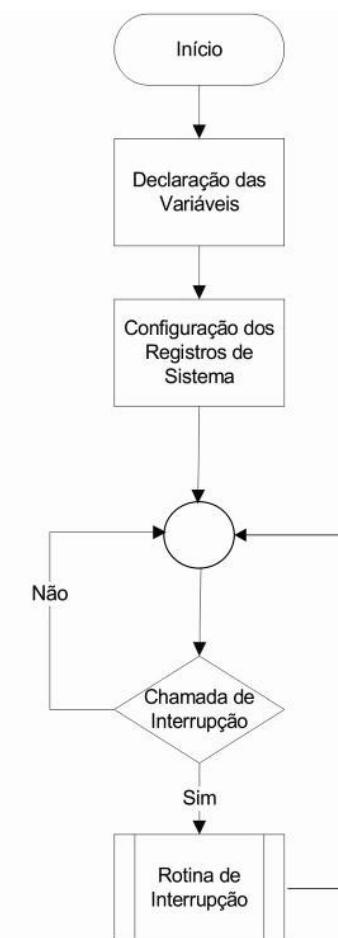

| 3.7 | Fluxograma do circuito de controle.....                                                                                               | 59 |

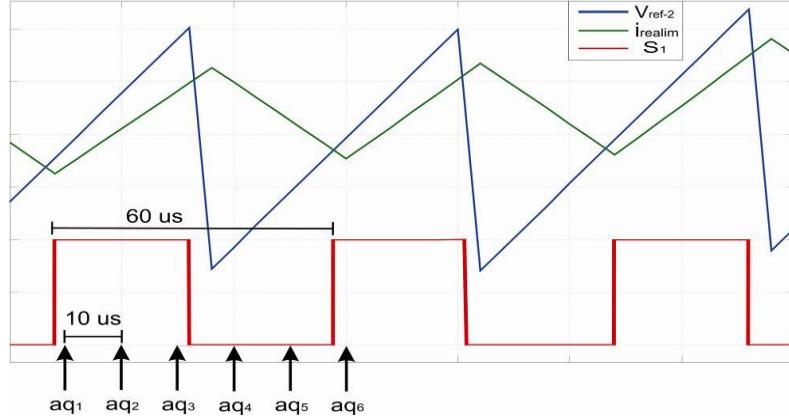

| 3.8 | Período de aquisição (10 $\mu s$ ) e período de chaveamento (60 $\mu s$ )..                                                           | 62 |

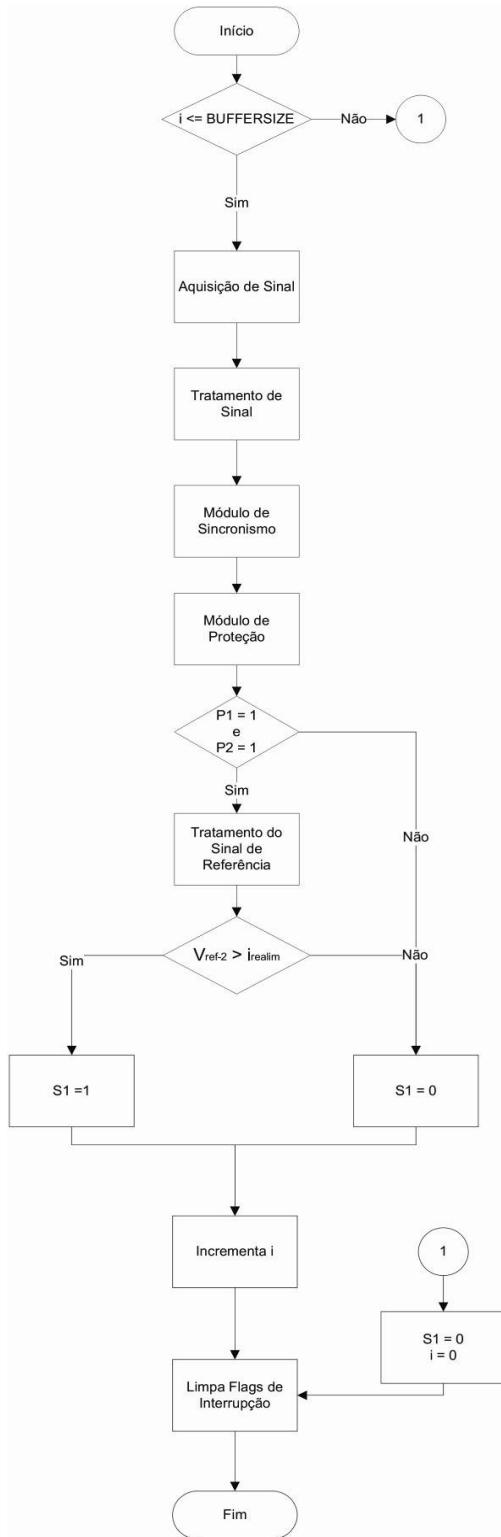

| 3.9 | Rotina de Interrupção.....                                                                                                            | 65 |

|      |                                                                                                                                                                          |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

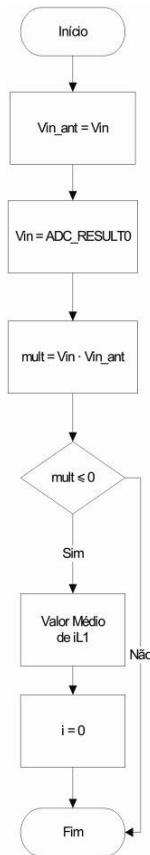

| 3.10 | Fluxograma do módulo de sincronismo.....                                                                                                                                 | 68 |

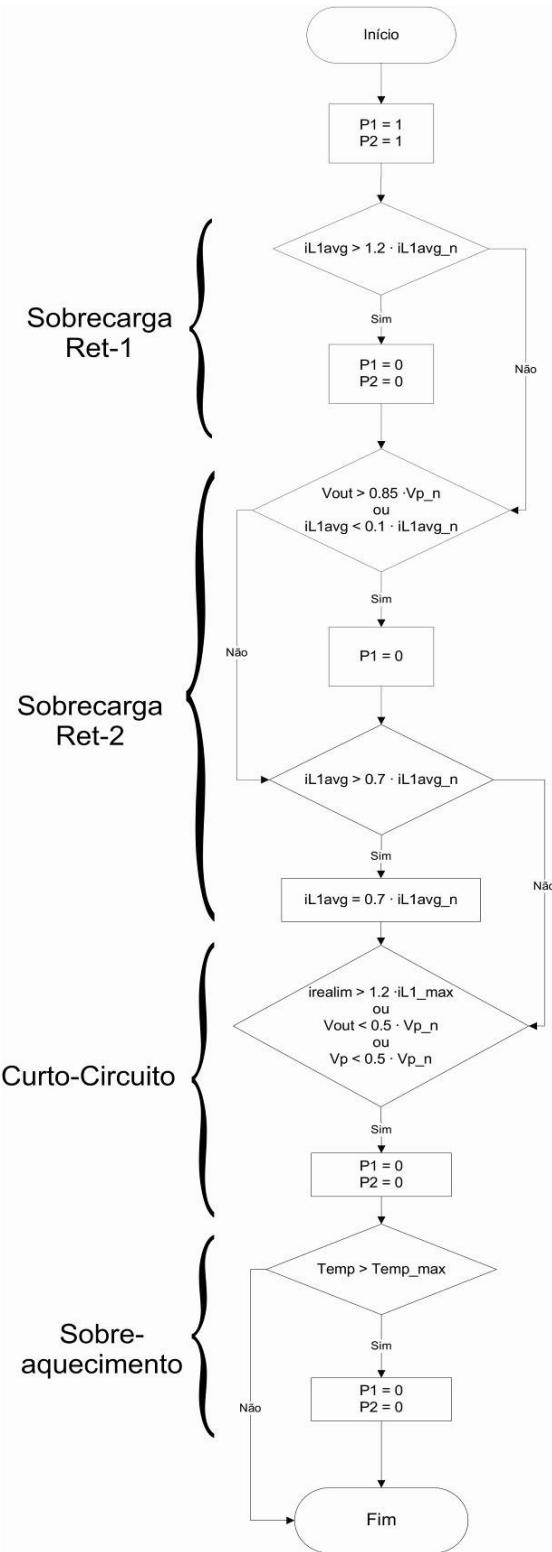

| 3.11 | Módulo de proteção.....                                                                                                                                                  | 71 |

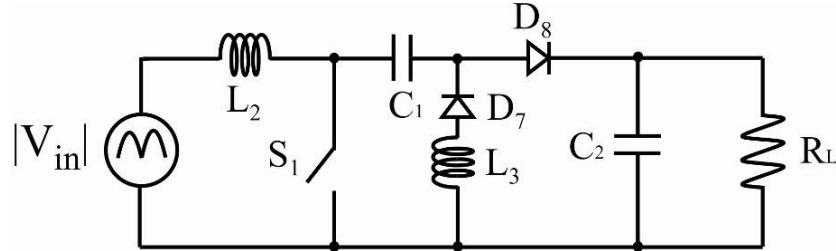

| 4.1  | Círcito de potência do RHM modelado.....                                                                                                                                 | 79 |

| 4.2  | Simplificação do círcito modelado.....                                                                                                                                   | 80 |

| 4.3  | Círcito equivalente com o interruptor S <sub>1</sub> fechado.....                                                                                                        | 81 |

| 4.4  | Círcito equivalente com o interruptor S <sub>1</sub> aberta.....                                                                                                         | 82 |

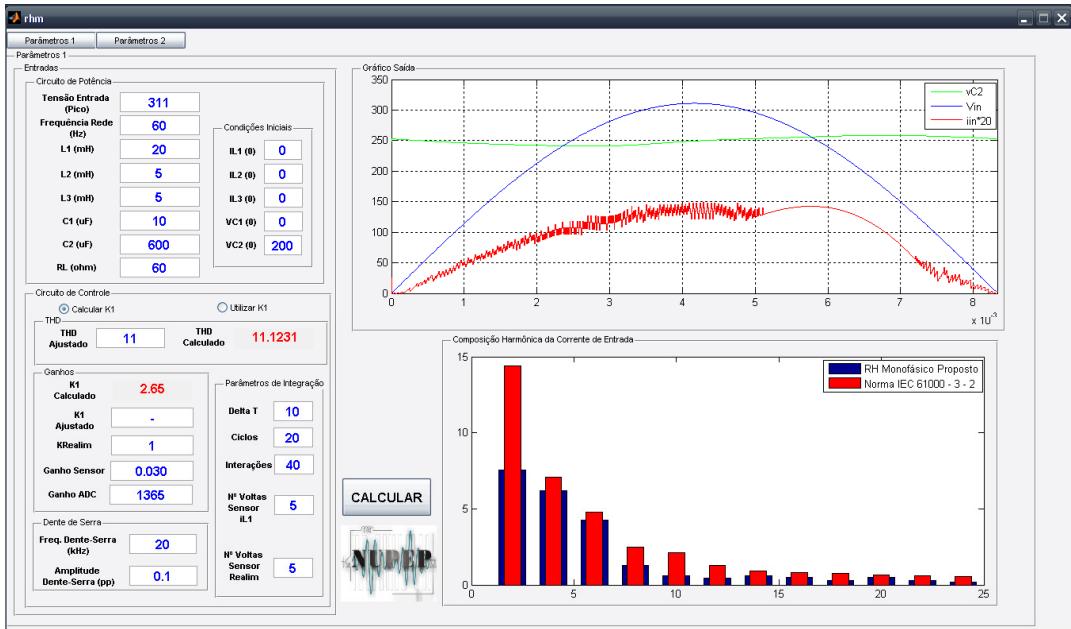

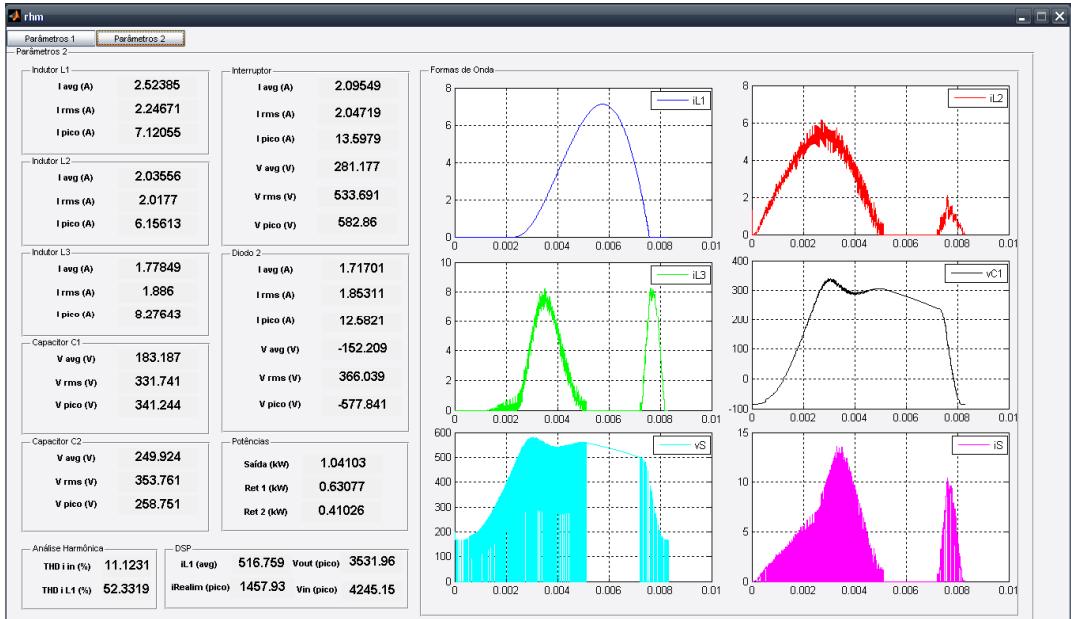

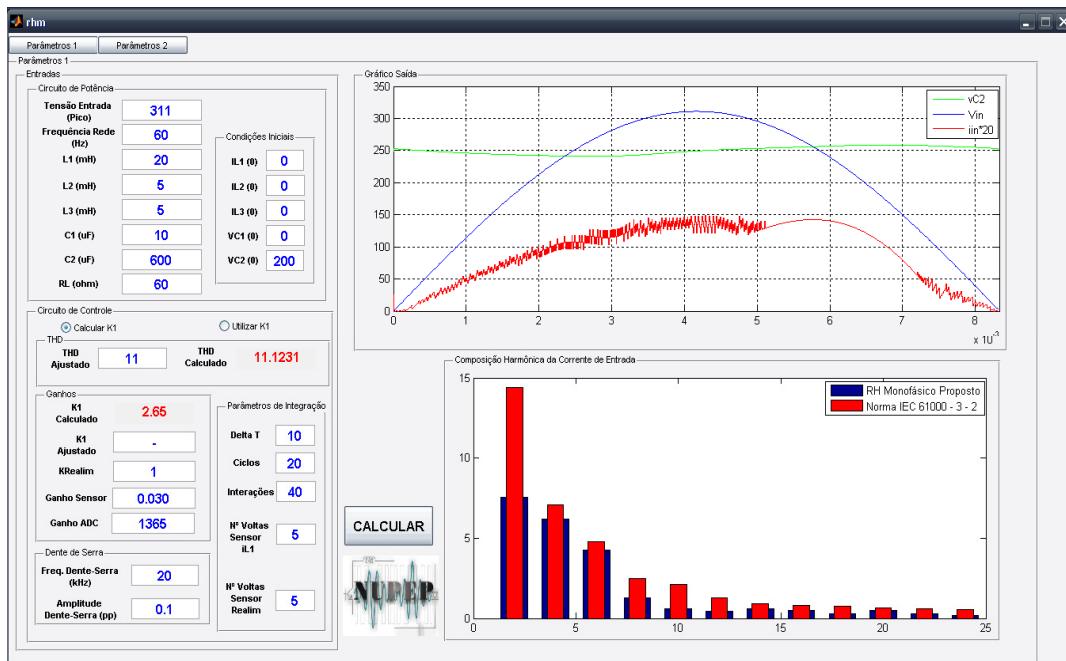

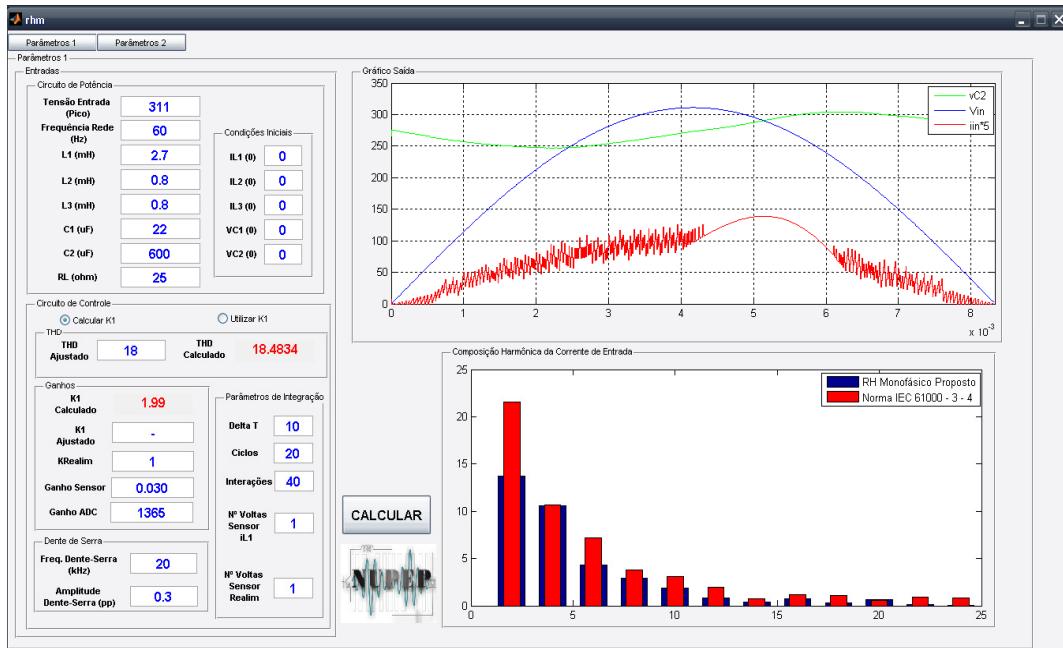

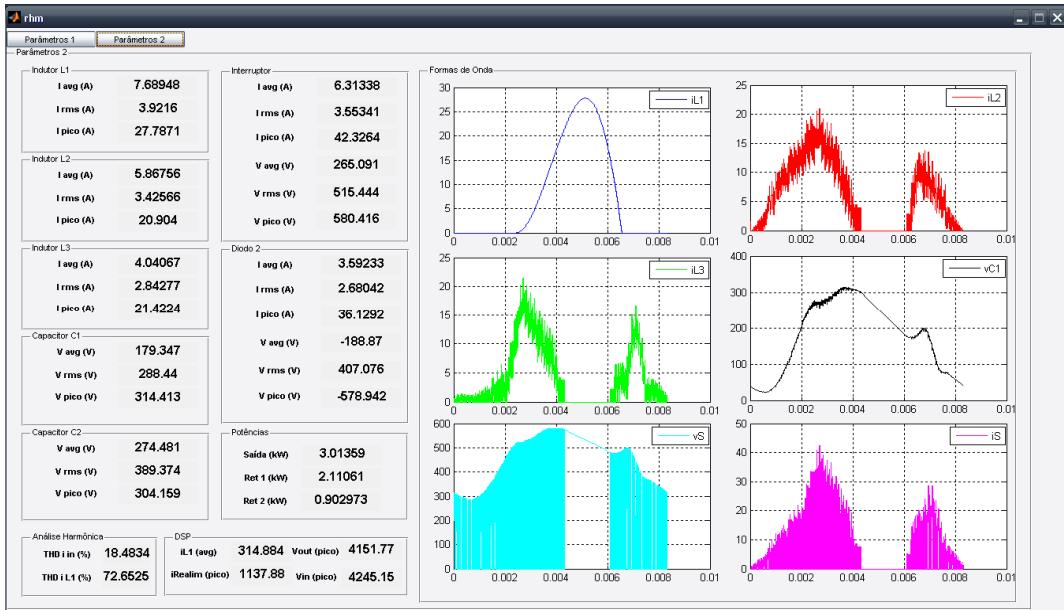

| 4.5  | Interface 1 do programa desenvolvido na plataforma Matlab <sup>®</sup> .....                                                                                             | 89 |

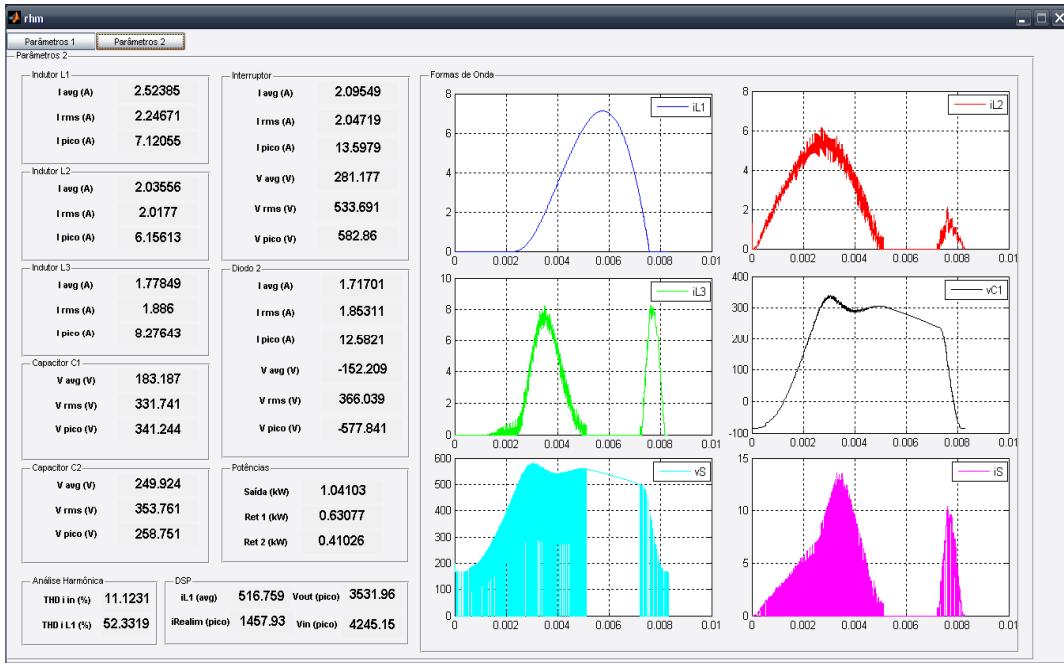

| 4.6  | Interface 2 do programa desenvolvido na plataforma Matlab <sup>®</sup> .....                                                                                             | 89 |

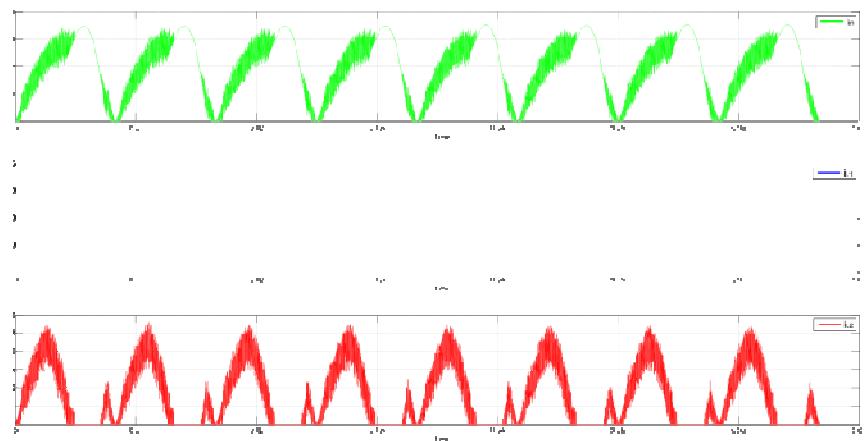

| 4.7  | Correntes drenadas pelo Ret-1 ( $i_{L1}$ ) e Ret-2 ( $i_{L2}$ ) e sua composição<br>( $i_{in}$ ).....                                                                    | 91 |

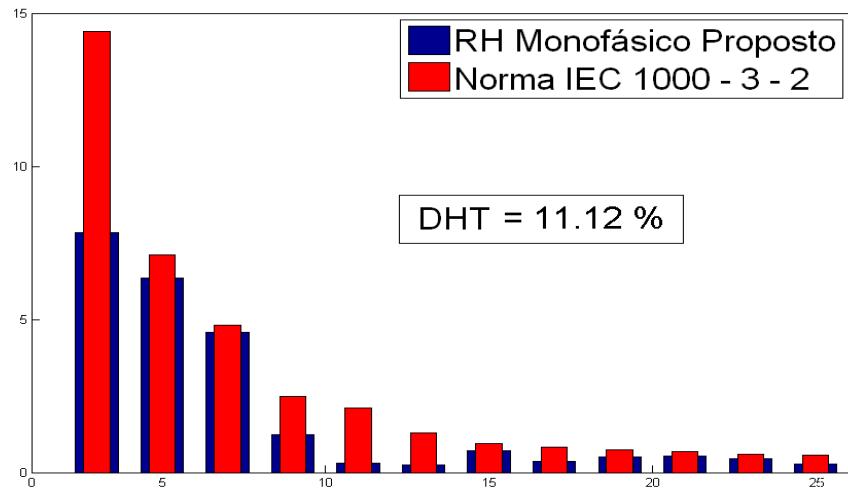

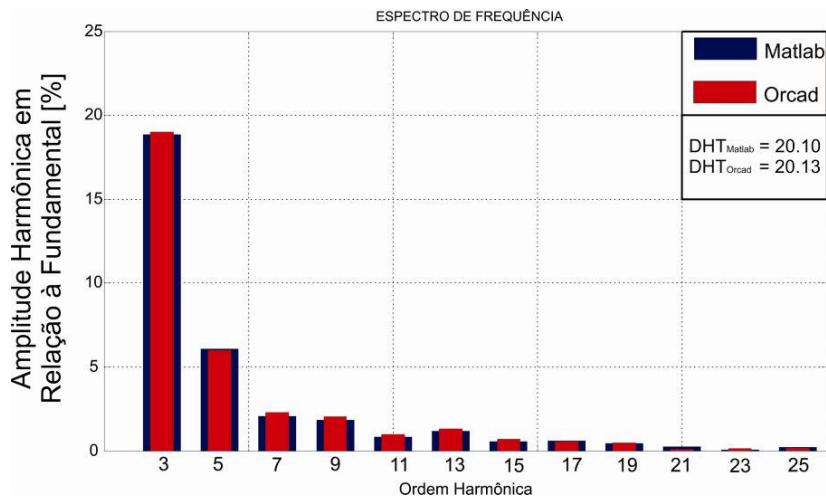

| 4.8  | Decomposição harmônica da corrente CA de entrada.....                                                                                                                    | 91 |

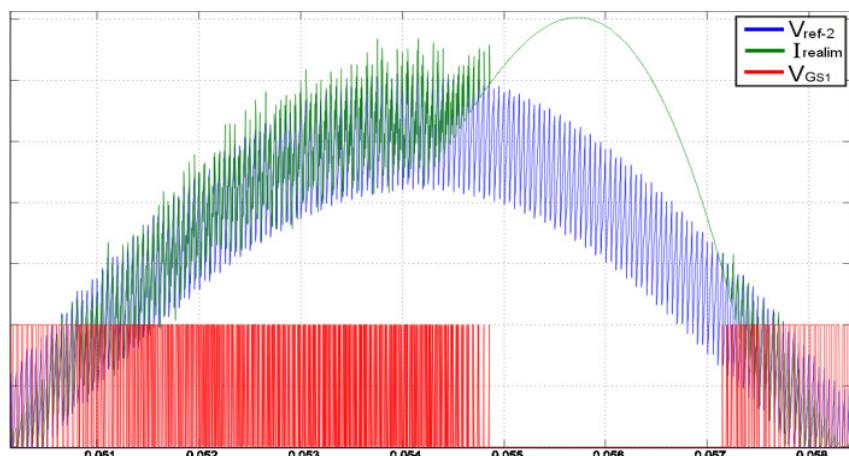

| 4.9  | Sinais de referência de corrente ( $V_{ref-2}$ ), de realimentação( $i_{realim}$ ) e<br>sinal lógico proveniente da comparação destes sinais ( $V_{GS1}$ ).....          | 91 |

| 4.10 | Círcito de pré-carga do capacitor de saída C <sub>2</sub> .....                                                                                                          | 93 |

| 4.11 | Pico da corrente na energização e no curto-círcito da resistência<br>de pré-carga em função da resistência de pré-carga ( $R_{pc}$ ).....                                | 95 |

| 4.12 | (a) Tensão de entrada ( $V_{in}$ ) e saída ( $V_{C2}$ ) e (b) corrente $i_{L1}$ durante<br>a pré carga do capacitor de saída C <sub>2</sub> para $R_{pc} = 25$ ohm.....  | 96 |

| 4.13 | Círcito Simulado no Orcad <sup>®</sup> .....                                                                                                                             | 97 |

| 4.14 | Tensão de entrada ( $V_{in}$ ), saída ( $V_{C2}$ ) e corrente de entrada<br>( $i_{in}$ ) obtidos por simulação no (a) Orcad <sup>®</sup> e (b) Matlab <sup>®</sup> ..... | 98 |

| 4.15 | Corrente de entrada ( $i_{in}$ ) obtidos por simulação no (a) Orcad <sup>®</sup> e                                                                                       |    |

|                                                                                                                                              |     |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| (b) Matlab® .....                                                                                                                            | 98  |

| 4.16 Decomposição harmônica da corrente CA de entrada obtida<br>no Orcad® e Matlab® através da solução do modelo<br>matemático proposto..... | 99  |

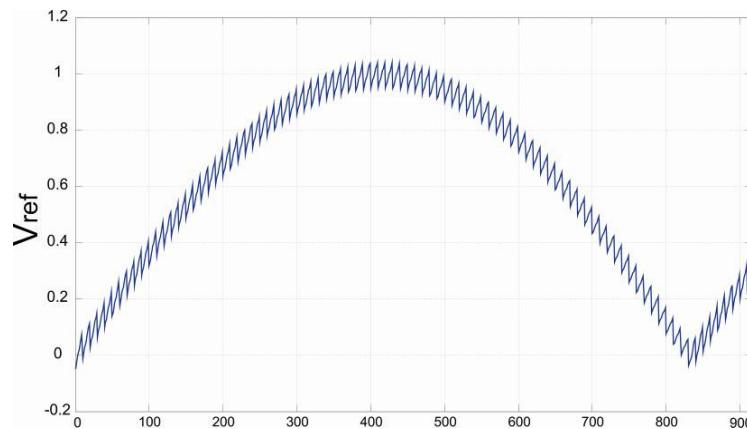

| 4.17 Senóide digital retificada ( $V_{ref}$ ) gerada no Matlab® .....                                                                        | 100 |

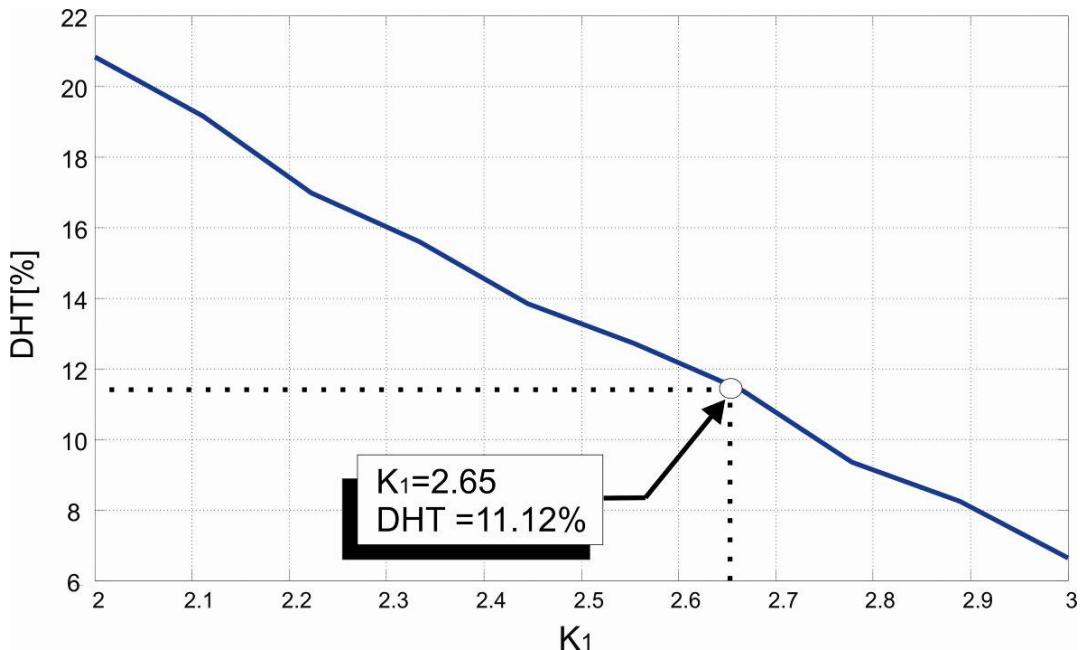

| 4.18 Distorção harmônica total da corrente de entrada obtida através<br>da análise matemática apresentada para $2 \leq K_1 \leq 3$ .....     | 101 |

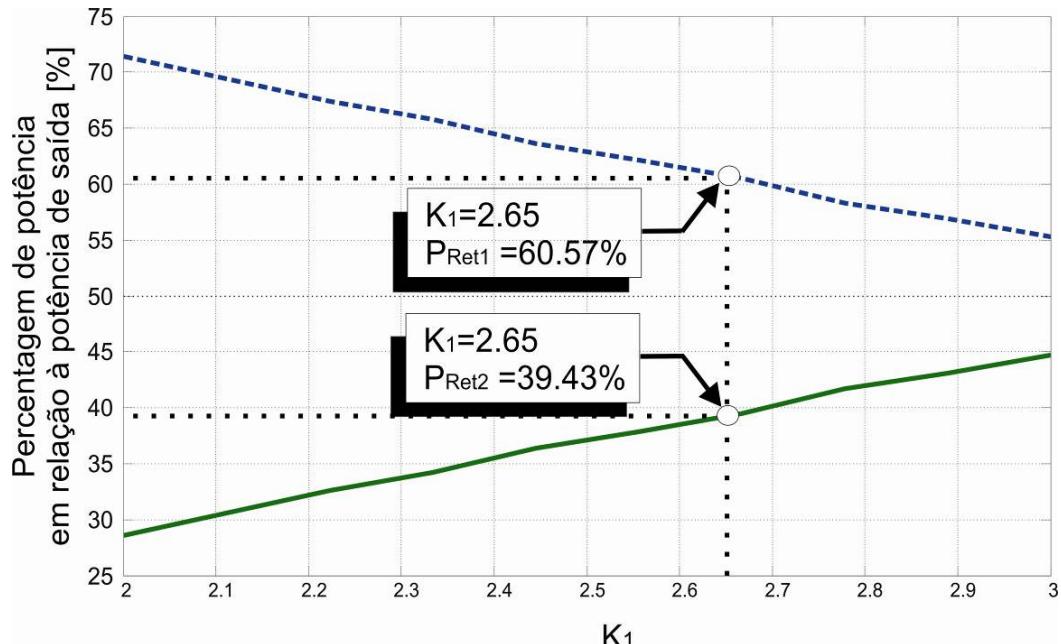

| 4.19 Parcela de contribuição de potência ativa média de cada<br>retificador para $1 \leq K_1 \leq 3$ .....                                   | 102 |

| <br>                                                                                                                                         |     |

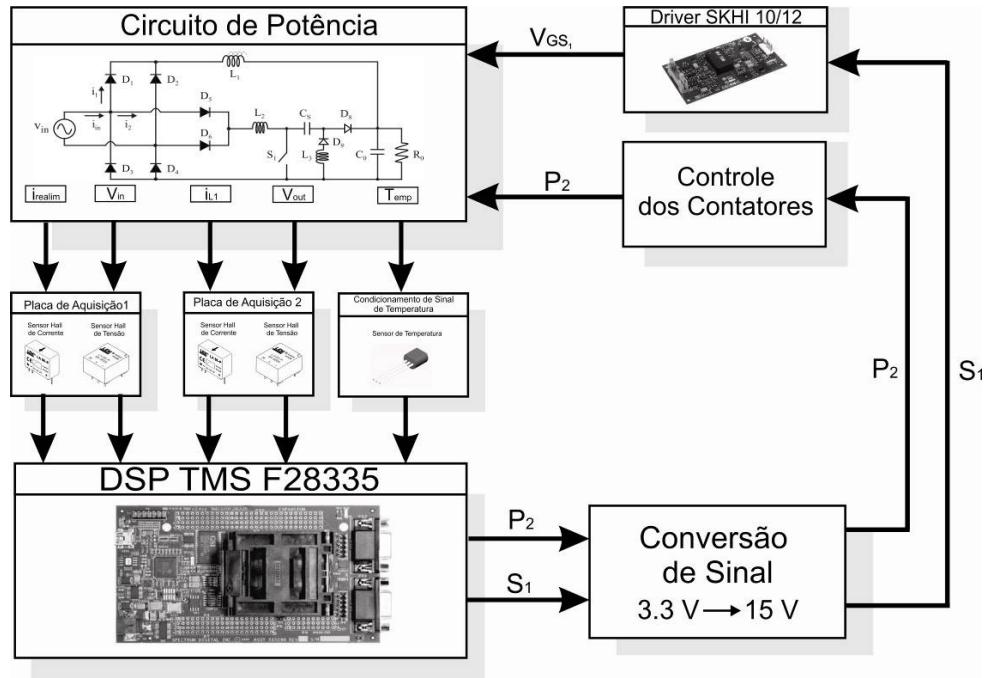

| 5.1 Diagrama esquemático dos protótipo de 1 kW e 10 kW.....                                                                                  | 105 |

| 5.2 Placas de aquisição de tensão e corrente.....                                                                                            | 105 |

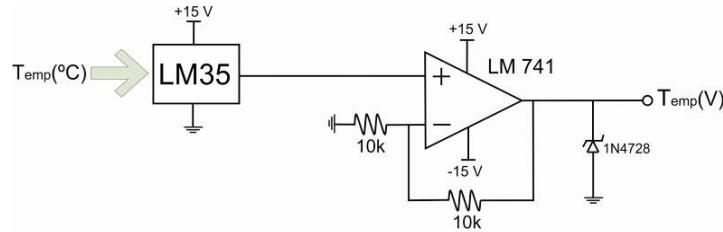

| 5.3 Condicionamento de sinal do sensor de temperatura.....                                                                                   | 106 |

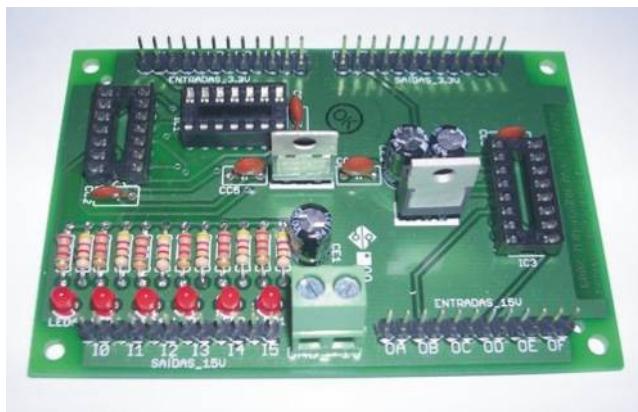

| 5.4 Placa de conversão de 3,3 V para 15 V.....                                                                                               | 107 |

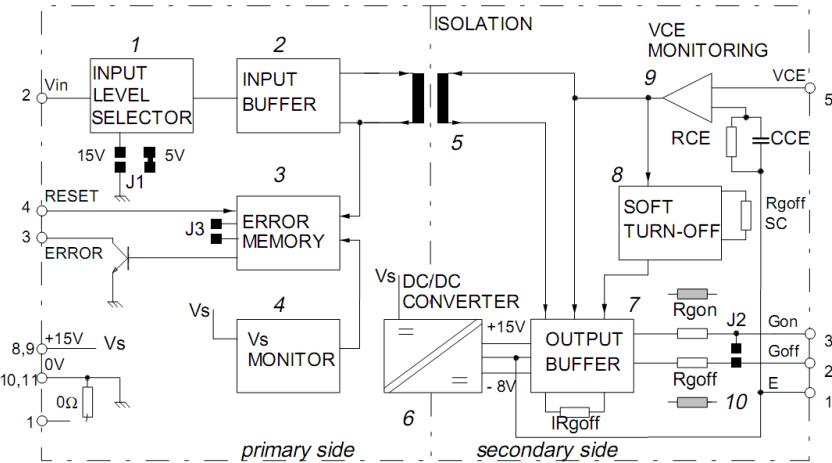

| 5.5 Diagrama de blocos do <i>gate-driver</i> SKHI 10-12 da Semikron® ...                                                                     | 108 |

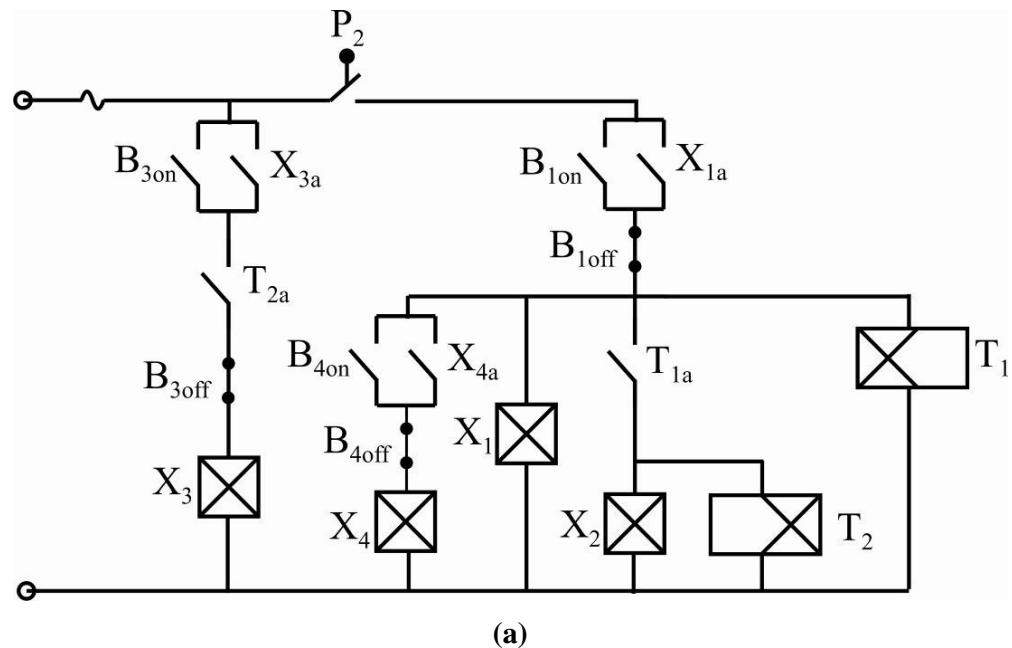

| 5.6 Circuito de potência do RHM com contatores.....                                                                                          | 109 |

| 5.7 (a) Circuito de controle e (b) gráficos de acionamento.....                                                                              | 110 |

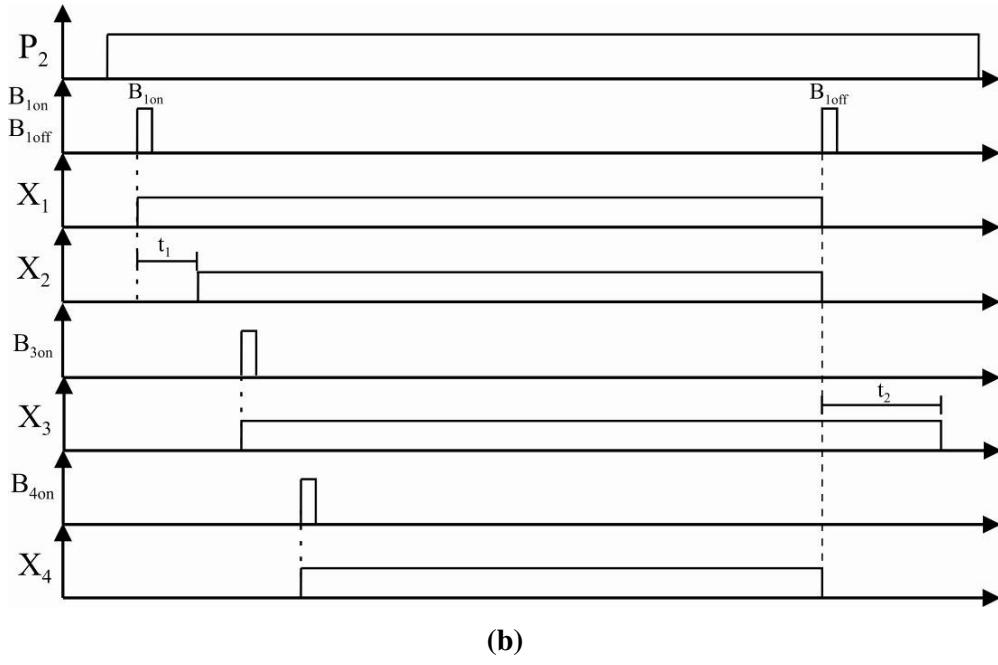

| 5.8 Protótipo de 1 kW no Solid Works.....                                                                                                    | 112 |

| 5.9 Interfaces do programa desenvolvido para especificação do<br>Protótipo de 1 kW.....                                                      | 117 |

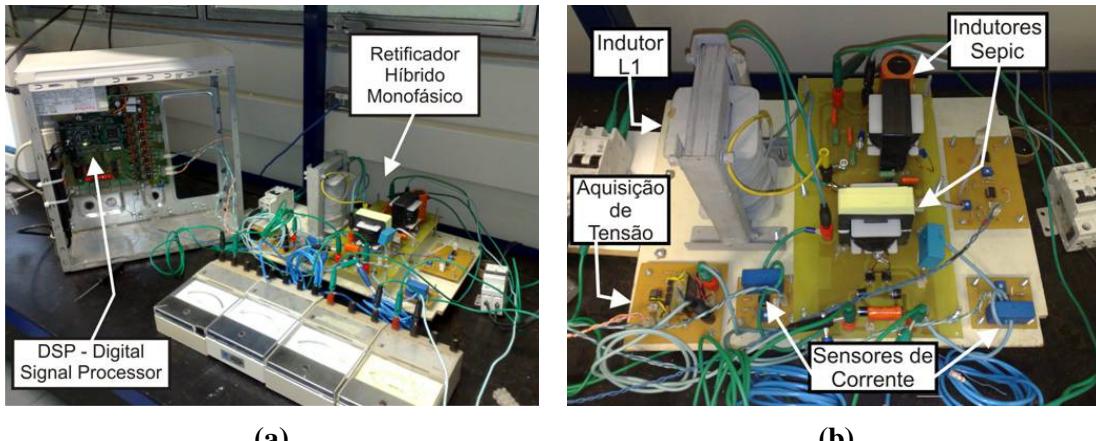

| 5.10 (a)Visão geral e (b) detalhes do protótipo de 1 kW.....                                                                                 | 117 |

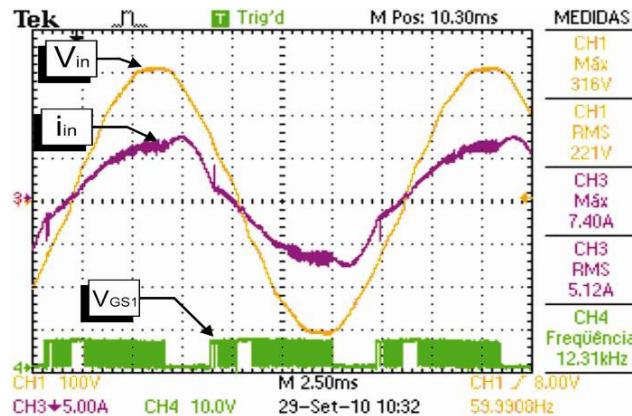

| 5.11 Tensão ( $V_{in}$ ), corrente CA de entrada (iin) e pulsos de ataque de                                                                 |     |

|                                                                                                                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| gate do interruptor S1 ( $V_{GS1}$ ).....                                                                                                                                                                                            | 118 |

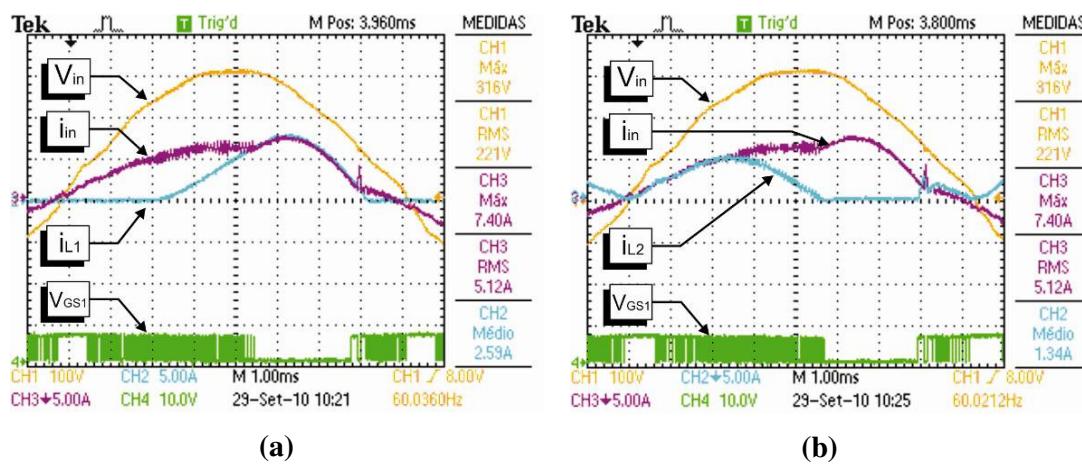

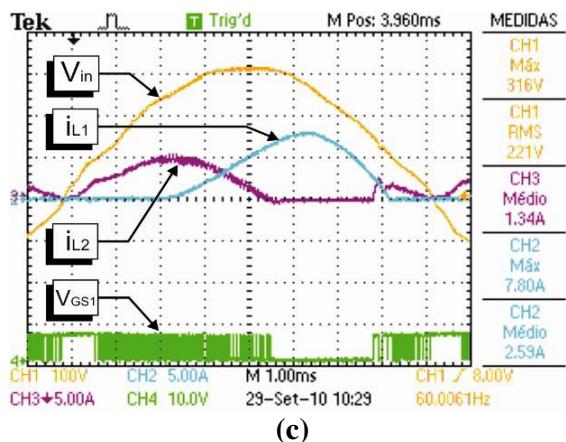

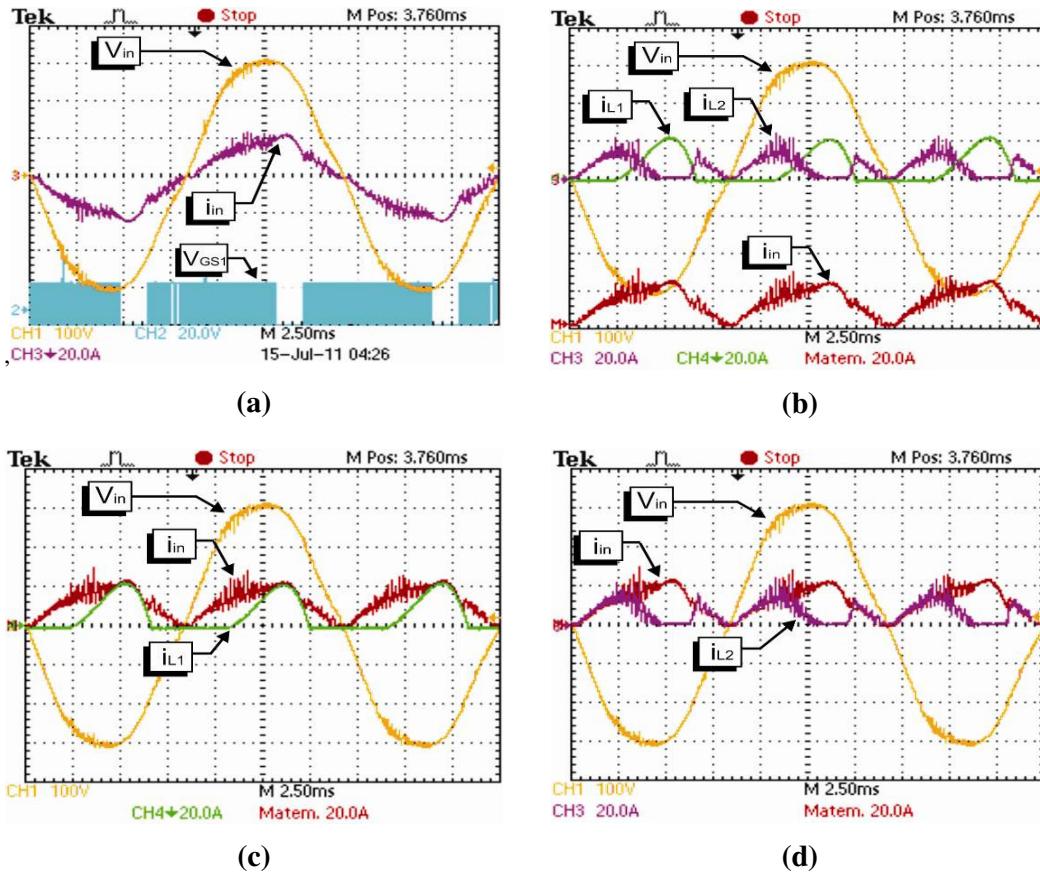

| 5.12 Tensão ( $V_{in}$ ) e corrente ( $i_{in}$ ) de entrada e (a) corrente $i_{L1}$ , (b) corrente $i_{L2}$ e (c) corrente $i_{L1}$ e $i_{L2}$ .....                                                                                 | 119 |

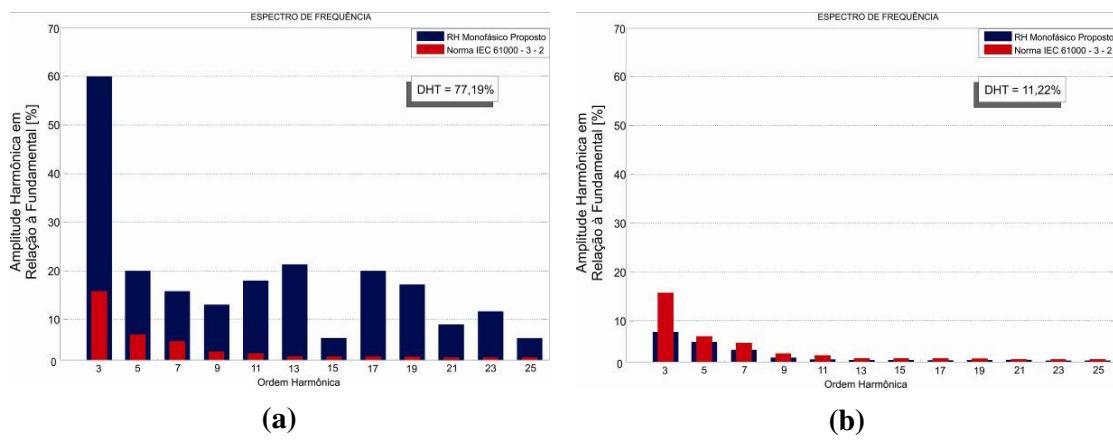

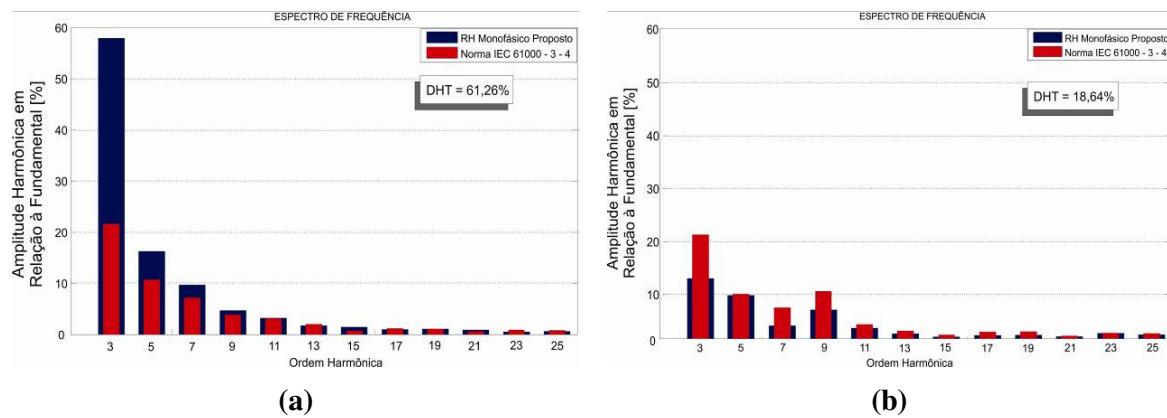

| 5.13 Decomposição harmônica da corrente CA de entrada estando ativo<br>(a) somente o Ret-1 e (b) ambos os retificadores (Ret-1 e Ret-2). 119                                                                                         |     |

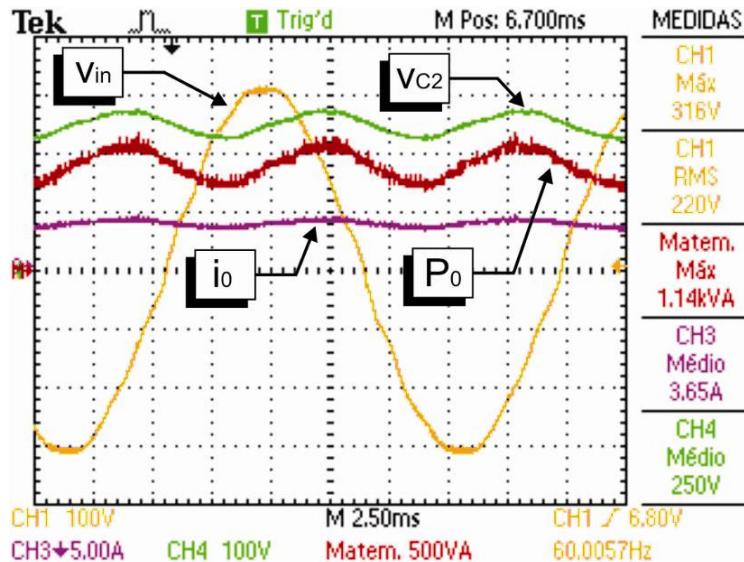

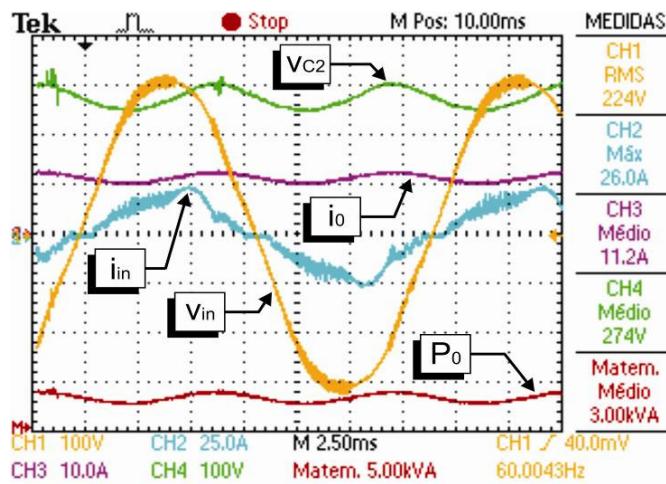

| 5.14 Tensão de entrada ( $V_{in}$ ) e saída ( $V_o$ ), corrente ( $i_o$ ) e potência ( $P_o$ ) de saída.....                                                                                                                         | 120 |

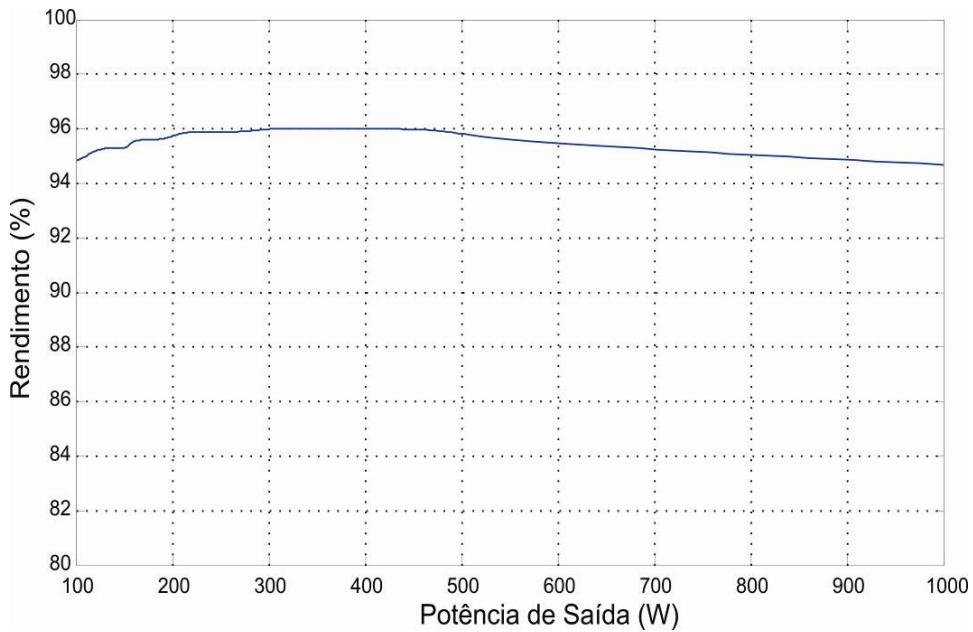

| 5.15 Curva de rendimento.....                                                                                                                                                                                                        | 121 |

| 5.16 Interfaces do <i>software</i> desenvolvido para o protótipo de 10 kW com resultados para uma potência de saída de 3 kW.....                                                                                                     | 126 |

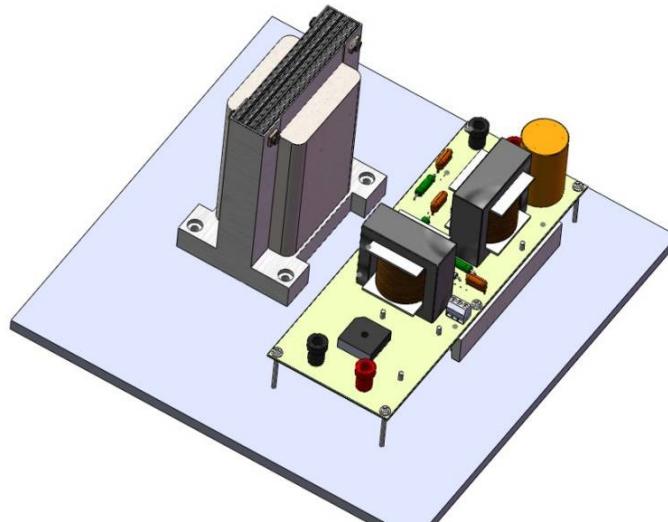

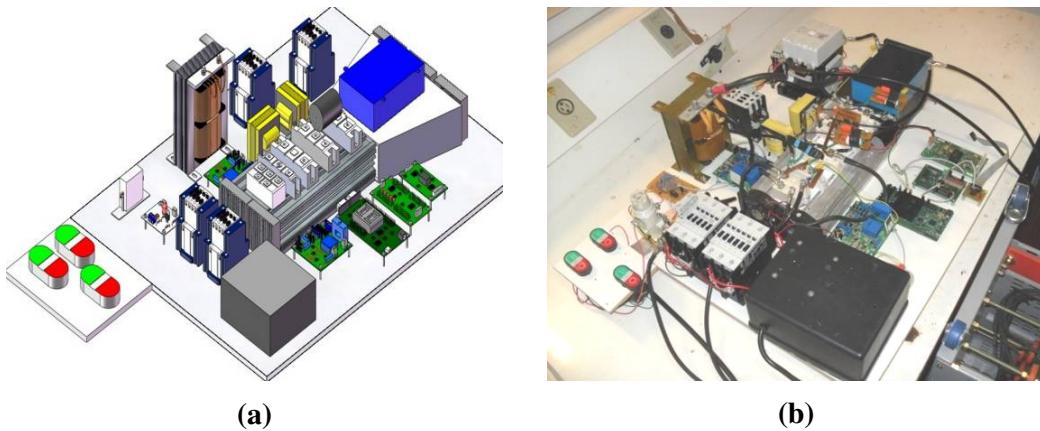

| 5.17 (a) Modelo tridimensional e (b) foto do protótipo de 10 kW....                                                                                                                                                                  | 126 |

| 5.18 Tensão e corrente de entrada ( $V_{in}$ e $i_{in}$ ) e saída ( $V_o$ e $i_o$ ) e potência de saída ( $P_o$ ).....                                                                                                               | 128 |

| 5.19 Tensão de entrada ( $V_{in}$ ) e (a) corrente $i_{L1}$ , (b) corrente $i_{L2}$ ,<br>(c) corrente $i_{L1}$ e $i_{L2}$ compondo a corrente de entrada $i_{in}$ e (d) corrente $i_{in}$ e pulsos de ataque de gate $V_{GS1}$ ..... | 128 |

| 5.20 DHT de corrente CA de entrada quando ativo (a) somente o Ret-1 e<br>(b) ambos os grupos de retificadores (Ret-1 e Ret-2).....                                                                                                   | 129 |

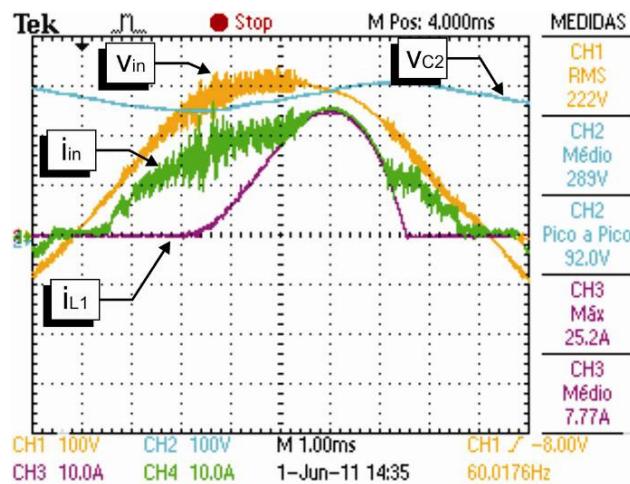

| 5.21 Tensão ( $V_{in}$ ) e corrente ( $i_{in}$ ) de entrada, corrente no indutor $L_1$ ( $i_{L1}$ ) e tensão de saída ( $V_o$ ).....                                                                                                 | 130 |

| 5.22 (a) Tensão, (b) corrente e (c) detalhe da comutação no interruptor $S_1$ ..                                                                                                                                                     | 130 |

| 5.23 Resposta dinâmica do retificador híbrido monofásico proposto...                                                                                                                                                                 | 131 |

# **Lista de Tabelas**

|     |                                                                     |     |

|-----|---------------------------------------------------------------------|-----|

| 2.1 | Resumo dos conversores básicos operando como PFC.....               | 26  |

| 3.1 | Especificação de projeto do retificador não controlado (Ret-1)..... | 45  |

| 3.2 | Especificações do Conversor SEPIC.....                              | 48  |

| 3.3 | Resumo de dimensionamento.....                                      | 50  |

| 3.4 | Variáveis utilizadas na estratégia de controle digital.....         | 60  |

| 3.5 | Informações dos sinais e pinos do ADC .....                         | 66  |

| 5.1 | Parâmetros do protótipo 1 kW – Retificador híbrido monofásico.      | 113 |

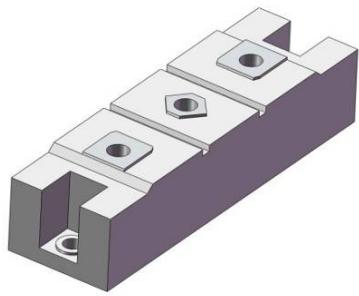

| 5.2 | Ponte Retificadora TB3505.....                                      | 113 |

| 5.3 | Diodos D8/D9 - APT15D100K.....                                      | 114 |

| 5.4 | IGBT S <sub>1</sub> - IRGPC40S.....                                 | 114 |

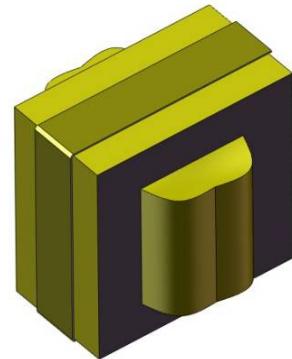

| 5.5 | Indutor L <sub>1</sub> .....                                        | 114 |

| 5.6 | Indutor L <sub>2</sub> /L <sub>3</sub> .....                        | 115 |

| 5.7 | Capacitor C <sub>1</sub> .....                                      | 115 |

| 5.8 | Capacitor C <sub>2</sub> .....                                      | 115 |

|      |                                                                |     |

|------|----------------------------------------------------------------|-----|

| 5.9  | Parâmetros do protótipo 10 kW – Retificador híbrido monofásico | 122 |

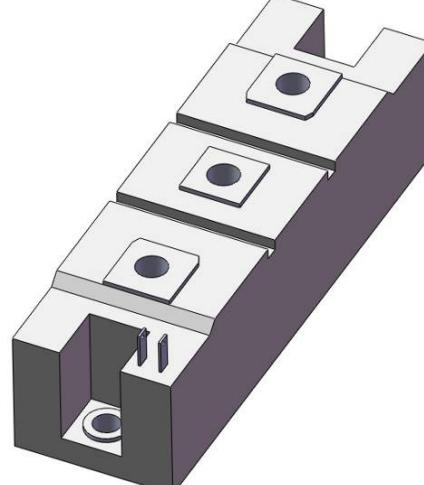

| 5.10 | Ponte Retificadora SKB 52/12.....                              | 122 |

| 5.11 | Diodos D <sub>8</sub> /D <sub>9</sub> 120F.....                | 122 |

| 5.12 | IGBT S <sub>1</sub> SKM 75GB123D.....                          | 123 |

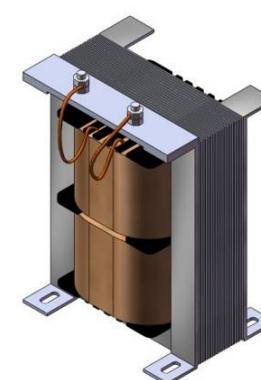

| 5.13 | Indutor L <sub>1</sub> .....                                   | 123 |

| 5.14 | Indutor L <sub>2</sub> /L <sub>3</sub> .....                   | 124 |

| 5.15 | Capacitor C <sub>1</sub> .....                                 | 124 |

| 5.16 | Capacitor C <sub>2</sub> B25655.....                           | 124 |

# Simbologia

|                     |                                                                           |

|---------------------|---------------------------------------------------------------------------|

| ADC                 | - <i>Analogic – Digital Converter</i>                                     |

| C <sub>1</sub>      | - Capacitor do conversor SEPIC                                            |

| C <sub>2</sub>      | - Capacitor de filtro de saída                                            |

| CA                  | - Corrente alternada                                                      |

| CC                  | - Corrente contínua                                                       |

| D                   | - razão cíclica                                                           |

| D <sub>min</sub>    | - razão cíclica mínima                                                    |

| D <sub>max</sub>    | - razão cíclica máxima                                                    |

| D <sub>1-4</sub>    | - Diodos da ponte retificadora                                            |

| D <sub>5-6</sub>    | - Diodos do conversor SEPIC                                               |

| DHT                 | - Distorção Harmônica Total                                               |

| DSP                 | - <i>Digital Signal Processor</i>                                         |

| ΔI <sub>L2</sub>    | - <i>Ripple</i> de corrente no indutor L <sub>2</sub>                     |

| ΔI <sub>L3</sub>    | - <i>Ripple</i> de corrente no indutor L <sub>3</sub>                     |

| ΔV <sub>C1</sub>    | - <i>Ripple</i> de tensão no indutor C <sub>1</sub>                       |

| ΔV <sub>C2</sub>    | - <i>Ripple</i> de tensão no indutor C <sub>2</sub>                       |

| FP                  | - Fator de potência.                                                      |

| f <sub>s</sub>      | - Freqüência de chaveamento                                               |

| GPIO                | - <i>General Purpose In-Out</i>                                           |

| K <sub>1</sub>      | - Constante                                                               |

| IEC                 | - <i>International Electrotechnical Commission</i>                        |

| i                   | - Contador geral                                                          |

| i <sub>L1</sub>     | - Corrente no indutor L <sub>1</sub> do retificador não controlado.       |

| i <sub>L1avg</sub>  | - Corrente média no indutor L <sub>1</sub> do retificador não controlado. |

| i <sub>L2</sub>     | - Corrente no indutor L <sub>2</sub> do conversor SEPIC                   |

| i <sub>in</sub>     | - Corrente AC de entrada                                                  |

| i <sub>realim</sub> | - Corrente realimentada                                                   |

| I <sub>o</sub>      | - Corrente média de saída                                                 |

| L <sub>1</sub>      | - Indutor de filtro do retificador não controlado                         |

| L <sub>2</sub>      | - Indutor do conversor SEPIC 2                                            |

| L <sub>3</sub>      | - Indutor do conversor SEPIC 2                                            |

| P <sub>0</sub>      | - Potência média de saída                                                 |

| P <sub>1</sub>      | - Sinal de proteção do interruptor                                        |

| P <sub>2</sub>      | - Sinal de proteção dos contatores                                        |

| P <sub>Ret-1</sub>  | - Potência média processada pelo retificador não controlado               |

| P <sub>Ret-2</sub>  | - Potência média processada pelo conversor chaveado                       |

| PWM                 | - <i>Pulse Width Modulation</i>                                           |

| Ret-1               | - Retificador não controlado                                              |

| Ret-2               | - Conversor chaveado (SEPIC)                                              |

| R <sub>L</sub>      | - Resistência de carga                                                    |

| R <sub>PC</sub>     | - Resistência de pré-carga                                                |

| S <sub>1</sub>      | - Interruptor do conversor SEPIC                                          |

| T                   | - Período de chaveamento                                                  |

| T <sub>1</sub>      | - Temporizador com retardo na energização                                 |

- $T_2$  - Temporizador com retardo na desenergização

$T_{BPRD}$  - Período do Timer Base

$T_{emp}$  - Temperatura no dissipador de calor

$V_0$  - Tensão de saída

$V_{C1md}$  - Tensão média no capacitor  $C_1$  do SEPIC

$V_{in}$  - Tensão eficaz de entrada

$V_{imax}$  - Tensão máxima de entrada

$V_{imin}$  - Tensão mínima de entrada

$V_p$  - Valor de pico da tensão de entrada

$V_{ref}$  - Tensão senoidal digital

$V_{ref-2}$  - Tensão senoidal de referência proporcional à carga

$V_{st}$  - Amplitude da onda dente-de-serra.

# **Capítulo 1**

## **Introdução**

### **1.1 Introdução Geral**

Devido à notável evolução da eletrônica de potência e, consequentemente, a viabilização de novos dispositivos mais flexíveis, compactos e eficientes, nota-se que é cada vez maior o número de cargas elétricas que utilizam algum tipo de conversor eletrônico de potência. Estima-se que aproximadamente 50% da energia elétrica gerada no Brasil seja processada eletronicamente antes de ser realmente utilizada.

A grande maioria desses equipamentos que processam energia eletronicamente possui um conversor CA-CC (retificadores ou conversores CA-CC), obtendo-se, dessa forma, um barramento de tensão contínua na saída que alimenta a carga. A utilização desses conversores CA-CC trazem como benefício melhorias significativas na operação e no rendimento dos equipamentos. Todavia, na condição de cargas não lineares, esses conversores injetam correntes não senoidais pela rede CA de alimentação [1].

Dentre os problemas causados pelos componentes harmônicos na rede CA de alimentação podem-se destacar [1]-[3]:

- Aquecimento em máquinas elétricas e capacitores;

- Mau funcionamento de disjuntores termomagnéticos;

- Aumento na corrente de neutro;

- Perda em condutores;

- Erro em equipamentos convencionais de medição.

Destaca-se que, além dos problemas citados, a inserção de conteúdos harmônicos devido ao elevado número de equipamentos com reduzido fator de potência conectados na rede de distribuição em CA causam uma redução global da eficiência do sistema, resultando em perdas desde a geração até a distribuição de energia.

Diante desse quadro, inúmeras pesquisas vêm sendo realizadas no intuito de diagnosticar e resolver os problemas causados pela distorção harmônica e o redução do fator de potência no sistema elétrico [4] - [6].

Neste sentido, como proposta de reduzir a distorção harmônica de corrente ( $DHT_I$ ) devido à presença de cargas não lineares, realizar a correção do fator de potência e a busca por redução de custos, alto rendimento e confiabilidade operacional, este trabalho propõe um novo estágio pré-regulador composto por um retificador híbrido monofásico de alta potência e elevado FP.

O Retificador Híbrido Monofásico (RHM) proposto é composto por um retificador monofásico não controlado (Ret-1), associado em paralelo com um conversor monofásico chaveado (Ret-2). Destaca-se que as principais vantagens de se utilizar retificadores híbridos como estágio pré-regulador com correção do fator de potência para conexão de conversores eletrônicos são:

- Maior rendimento global da estrutura, uma vez que os conversores chaveados processam reduzida parcela de potência ativa entregue à carga;

- Menor custo, quando comparado com conversores pré-reguladores chaveados convencionais com FP unitário, uma vez que os dispositivos semicondutores utilizados nessas estruturas são dimensionados para potência nominal;

- Flexibilidade quanto ao atendimento às restrições impostas pela normas IEC610003-2 e IEC610003-4, uma vez que a corrente a ser imposta na

rede CA de alimentação pode assumir diferentes formas, dependendo da DHT<sub>I</sub> desejada;

- Técnica de controle simples, de baixo custo e eficiente.

A grande vantagem proporcionada por retificadores híbridos, trifásicos ou monofásicos, é a associação da robustez, confiabilidade e simplicidade dos retificadores não controlados a diodos com a redução de peso e volume proporcionados pelos conversores chaveados, que operam em alta freqüência de chaveamento. Desta forma, a potência nominal da estrutura híbrida pode ser drasticamente aumentada, sem prejudicar a eficiência global do retificador, o que não pode ser alcançado com retificadores PWM convencionais, sem aumentar consideravelmente os custos [2], [7]-[10].

## 1.2 Considerações Iniciais

Os objetivos deste trabalho envolvem a análise, o desenvolvimento e implementação de um novo retificador híbrido monofásico com características de elevado fator de potência e reduzida distorção harmônica da corrente CA de entrada para operação em aplicações de elevados níveis de potência.

Para demonstrar a viabilidade técnica e econômica do RHM proposto, construiu-se no Núcleo de Pesquisa em Eletrônica de Potência (NUPEP) dois protótipos a fim de verificar o comportamento do conjunto operando em baixas potências (1 kW) e em potências mais elevadas (10 kW).

Destaca-se que o controle digital utilizado, baseado em DSP, constitui uma inovação tecnológica no desenvolvimento de equipamentos, permitindo uma grande versatilidade na implementação de técnicas de controle digital aplicadas em eletrônica de potência.

Os trabalhos publicados durante a pesquisa [11] - [16] introduzem importantes e inovadores conhecimentos tecnológicos para a comunidade científica, contribuindo, portanto, com o desenvolvimento da pesquisa em Eletrônica de Potência.

## **1.3 Estrutura da Dissertação**

Este trabalho está dividido em 6 capítulos, incluindo este capítulo introdutório.

### **1.3.1 – Capítulo 2**

No capítulo 2 serão apresentadas as topologias tradicionalmente utilizadas para mitigação de harmônicos em sistemas monofásicos, fornecendo, dessa forma, informações suficientes para comparação da estrutura proposta com aquelas encontradas na literatura.

### **1.3.2 – Capítulo 3**

Neste capítulo será apresentando o retificador híbrido monofásico proposto, com detalhes de sua operação, projeto e da estratégia de controle adotada. São apresentados também a metodologia para o dimensionamento dos componentes do circuito de potência de cada protótipo construído, além de detalhes da implementação das leis de controle digital baseado em DSP.

### **1.3.3 – Capítulo 4**

O capítulo 4 é destinado ao desenvolvimento da modelagem matemática do retificador híbrido monofásico proposto. A modelagem matemática é baseada no método por espaço de estados e a solução do modelo tem como objetivo o cálculo dos valores eficazes, médio e pico de tensão e corrente em todos os elementos do circuito de potência, possibilitando sua completa especificação. Além disso, é possível determinar

parâmetros do controle digital com base em um DHT desejado para a corrente CA de entrada, fornecido através de uma interface gráfica desenvolvida no *software Matlab*<sup>®</sup>.

Como método de validação do modelo proposto, as formas de onda resultantes da sua solução foram comparadas com as formas de onda obtidas através da simulação do retificador híbrido monofásico no Orcad<sup>®</sup> para uma mesma condição de carga e mesmo DHT da corrente CA de entrada. Os resultados alcançados comprovam a eficácia da modelagem realizada.

#### **1.3.4 – Capítulo 5**

No capítulo 5 são apresentados os resultados experimentais para os protótipos construídos e ensaiados com base nas leis de controle descritas no Capítulo 3. O objetivo é avaliar o comportamento e o desempenho da estrutura mitigando harmônicos da corrente CA de entrada e elevando o fator de potência do conjunto.

Foram realizados exaustivos testes em situações extremas de funcionamento dos protótipos, verificando a eficiência da estrutura e a eficácia dos dispositivos de proteção configurados para manter a integridade do conjunto.

#### **1.3.5 – Conclusões**

Conclusões gerais do trabalho.

#### **1.3.6 – Apêndices**

Programas desenvolvidos no *software Matlab*<sup>®</sup>.

# **Capítulo 2**

## **Estado da Arte**

### **2.1 Introdução Geral**

Neste capítulo serão descritas resumidamente as topologias de conversores CA-CC encontradas na literatura tradicionalmente utilizadas para correção ativa do fator de potência e para mitigação de componentes harmônicos na corrente de alimentação de sistemas monofásicos. Essa abordagem é oportuna por reunir informações a respeito do tema, servindo como parâmetro de comparação para a estrutura topológica apresentada neste trabalho.

### **2.2 Conversores CC-CC Básicos**

De acordo com as informações apresentadas em [17]-[20] a respeito dos conversores nas suas topologias básicas conclui-se que os conversores boost, flyback e buck-boost apresentam os melhores desempenhos operando como estágio pré-regulador. A conclusão pode ser estendida para a mitigação de harmônicos, visto as formas de onda de corrente de entrada dos conversores citados apresentarem a menor distorção.

Os outros conversores podem ser utilizados para correção ativa de fator de potência e mitigação de harmônicos, desde que sejam modificados para apresentarem uma curva característica de entrada V – I linearizada ou desde que operem em modo de condução contínuo (MCC).

As características a respeito dos conversores básicos operando como estágio pré-regulador com elevado fator de potência ou simplesmente Conversores PFC – *Power Factor Corrector* podem ser resumidas na Tab. 2.1 [17].

**Tab. 2.1 – Resumo dos conversores básicos operando como PFC.**

| Conversor Básico       | Forma de onda da corrente de entrada | Avaliação | Nível de Potência |

|------------------------|--------------------------------------|-----------|-------------------|

| Buck                   |                                      | Ruim      | Baixo a médio     |

| Boost                  |                                      | Bom       | Baixo a médio     |

| Buck-Boost             |                                      | Excelente | Baixo a médio     |

| Flyback                |                                      | Excelente | Baixo             |

| Forward                | -                                    | -         | -                 |

| Cuk,<br>Sepic,<br>Zeta |                                      | Ruim      | Baixo a médio     |

As formas de onda e as avaliações apresentadas na Tab. 2.1 são relativas aos conversores básicos operando como estágio PFC. O grau de distorção da forma de onda da corrente de entrada foi tomado como critério de avaliação de desempenho dos conversores. Assim, apesar de apresentar uma forma de onda aproximadamente senoidal, os conversores PFC básicos tradicionalmente utilizados para este fim são os

conversores Flyback e Boost, os quais são adequados para aplicações de baixa potência (centenas de watts) e média potência (até algumas unidades de kilowatts), respectivamente. Cabe ressaltar que os referidos conversores apresentando queda de rendimento em aplicações de potências mais elevadas, limitando, dessa forma, sua utilização.

Com vistas a superar essa desvantagem, ou seja, limitação de potência em aplicações monofásicas, é apresentado neste trabalho uma nova concepção de conversor PFC capaz de processar altas potências (dezenas de kW) mantendo elevada eficiência sem comprometer a robustez da estrutura. O conversor proposto recebe a denominação de Retificador Híbrido Monofásico por se tratar de uma estrutura topológica composta de um retificador não controlado operando em paralelo com um conversor chaveado (conversor CC-CC), resultando em uma estrutura que apresenta características de elevado fator de potência e reduzida distorção harmônica da corrente de alimentação. Quando comparado com as topologias PFC tradicionais, o retificador híbrido monofásico desenvolvido neste trabalho apresenta como vantagem o fato de o conversor chaveado processar apenas uma parcela de potência ativa total entregue à carga, sendo a maior parte processada pelo retificador não controlado, possibilitando, portanto, que o conjunto processe níveis mais elevados de potência (dezenas de kilowatts), promovendo maiores robustez e densidade de potência e elevada eficiência.

Nesse contexto, foram pesquisados outros trabalhos na literatura com o objetivo de encontrar estruturas que operam com elevado fator de potência e reduzido DHT<sub>I</sub> adequado para operação em sistemas monofásicos de alta potência (dezenas de kilowatts). Dessa forma, constatou-se que a maioria dos estudos realizados até o presente momento se baseiam na implementação de modificações topológicas em estruturas básicas e em novos arranjos topológicos baseados no paralelismo de

conversores chaveados tradicionais, resultando em novas topologias com características total ou parcialmente diferentes daquelas de origem.

Neste contexto, a seguir são apresentados os principais trabalhos encontrados na literatura com o intuito de promover um estudo comparativo entre as soluções encontradas e Retificador Híbrido Monofásico apresentado nesta dissertação, objetivando evidenciar suas principais vantagens e desvantagens para aplicação como estágio pré-regulador com elevado fator de potência.

## **2.3 Topologias Modificadas de Conversores PFC**

Nesta seção serão apresentadas as topologias modificadas que foram encontradas na literatura, que operam ativamente na mitigação de conteúdos harmônicos e na correção do fator de potência.

### **2.3.1 Conversor Boost Modificado**

O conversor boost operando em modo contínuo (MCC) é tradicionalmente utilizado para correção de fator de potência e mitigação de componentes harmônicos da corrente de alimentação de equipamentos de média a alta potência (400 W até poucos kilowatts). Operando em modo contínuo de condução, a corrente de entrada do conversor proporciona reduzida interferência eletromagnética (EMI), quando comparado a outros conversores PFC, como buck e o buck-boost.

São encontrados na literatura muitos trabalhos com o objetivo de determinar qual tipo de conversor é o mais adequado para determinadas aplicações, levando-se em consideração robustez, densidade de potência, eficiência, custo e complexidade [21]. Nesse contexto, varias topologias de conversores boost PFC modificados foram pesquisados com o objetivo de melhorar as características do conversor boost tradicional utilizado como PFC, como por exemplo o problema de recuperação reversa

do diodo, que afeta o interruptor principal, [22], [23] e a elevada tensão de saída [24]. Esses esforços se justificam pela necessidade de se reduzir o conteúdo harmônico da corrente de entrada, os níveis de EMI, o peso e o volume do conjunto, aumentar a robustez e o rendimento da estrutura possibilitando, dessa forma, elevar os níveis de potência de operação do conversor.

### 2.3.1.1 Conversor Boost CA-CC *Bridgeless*

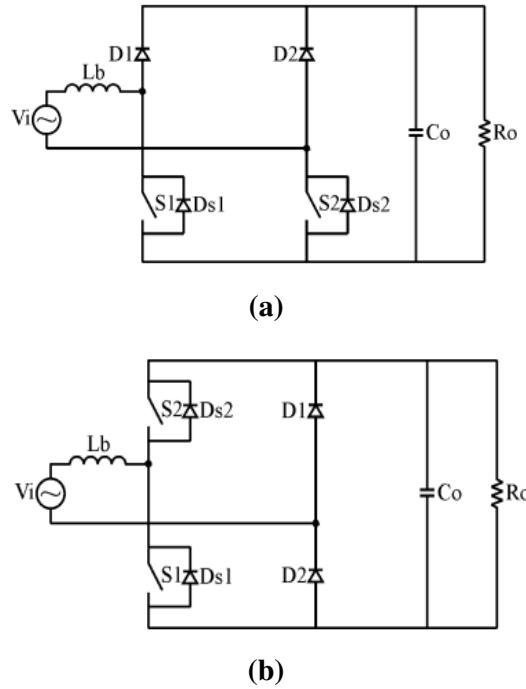

Para aumentar o rendimento do conversor boost tradicional foi desenvolvido o conversor boost bridgeless, ilustrado na Fig. 2.1 [25], [26].

**Fig. 2.1 – Conversor boost *bridgeless* (a) simétrico e (b) assimétrico.**

Por reduzir o número de componentes, as perdas de condução são reduzidas, elevando, nesse aspecto, o rendimento da estrutura. Entretanto, os diodos de saída quando polarizados reversamente ficam submetidos a uma tensão elevada e assim apresentam problemas graves de corrente de recuperação reversa. Essas elevadas correntes de recuperação reversa aumentam as perdas de comutação nos interruptores e

produzem interferência eletromagnética (EMI). Além disso, por utilizar dois interruptores ( $S_1$  e  $S_2$ ) a complexidade e o custo do projeto se elevam.

Concluindo, quando comparado com o conversor boost tradicional, o conversor boost *bridgeless* tem como vantagem a minimização das perdas de condução, mas apresenta, como desvantagem, um maior custo e complexidade de projeto.

A referência [27] apresenta uma alteração topológica no conversor apresentado na Fig. 2.1(a), incluindo-se um par de indutores acoplados e dois diodos adicionais, como método alternativo para minimização das desvantagens citadas. Dessa forma, reduz-se a corrente de recuperação reversa e os transitórios de chaveamento são melhorados.

### 2.3.1.2 Conversor Boost CA-CC com Três Níveis.

O conversor boost com três níveis é apresentado na Fig. 2.2.

**Fig. 2.2 – Conversor boost com três níveis.**

Esta topologia é adequada para aplicações com potências mais elevadas (alguns kilowatts). Por utilizar dois interruptores ( $S_1$  e  $S_2$ ), que devem ser projetados para metade da tensão de saída, pode-se elevar a tensão de operação. Do ponto de vista prático, esta topologia é adequada para aplicações onde a tensão de saída gira em torno de 400 V e a potência de saída é de alguns kilowatts [21].

Um importante aspecto a ser investigado nessa topologia é o tamanho do indutor pois, para uma mesma tensão de operação e mesma potência de saída, e consequentemente para um mesmo *ripple* de corrente, necessita-se de um indutor quatro

vezes menor, resultando em uma frequência de ripple duas vezes maior, que aquele requerido no conversor boost tradicional [28]. Um indutor menor requer menos material magnético e uma maior frequência de ripple de corrente tem impacto no filtro entrada, reduzindo-o [28].

Assim, conclui-se que o conversor boost PFC com três níveis é melhor que o conversor boost PFC tradicional, levando-se em consideração o rendimento e o volume da estrutura. Por outro lado, para contornar os empecilhos da estrutura do conversor boost tradicional, que limita o nível de potência do conversor, utiliza-se um número maior de componentes, elevando o custo e a complexidade do conjunto.

### 2.3.1.3 Conversor Boost com Célula de Chaveamento com Três Estados.

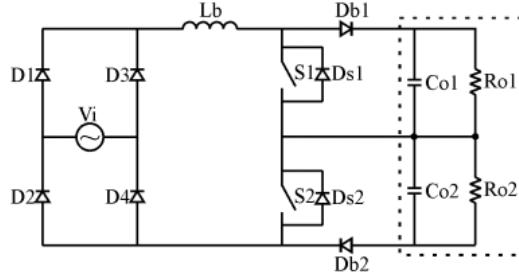

A referência [29] apresenta uma nova família de conversores CC-CC com uma célula de chaveamento com três estados, destacando como vantagens a alta eficiência, o pequeno *ripple* de corrente de entrada e reduzidos peso e volume do conjunto. A Fig. 2.3 ilustra o conversor com célula de comutação com três estados.

**Fig. 2.3 – Conversor boost PFC com célula de chaveamento com 3 estados .**

De acordo com a estratégia de controle apresentado em [29], parte da potência transferida para a carga é realizada através de um autotransformador, não havendo, nessa condição, circulação de corrente através dos interruptores  $S_1$  e  $S_2$ . Dessa forma, o conversor proposto é capaz de operar em níveis mais elevados de potência, uma vez que o autotransformador é responsável por processar uma parcela de potência entregue a carga.

Através dos resultados experimentais apresentados em [29] nota-se uma redução sensível da DHT da corrente de entrada e um elevado fator de potência, alcançados com os interruptores processando 60% da corrente de carga, sendo o restante processado pelo autotransformador.

### 2.3.2 Conversor SEPIC Modificado

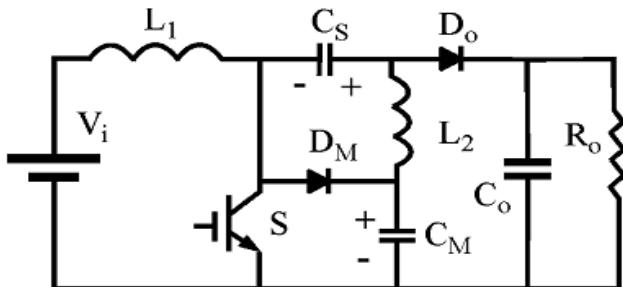

O desempenho do conversor SEPIC clássico é atrativo por ser um conversor tanto abaixador quanto elevador, tornando-se adequado para aplicações onde a tensão de saída é maior ou menor que a tensão de entrada. Entretanto, essa topologia apresenta o inconveniente da tensão no interruptor ser a soma da tensão da entrada com a tensão de saída. Nesse contexto, a referência [30] apresenta uma adaptação na topologia clássica do SEPIC, ilustrada na Fig. 2.4, incluindo o diodo  $D_M$  e o capacitor  $C_M$  na topologia básica, com o intuito de reduzir a tensão sobre o interruptor  $S$ .

**Fig. 2.4 – Conversor SEPIC modificado.**

Analisando o circuito da Fig. 2.4 percebe-se que o conversor SEPIC modificado apresenta, como desvantagem, a perda da característica de abaixador-elevador presente no conversor SEPIC básico. Dessa forma, apesar de reduzir os níveis de tensão no interruptor S, possibilitando aumentar a tensão de operação para elevar o nível de potência de saída, o conversor SEPIC modificado apresentado em [30] não pode operar em aplicações onde a tensão de saída é menor que a tensão de entrada.

### 2.3.3 Conversor Buck Modificado

O circuito do conversor buck modificado apresentado em [31] é ilustrado na Fig. 2.5. A diferença do conversor proposto em relação ao conversor buck tradicional é a inclusão de capacitores eletrolíticos ( $C_{1-4}$ ) conectados em paralelo com os diodos da ponte retificadora ( $D_{1-4}$ ). Com essa configuração, o circuito de entrada fica sempre conectado a um terminal do link DC, tornando a forma de onda da corrente de entrada mais próxima de uma senóide.

De acordo com os resultados apresentados em [31], observa-se um fator de potência próximo da unidade e uma redução sensível da DHT da corrente de entrada quando comparado com os resultados obtidos com conversor buck tradicional, sendo que tais melhorias são obtidas através de uma simples mudança topológica.

**Fig. 2.5 – Conversor Buck modificado.**

Contudo, percebe-se que os resultados são satisfatórios apenas quando o interruptor S é acionado através de pulsos com uma pequena razão cíclica (em torno de

10%), resultando em uma reduzida tensão de saída. Assim, a utilização do conversor buck modificado fica limitado a aplicações de baixa potência, visto que a tensão de saída ser necessariamente pequena para se obter uma corrente de entrada com reduzido conteúdo harmônico e elevado fator de potência.

## 2.4 Conversores PFC Operando em Paralelo

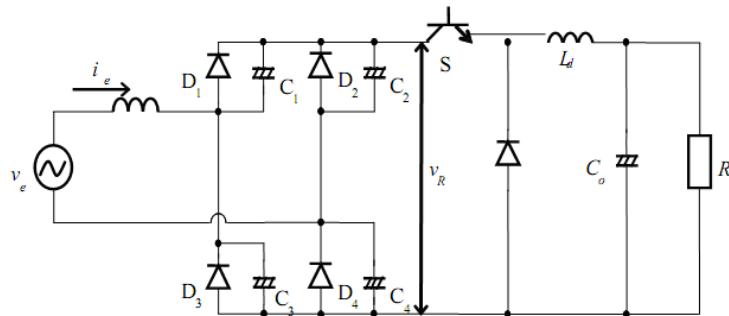

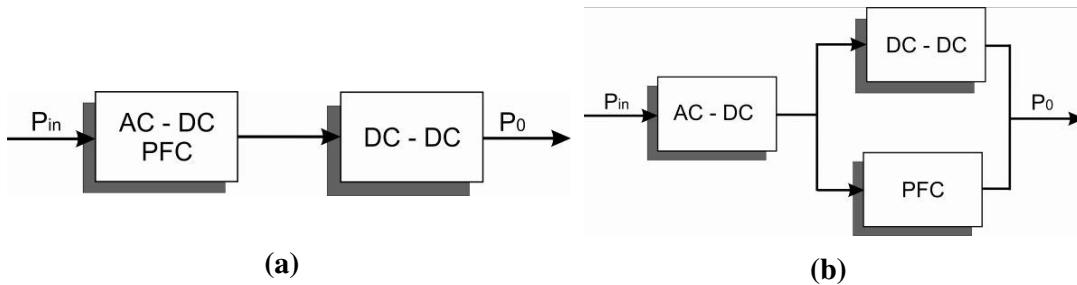

A Fig. 2.6 ilustra o diagrama básico dos métodos tradicionais utilizados para correção de fator de potência e mitigação de conteúdo harmônico.

**Fig. 2.6 – Fluxo de potência de conversores operando em modo (a) cascata e (b) paralelo.**

Para se obter uma boa regulação na tensão de saída e um *ripple* de corrente reduzido são utilizados dois conversores cascataados, sendo um estágio PFC seguido por um conversor DC-DC. Dessa forma, por utilizar dois estágios, a estrutura PFC ilustrada na Fig. 2.6 apresenta um baixo rendimento, visto a potência de saída ser processada por ambos os conversores [32]. Por outro lado, no modo em paralelo (Fig. 2.6(b)) a potência de saída é dividida entre o conversor DC-DC e o estágio PFC, o que contribui para um melhor rendimento do conjunto.

Nesse contexto, nas seções que seguem serão apresentadas estruturas que utilizam conversores operando em paralelo para fins de obtenção de elevado fator de potência e reduzida DHT<sub>I</sub>. Objetiva-se destacar que a associação em paralelo de conversores proporciona elevação do rendimento global da estrutura, uma vez que cada conversor

processa apenas uma parcela da potência total entregue à carga, elevando, dessa forma, o rendimento total da estrutura.

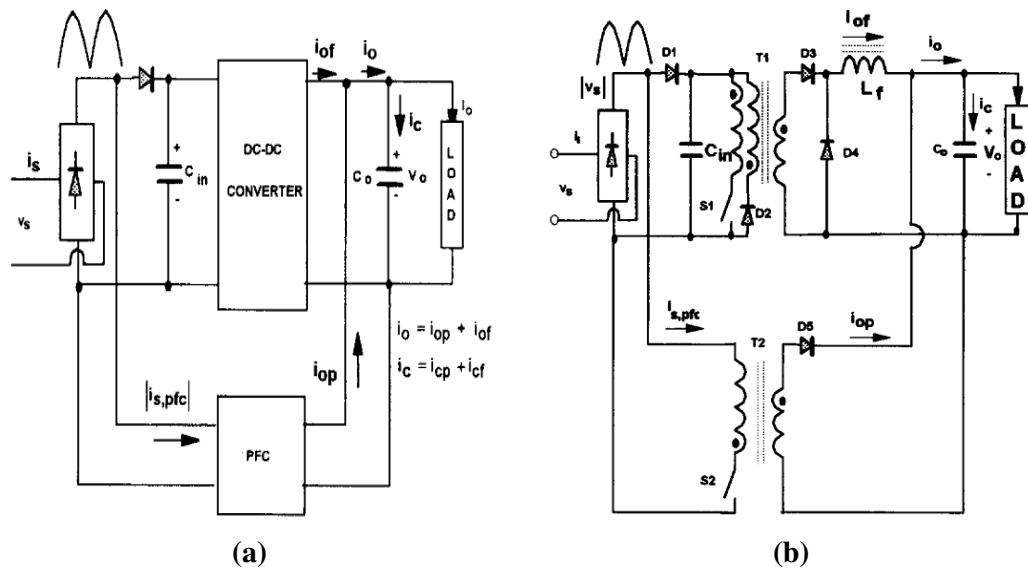

### 2.4.1 – Conversores Flyback e Forward Operando em Paralelo

A Fig. 2.7 ilustra a estrutura básica de conversores PFC operando em paralelo apresentado em [33].

É realizado o estudo da estrutura proposta utilizando-se os conversores Flyback e Forward, ilustrados na Fig. 2.7 (b), sendo que o conversor Flyback é diretamente responsável pela forma de onda de corrente CA de entrada. Nessa configuração, são desenvolvidos dois métodos de controle. Em um dos métodos há uma divisão igualitária de potência entre os conversores, ou seja, cada um processa 50% da potência total de saída. No outro método, o conversor Flyback processa 68% e o conversor Forward processa 32% da potência de saída.

**Fig. 2.7 – Conversores chaveados operando em paralelo.**

Analisando os resultados apresentados, observa-se que em ambos os métodos obteve-se uma redução da DHT<sub>I</sub> e um elevado fator de potência. No método de controle em que a parcela de contribuição de potência é de 68% e 32% para o conversor Flyback

e Forward, respectivamente, a redução da DHT<sub>I</sub> foi mais significativa. Porém, nesse método, a resposta dinâmica da estrutura apresentou pior desempenho.

A estrutura composta pelos conversores Flyback e Forward operando em paralelo apresenta um melhor rendimento que a estrutura tradicional composta por conversores cascateados. Todavia, de acordo com o apresentado em [33], conclui-se que a estrutura proposta é limitada a aplicações onde o nível de potência de saída gira em torno de 600W.

#### **2.4.2 – Retificador Híbrido Monofásico Proposto.**

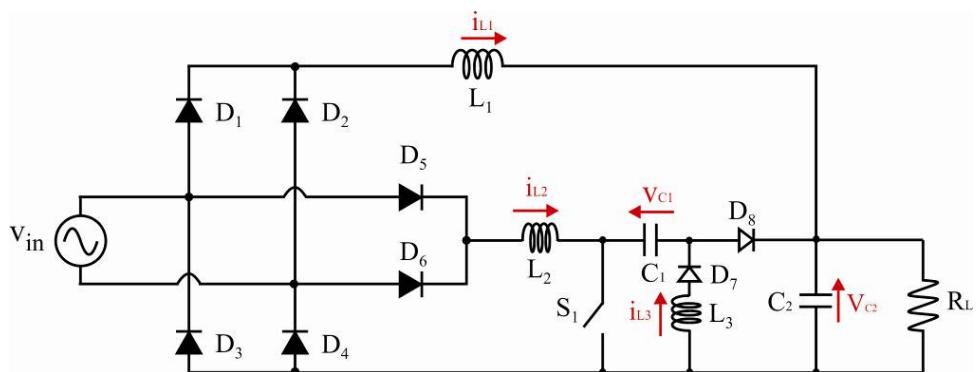

O arranjo topológico do Retificador Híbrido Monofásico (RHM) proposto é ilustrado na Fig. 2.8.

**Fig. 2.8 – Arranjo topológico do retificador híbrido monofásico**

O RHM desenvolvido consegue aliar a robustez e eficiência dos retificadores não controlados (Ret-1) com a capacidade que os conversores chaveados (Ret-2) têm de impor correntes CA de alimentação na forma de onda desejada.

Destaca-se que o conversor chaveado processa apenas parte da potência ativa entregue à carga, sendo a maior parcela de potência processada pelo retificador não controlado. Dessa forma, diferentemente das estruturas topológicas PFC apresentadas neste capítulo, que são limitadas à aplicações de baixa e média potência (até algumas unidades de kilowatts), o RHM proposto apresenta como vantagem a possibilidade de operar com níveis mais elevados de potência (dezenas de kilowatts) com capacidade de

compor a forma de onda da corrente CA de alimentação desejada com apenas uma fração de potência sendo processada pelo conversor chaveado. Trata-se, portanto, de uma estrutura compacta, de alta eficiência, com volume e peso reduzidos, capaz de impor corrente senoidal na rede CA de alimentação, adequada para aplicação em sistemas monofásicos de alta potência (dezenas de kilowatts) onde se deseja elevado fator de potência e reduzida distorção harmônica de corrente.

O conversor chaveado utilizado nesse projeto deve possuir característica de fonte de corrente de entrada, uma vez que sua função é compor a forma de onda da corrente de entrada do conjunto. Vale ressaltar que conversores Boost são tradicionalmente utilizados em sistemas PFC, tanto trifásicos como monofásicos. Porém, para compor o retificador híbrido proposto sua utilização é inviabilizada pelo fato de não haver o controle sobre a tensão de saída, conforme descrito detalhadamente no Capítulo 3.

Baseado nas conclusões apresentadas na Tab. 2.1 os conversores buck-boost e flyback são os indicados para compor o conversor chaveado. Todavia, o conversor buck-boost apresenta uma tensão de saída invertida em relação à tensão de entrada, o que inviabiliza sua operação em paralelo com o retificador não controlado (Ret-1). O conversor flyback, por ser inherentemente um conversor isolado, necessita de um transformador de acoplamento, elevando consideravelmente o peso, volume e custo da estrutura.

Diante do exposto, optou-se pelo conversor SEPIC para operar como conversor chaveado (Ret-2). O conversor SEPIC possui naturalmente característica de fonte de corrente de entrada, sendo capaz de operar impondo corrente segundo uma dada referência. Além disso, por possuir um capacitor série que força o decrescimento da corrente quando o interruptor é aberto, sua operação não depende do nível da tensão de saída, tornando-o apto a operar em todas as etapas de operação do RHM.

Apesar de o conversor SEPIC ser avaliado como ruim na Tab. 2.1, resultado da distorção na forma de onda da sua corrente entrada, ressalta-se que esta avaliação de desempenho considera o conversor atuando isoladamente na composição da corrente de entrada. Ao utilizá-lo em paralelo com o retificador não controlado (Ret-1) e, dessa forma, tornando-o responsável por drenar apenas uma parcela da corrente de entrada, a avaliação proposta na Tab. 2.1 não pode ser considerada.

## 2.5 Conclusão

Neste capítulo foram apresentadas diversas topologias tradicionalmente utilizadas para correção de fator de potência e mitigação de conteúdo harmônico. Foram analisadas as topologias PFC básicas, suas versões modificadas e o arranjo composto por conversores operando em paralelo, no qual está inserido o retificador híbrido proposto nesse trabalho.

Portanto, o objetivo deste capítulo foi apresentar uma revisão geral e apresentar o estado da arte sobre o tema, possibilitando uma comparação dos métodos tradicionais com o método apresentado neste trabalho para correção de fator de potência e redução de conteúdos harmônicos da corrente de entrada do conjunto para aplicações monofásicas com níveis mais elevados de potência.

Isto posto, acredita-se que o RHM apresentado neste trabalho é uma opção para contornar o problema de limitação de potência encontrado nos conversores PFC para sistemas monofásicos de alimentação, tanto nas suas versões tradicionais quanto nas modificadas.

# **Capítulo 3**

## **Operação do Retificador Híbrido Monofásico Proposto**

### **3.1 Introdução Geral**

Neste capítulo serão apresentadas as etapas de operação e a estratégia de controle do retificador híbrido monofásico proposto. Serão descritos detalhadamente as características de cada etapa de operação, destacando os instantes em que ocorrem e a parcela de contribuição de corrente de cada grupo de retificador.

A estratégia de controle adotada visa obter uma corrente CA de entrada com baixos níveis de DHT e elevado o fator de potência, garantindo ainda um elevado rendimento e robustez do conjunto. Será apresentado o diagrama de blocos do controle, com a descrição dos sinais envolvidos e os detalhes da sua implementação digital utilizando DSP.

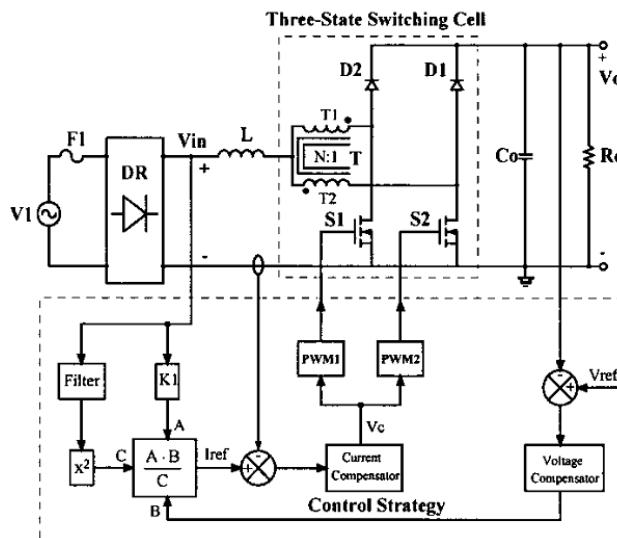

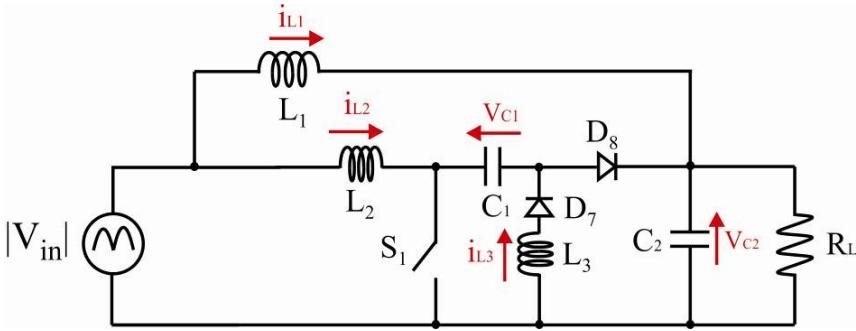

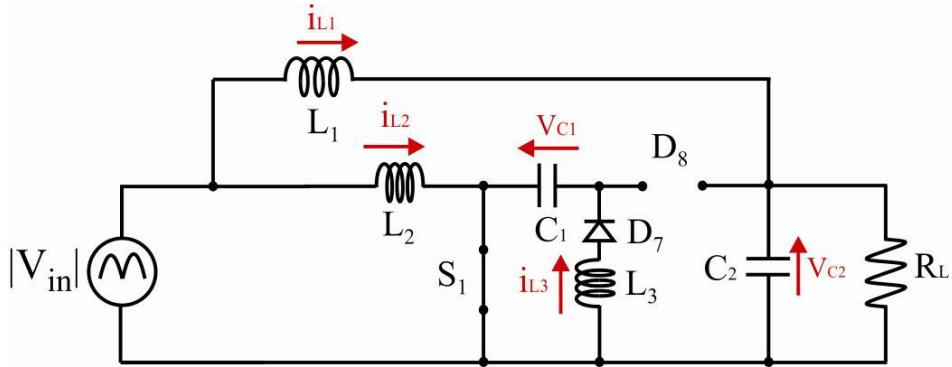

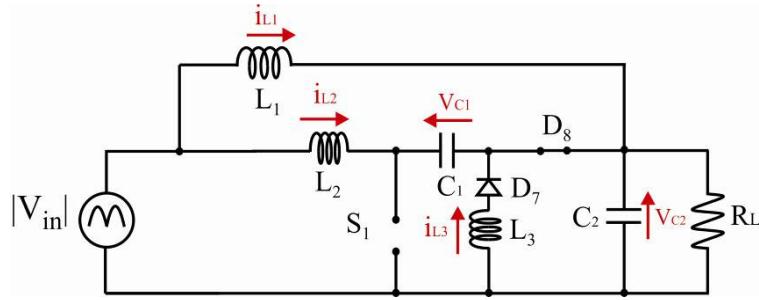

### **3.2 Operação do Retificador Híbrido Monofásico**

O retificador híbrido monofásico proposto é composto por um retificador monofásico não controlado (Ret-1), associado em paralelo com um conversor monofásico chaveado (Ret-2), como ilustrado na Fig. 3.1. Destaca-se que as principais vantagens de se utilizar retificadores híbridos como estágio pré-regulador com correção do fator de potência para conexão de conversores eletrônicos são:

- Maior rendimento global da estrutura, uma vez que os conversores chaveados processam reduzida parcela de potência ativa entregue à carga;

- Menor custo, quando comparado com conversores pré-reguladores chaveados convencionais com FP unitário, uma vez que os dispositivos semicondutores utilizados nessas estruturas são dimensionados para potência nominal;

- Flexibilidade quanto aos limites impostos pelas normas IEC610003-2 e IEC610003-4, uma vez que a corrente imposta na rede CA de alimentação pode assumir diferentes formas, dependendo da DHT<sub>I</sub> desejada;

- Técnica de controle simples, de baixo custo e eficiente.

Conforme ilustrado na Fig. 3.1, a corrente drenada da rede ( $i_{in}$ ) será a composição daquela requerida pelo retificador não controlado ( $i_{L1}$ ), com a parcela do conversor chaveado ( $i_{L2}$ ), sendo que a forma de onda da corrente  $i_{L2}$  é diretamente responsável pela característica final da forma de onda da corrente CA drenada da fonte de alimentação.

**Fig. 3.1 – Arranjo topológico do retificador híbrido monofásico**

Desta forma, resultam desta combinação na corrente de linha, as correntes  $i_{L1}$  e  $i_{L2}$ , sendo que  $i_{L1}$  é a corrente clássica dos retificadores monofásicos não controlados de onda completa, operando no modo descontínuo de condução, enquanto que a corrente  $i_{L2}$  é aquela imposta de acordo com a referência senoidal desejada. Portanto, tem-se que a composição das correntes  $i_{L1}$  e  $i_{L2}$  ( $i_{L1}$  somada a  $i_{L2}$ ), assume a forma aproximadamente senoidal ( $i_{in}$ ), se assim for desejado, conforme referência exemplo da Fig. 3.2.

**Fig. 3.2 – Formas de onda teóricas de corrente  $i_{L1}$ ,  $i_{L2}$ ,  $i_{in}$ . A forma de onda tracejada representa a tensão de entrada ( $v_{in}$ ) e a  $v_{C2}$  é a tensão de saída.**

### 3.2.1 Etapas de Operação

São identificadas 5 etapas de operação no funcionamento do RHM, ilustradas na Fig. 3.2. Os intervalos são divididos conforme a parcela de contribuição de cada grupo de retificador, na qual a forma de onda final da corrente é determinada pelo retificador não controlado, pelo conversor chaveado ou pela combinação de ambos.

As etapas descritas são:

**De 0 a  $t_1$ ,** os diodos da ponte retificadora do retificador não controlado estão polarizados reversamente, isto é, a tensão no barramento CC é maior que a tensão de entrada. Desta forma, inicia-se a imposição de corrente no indutor  $L_2$  do conversor chaveado, seguindo a referência senoidal de corrente. Portanto, neste intervalo de tempo, o retificador não controlado está fora de operação;

**De  $t_1$  a  $t_2$ ,** a tensão de entrada ( $v_{in}$ ) é maior que a tensão de saída ( $v_{C2}$ ) e, portanto, os diodos da ponte retificadora do retificador não controlado entram em condução e a corrente  $i_{L1}$  começa a crescer pela ação de  $v_{in}$ . Neste instante, o retificador não controlado começa a contribuir com a potência entregue à carga e, portanto, a

contribuição do conversor chaveado começa a diminuir. A corrente imposta no conversor chaveado ( $i_{L2}$ ) começa a decrescer, respeitando a referência senoidal de corrente, chegando a zero em t2;

**De t2 a t3**, apenas o retificador não controlado fornece potência à carga, pois a diferença entre a referência senoidal de corrente e o sinal realimentado é zero, desabilitando o conversor chaveado. Portanto, neste intervalo de tempo, a corrente de entrada é igual à corrente no indutor  $L_1$  do retificador não controlado;

Neste momento cabe ressaltar que, conforme descrito no Capítulo 2, se o conversor Boost fosse utilizado para compor o retificador híbrido seria impossível impor corrente entre os intervalos t1 e t3, visto que a tensão de saída ser menor que a tensão de entrada.

**De t3 a t4**, o conversor chaveado entra novamente em operação seguindo a referência de corrente senoidal imposta. A corrente  $i_{L1}$  chega a zero em t4 uma vez que a tensão  $v_{C2}$  fica maior que a tensão de entrada, retirando o retificador não controlado de operação;

**De t4 a  $\pi$** , apenas o conversor chaveado fornece potência à carga, pois os diodos da ponte retificadora do retificador não controlado foram bloqueados pela tensão de saída  $v_{C2}$ . Portanto, neste intervalo de tempo, a corrente de entrada é igual à corrente  $i_{L2}$ .

Desta forma, observa-se que a forma de onda da corrente  $i_{L2}$  é diretamente responsável pela característica final da forma de onda da corrente CA de alimentação, promovendo, portanto, uma sensível redução de sua TDH<sub>I</sub>. Destaca-se que, apesar de  $i_{in}$  ser uma forma de onda atípica, seu espectro harmônico apresenta níveis harmônicos adequados, tomado, indicativamente, como referência as normas internacionais IEC61000-3-2 e IEC61000-3-4, dependendo do nível de potência adotado, conforme comprovação experimental apresentada no Capítulo 5.

### 3.3 Projeto do Retificador Não Controlado (Ret-1)

Considerando o capacitor de saída infinito, a tensão na carga é constante e pode ser escrita como  $V_o$ .

Assim, a expressão da tensão no indutor  $L_1$  pode ser escrita como:

$$L_1 \frac{di_{L1}(t)}{dt} = V_p \sin(\omega t) - V_o \quad (3.1)$$

Onda  $V_p$  é a tensão de pico da senóide de entrada.

A corrente no indutor  $L_1$  pode ser obtida através da integral de (3.1):

$$i_{L1}(t) = \frac{1}{L_1} \int_{t_1}^t (V_p \sin(\omega t) - V_o) dt \quad (3.2)$$

$$i_{L1}(t) = \left( \frac{-1}{L_1} \right) \cdot \left\{ \frac{V_p [\cos(\omega t) - \cos(\omega t_1)]}{\omega} - V_o (t - t_1) \right\} \quad (3.3)$$

Onde  $t_1$  é o instante em que a tensão de saída se iguala à tensão de entrada, polarizando diretamente os diodos da ponte retificadora e fazendo a corrente  $i_{L1}$  crescer.

Seu valor pode ser determinado por:

$$t_1 = \frac{\sin^{-1} \left( \frac{V_o}{V_p} \right)}{\omega} \quad (3.4)$$

A expressão da corrente  $i_{L1}$  representada em (3.2) é válida somente no intervalo de  $t_1$  a  $t_4$ , onde  $t_4$  é o instante em que a corrente  $i_{L1}$  se iguala a zero.

O valor de  $t_4$  pode ser determinado igualando a Eq. (3.2) a zero, ou seja:

$$\frac{V_p [\cos(\omega t_4) - \cos(\omega t_1)]}{\omega} - V_o (t_4 - t_1) = 0 \quad (3.5)$$

A solução da Eq. (4) deve ser obtida por métodos numéricos. Dentro do intervalo de 0 a T (período de meio ciclo da tensão de entrada) obtém-se 2 soluções: uma delas coincide com o valor de  $t_1$ , obtido em (3.4). A segunda solução é o valor de  $t_4$ .

Dessa forma, a corrente  $i_{L1}$  pode ser escrita como:

$$\begin{cases} i_{L1}(t) = 0 & \text{se } 0 \leq t < t_1 \\ i_{L1}(t) = \left( \frac{-1}{L_1} \right) \cdot \left\{ \frac{V_p [\cos(\omega t) - \cos(\omega t_1)]}{\omega} - V_o(t - t_1) \right\} & \text{se } t_1 \leq t < t_4 \\ i_{L1}(t) = 0 & \text{se } t_4 \leq t < T \end{cases} \quad (3.6)$$

No intervalo de 0 a  $t_1$  a tensão de saída é maior que a tensão de entrada, bloqueando os diodos da ponte retificadora, resultando em uma corrente  $i_{L1}$  nula. A partir do instante  $t_1$  até o instante  $t_4$ , a tensão de entrada ( $v_{in}$ ) é maior que a tensão de saída ( $v_{C2}$ ) e a corrente no indutor  $L_1$  se comporta de acordo a Eq. (3.2). No instante  $t_4$  a corrente  $i_{L1}$  se iguala a zero, permanecendo nula enquanto a tensão de entrada for menor que a tensão de saída, repetindo o ciclo.

O valor médio da corrente  $i_{L1}$  pode ser obtido integrando as equações de cada intervalo de (3.6). Assim:

$$i_{L1avg} = \left( \frac{1}{T} \right) \left[ \int_0^{t_1} i_{L1}(t) dt + \int_{t_1}^{t_4} i_{L1}(t) dt + \int_{t_4}^T i_{L1}(t) dt \right] \quad (3.7)$$

$$i_{L1avg} = \left( \frac{1}{T} \right) \left[ 0 + \int_{t_1}^{t_4} i_{L1}(t) dt + 0 \right] \quad (3.8)$$

Substituindo (3.2) em (3.8) tem-se:

$$i_{L1avg} = \left( \frac{1}{T} \right) \int_{t_1}^{t_4} \left\{ \left( \frac{-1}{L_1} \right) \cdot \left[ \frac{V_p [\cos(\omega t) - \cos(\omega t_1)]}{\omega} - V_o(t - t_1) \right] \right\} dt \quad (3.9)$$

Integrando (3.9) obtém-se o valor da corrente média no indutor  $L_1$ :

$$i_{L1avg} = \left( \frac{-1}{L_1 \cdot T} \right) \left[ \frac{V_p (\sin \omega t_4 - \sin \omega t_1)}{\omega^2} + \frac{V_p \cos \omega t_1 (t_1 - t_4)}{\omega} + \frac{V_o t_4^2}{2} + \frac{V_o t_1^2}{2} - V_o t_1 t_4 \right] \quad (3.10)$$

A potência média processada pelo retificador não controlado pode ser expressa como:

$$P_{Ret1} = i_{L1avg} \cdot V_o \quad (3.11)$$

Substituindo (3.10) em (3.11) é obtida a expressão da potência média processada pelo retificador não controlado em função do valor de pico da tensão de entrada, do valor médio da tensão de saída e do indutor de filtro  $L_1$ .

$$P_{Ret1} = \left( \frac{-V_o}{L_1 \cdot T} \right) \left[ \frac{V_p (\sin \omega t_4 - \sin \omega t_1)}{\omega^2} + \frac{V_p \cos \omega t_1 (t_1 - t_4)}{\omega} + \frac{V_o t_4^2}{2} + \frac{V_o t_1^2}{2} - V_o t_1 t_4 \right] \quad (3.12)$$

O valor da indutância  $L_1$  pode ser calculado através da Eq. 3.13, obtida através da Eq. 3.12. Dessa forma obtém-se uma equação que determina o valor da indutância  $L_1$  em função do valor de pico da tensão de entrada ( $V_p$ ), do valor médio da tensão de saída ( $V_o$ ), da potência média processada pelo retificador não controlado ( $P_{Ret1}$ ) e dos instantes  $t_1$  e  $t_4$ , calculados através das Eq. 3.4 e 3.5, respectivamente.

$$L_1 = \left( \frac{-V_o}{P_{Ret1} \cdot T} \right) \left[ \frac{V_p (\sin \omega t_4 - \sin \omega t_1)}{\omega^2} + \frac{V_p \cos \omega t_1 (t_1 - t_4)}{\omega} + \frac{V_o t_4^2}{2} + \frac{V_o t_1^2}{2} - V_o t_1 t_4 \right] \quad (3.13)$$

O capacitor de saída  $C_2$  pode ser calculado através da Eq. 3.14.

$$C_2 = \left( \frac{P_{out}}{4 \cdot V_o \cdot \Delta V_o \cdot f} \right) \quad (3.14)$$

Onde:

$P_{out}$  – potência total de saída.

$V_o$  – tensão média de saída.

$\Delta V_o$  – *ripple* da tensão de saída.

f – frequência da tensão senoidal retificada de entrada.

$\omega$  – velocidade angular da tensão senoidal retificada de entrada.

A Tab. 3.1 trás as especificações para o dimensionamento do retificador não controlado utilizado nos protótipos de 1 kW e 10 kW.

**Tab. 3.1 – Especificação de projeto do retificador não controlado (Ret-1)**

| Parâmetros                             | Símbolo         | Protótipo 1 kW | Protótipo 10kW |

|----------------------------------------|-----------------|----------------|----------------|

| Tensão de pico de entrada              | $V_p$           | 311 V          | 311 V          |

| Tensão média de saída                  | $V_o$           | 250 V          | 250 V          |

| Potência média do Ret-1                | $P_{ret1}$      | 0.6 kW         | 6 kW           |

| Ondulação da tensão no capacitor $C_2$ | $\Delta V_{C2}$ | 15             | 150            |

### 3.3.1 Dimensionamento Retificador Não Controlado do Protótipo de 1 kW

#### 3.3.1.1 Cálculo do Indutor $L_1$

Para se obter o valor do indutor  $L_1$  pode ser obtido através da Eq. 3.13 é necessário o cálculo dos instantes  $t_1$  e  $t_4$ , obtidos através da Eq. 3.4 e 3.5, respectivamente. Assim

$$t_1 = \frac{\sin^{-1}\left(\frac{V_o}{V_p}\right)}{\omega} = 2,5 \text{ ms} \quad (3.15)$$

Através da solução numérica da Eq. 3.5 obtém-se o instante  $t_4$ .

$$t_4 = 7,6 \text{ ms} \quad (3.16)$$

Dessa forma:

$$L_1 = \left( \frac{-V_o}{P_{ret1} \cdot T} \right) \left[ \frac{V_p (\sin \alpha_4 - \sin \alpha_1)}{\alpha^2} + \frac{V_p \cos \alpha_1 (t_1 - t_4)}{\omega} + \frac{V_o t_4^2}{2} + \frac{V_o t_1^2}{2} - V_o t_1 t_4 \right] = 19,7 \text{ mH} \quad (3.17)$$

### 3.3.1.2 Cálculo do Capacitor C2

O valor do capacitor de saída C2 pode ser obtido através da Eq. 3.14.

$$C_2 = \left( \frac{P_{out}}{4 \cdot V_o \cdot \Delta V_o \cdot f} \right) = 555 \mu\text{F} \quad (3.18)$$

## 3.3.2 Dimensionamento Retificador não Controlado do Protótipo de 10 kW

### 3.3.2.1 Cálculo do indutor L1

De maneira análoga ao dimensionamento do indutor L1 do protótipo de 1 kW, obtém-se os instantes t1 e t4 para o protótipo de 10 kW através da Eq. 3.4 e 3.5, respectivamente. Dessa forma:

$$t_1 = \frac{\sin^{-1} \left( \frac{V_o}{V_p} \right)}{\omega} = 2,3 \text{ ms} \quad (3.19)$$

Através da solução numérica da Eq. 3.5 obtém-se o instante t4.

$$t_4 = 7,9 \text{ ms} \quad (3.20)$$

Dessa forma:

$$L_1 = \left( \frac{-V_o}{P_{Ret1} \cdot T} \right) \left[ \frac{V_p (\sin \alpha_4 - \sin \alpha_1)}{\omega^2} + \frac{V_p \cos \alpha_1 (t_1 - t_4)}{\omega} + \frac{V_o t_4^2}{2} + \frac{V_o t_1^2}{2} - V_o t_1 t_4 \right] = 2,65 \text{ mH} \quad (3.21)$$

### 3.3.2.2 Cálculo do Capacitor C2

O valor do capacitor de saída C2 do protótipo de 10 kW pode ser obtido através da Eq. 3.14.

$$C_2 = \left( \frac{P_{out}}{4 \cdot V_o \cdot \Delta V_o \cdot f} \right) = 555 \mu\text{F} \quad (3.22)$$

### 3.4 Projeto do Conversor Chaveado (Ret-2)

O conversor SEPIC utilizado nesta aplicação é ilustrado na Fig. 3.3.

**Fig. 3.3 – Conversor SEPIC.**

Suas especificações de projeto são apresentadas na Tab. 3.2.

**Tab. 3.2 – Especificações do Conversor SEPIC.**

| Parâmetros                             | Símbolo         | Protótipo 1kW | Protótipo 10 kW |

|----------------------------------------|-----------------|---------------|-----------------|

| Tensão máxima na entrada               | $V_{imax}$      | 311 V         | 311 V           |

| Tensão mínima na entrada               | $V_{imin}$      | 300 V         | 300 V           |

| Potência de Saída                      | $P_o$           | 0.4 kW        | 4 kW            |

| Tensão na média de saída               | $V_o$           | 250 V         | 250 V           |

| Contribuição da corrente na saída      | $I_o$           | 1.6 A         | 16 A            |

| Ondulação da corrente no Indutor $L_2$ | $\Delta I_{L2}$ | 1 A           | 6 A             |

| Ondulação da corrente no Indutor $L_3$ | $\Delta I_{L3}$ | 1 A           | 6 A             |

| Ondulação da tensão no capacitor $C_1$ | $\Delta V_{C1}$ | 4 V           | 20 V            |

| Freqüência de chaveamento              | $f_s$           | 25 kHz        | 25 kHz          |

#### 3.4.1 Dimensionamento do Protótipo de 1 kW

##### 3.4.1.1 Dimensionamento do Indutor $L_2$

A razão cíclica mínima e máxima podem ser determinada por:

$$\frac{D_{min}}{1 - D_{min}} = \frac{V_0}{V_{imax}} \quad (3.23)$$

$$D_{min} = 0,44 \quad (3.24)$$

$$\frac{D_{max}}{1 - D_{max}} = \frac{V_0}{V_{imin}} \quad (3.25)$$

$$D_{max} = 0,45 \quad (3.26)$$

Assim, o indutor  $L_2$  pode ser obtido por:

$$L_2 = \frac{V_{i\max}}{\Delta I_{L1}} D_{\min} T \cong 5,5 \text{ mH} \quad (3.27)$$

### 3.4.1.2 Dimensionamento do Indutor L<sub>3</sub>

Considerando a máxima tensão, o valor do indutor L<sub>3</sub> pode ser obtido por:

$$L_3 = \frac{V_o}{\Delta I_{L3}} (1 - D_{\min}) T \cong 5,5 \text{ mH} \quad (3.28)$$

### 3.4.1.3 Dimensionamento do Capacitor C<sub>1</sub>

Considerando a mínima tensão de entrada a tensão média no capacitor C<sub>1</sub> pode ser obtida por:

$$V_{C1md} = V_{i\min} = 300V \quad (3.29)$$

O valor do capacitor C<sub>1</sub> pode ser obtido por:

$$C_1 = \frac{I_{L3} D_{\max}}{0,2 V_{C1md} f_s} = 5,36 \mu F \quad (3.30)$$

## 3.4.2 Dimensionamento para Protótipo de 10 kW

### 3.4.2.1 Dimensionamento do Indutor L<sub>2</sub>

A razão cíclica mínima e máxima podem ser determinada por:

$$\frac{D_{\min}}{1 - D_{\min}} = \frac{V_0}{V_{i\max}} \quad (3.31)$$

$$D_{\min} = 0,41 \quad (3.32)$$

$$\frac{D_{\max}}{1 - D_{\max}} = \frac{V_0}{V_{i\min}} \quad (3.33)$$

$$D_{\max} = 0,42 \quad (3.34)$$

Assim, o indutor L<sub>2</sub> pode ser obtido por:

$$L_2 = \frac{V_{i\max}}{\Delta I_{L1}} D_{\min} T \cong 859 \mu H \quad (3.35)$$

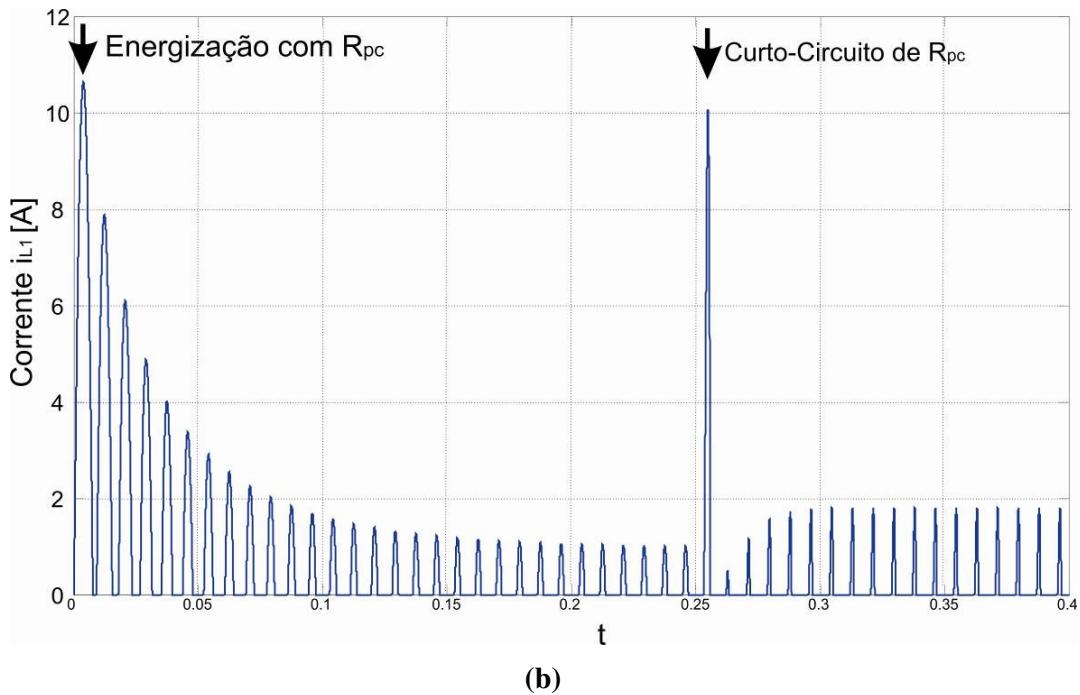

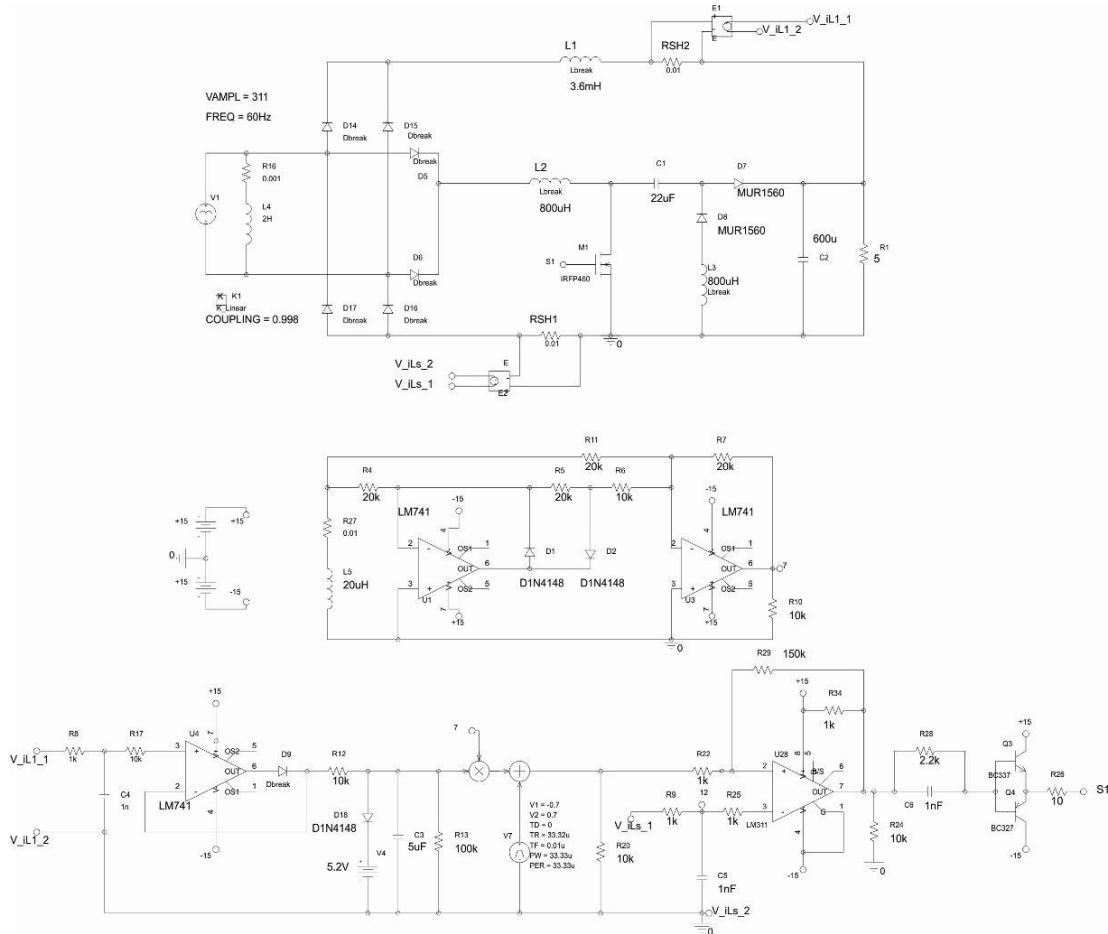

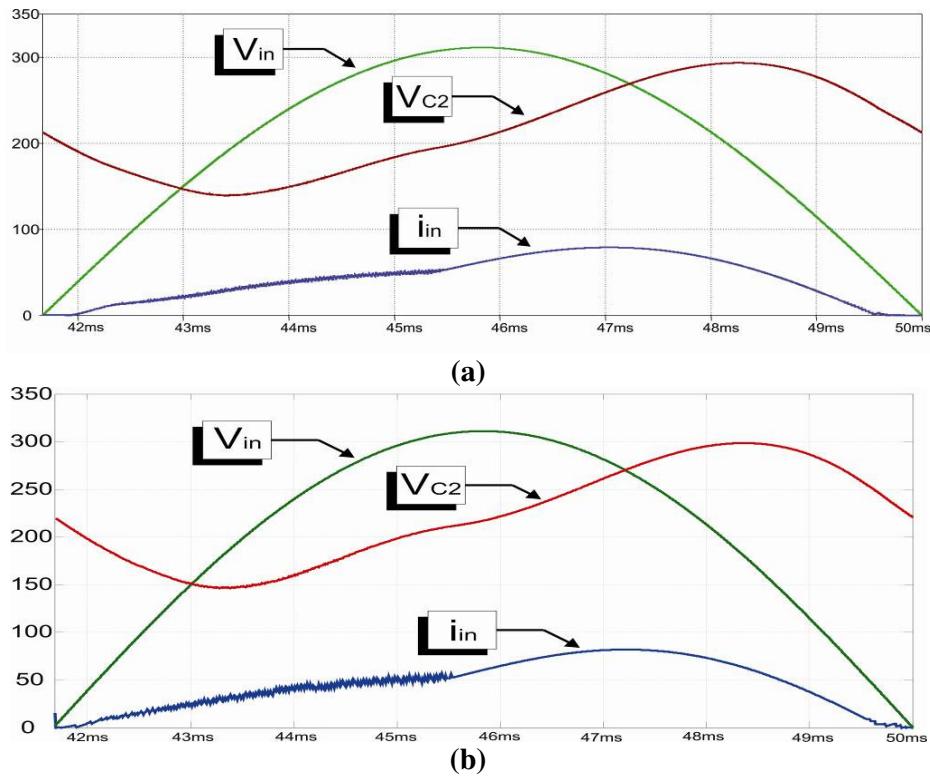

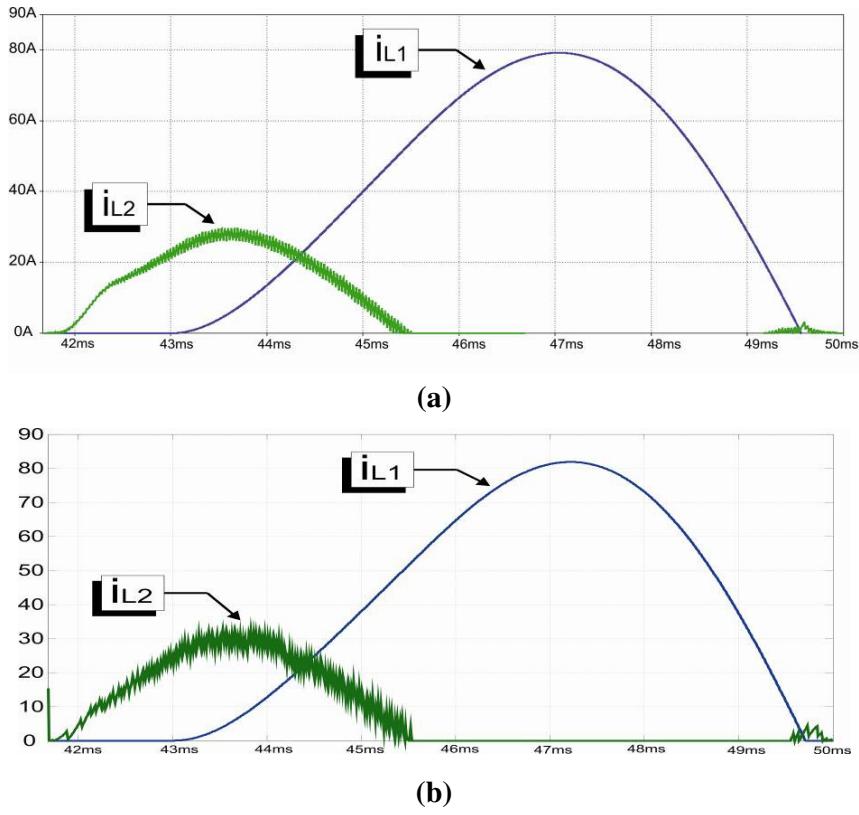

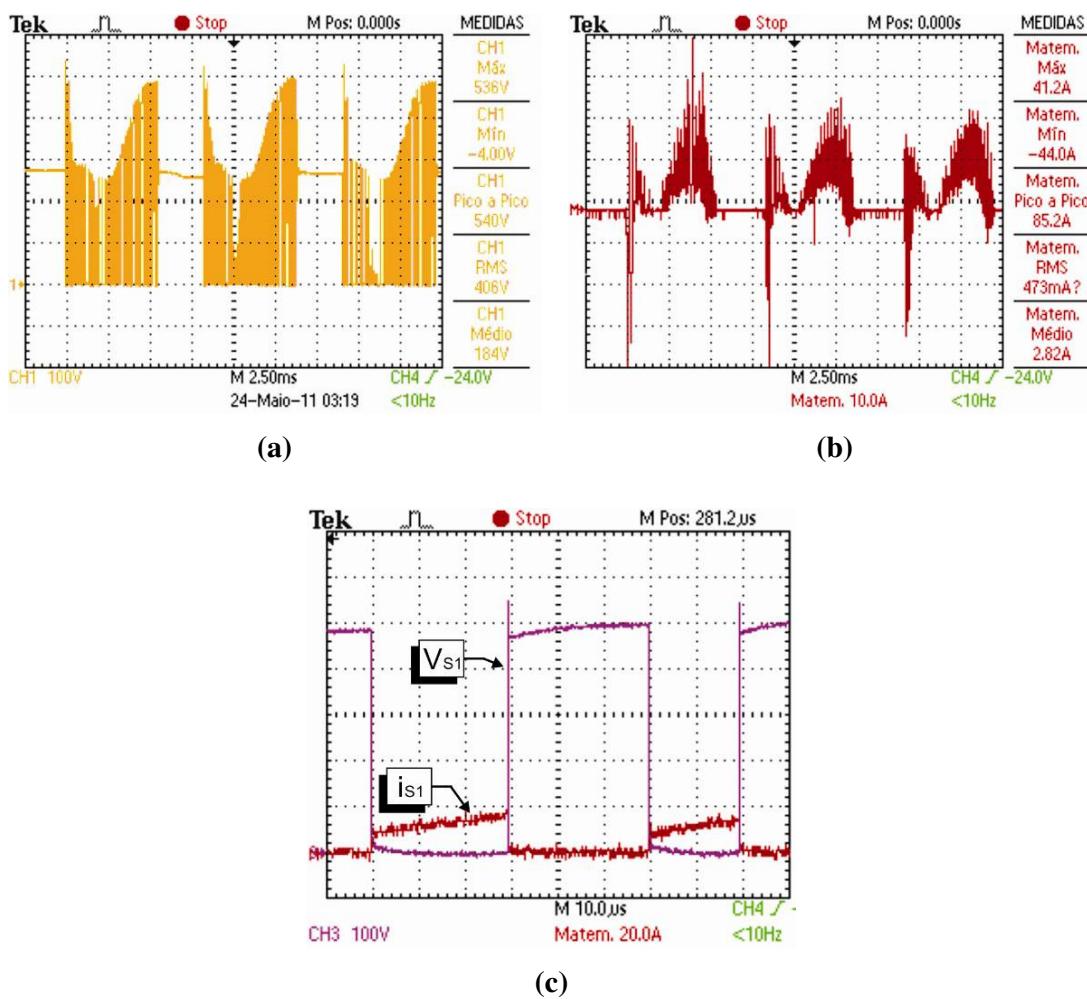

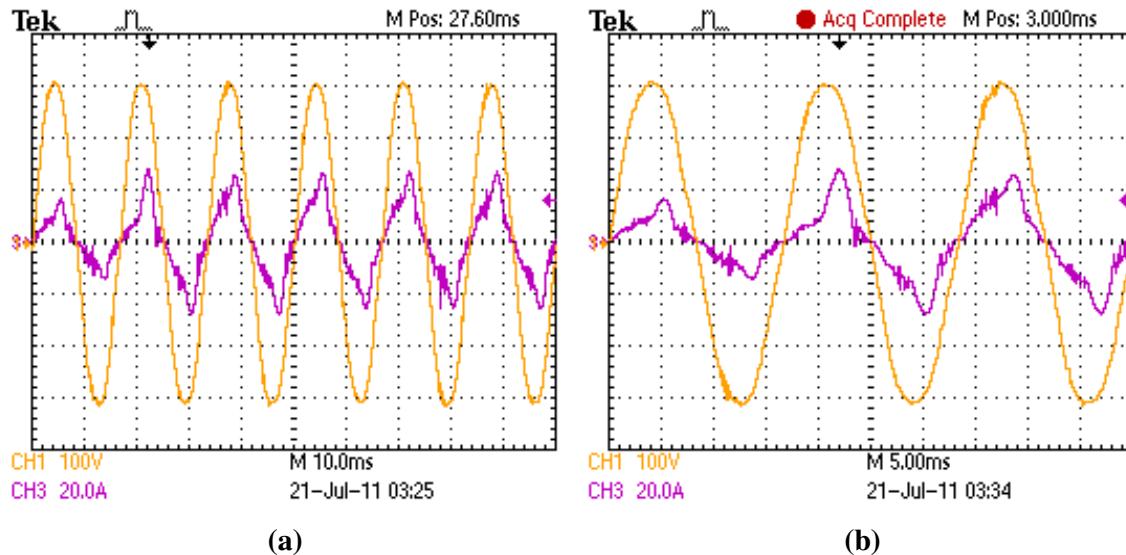

### 3.4.2.2 Dimensionamento do Indutor L<sub>3</sub>